05 ГС

со

Изобретение относится к электросвязи и может использоваться для асинхронного ввода-вывода синхронных двоичных сигналов в цифровые тракты систем с импульс- но-кодовой модуляцией, дельта-модуляцией и другими цифровыми методами модуляции.

Цель изобретения - повышение точности сопряжения цифровых последовательностей за счет учета влияния девиации частоты следования импульсов этих носле- :довательностей.

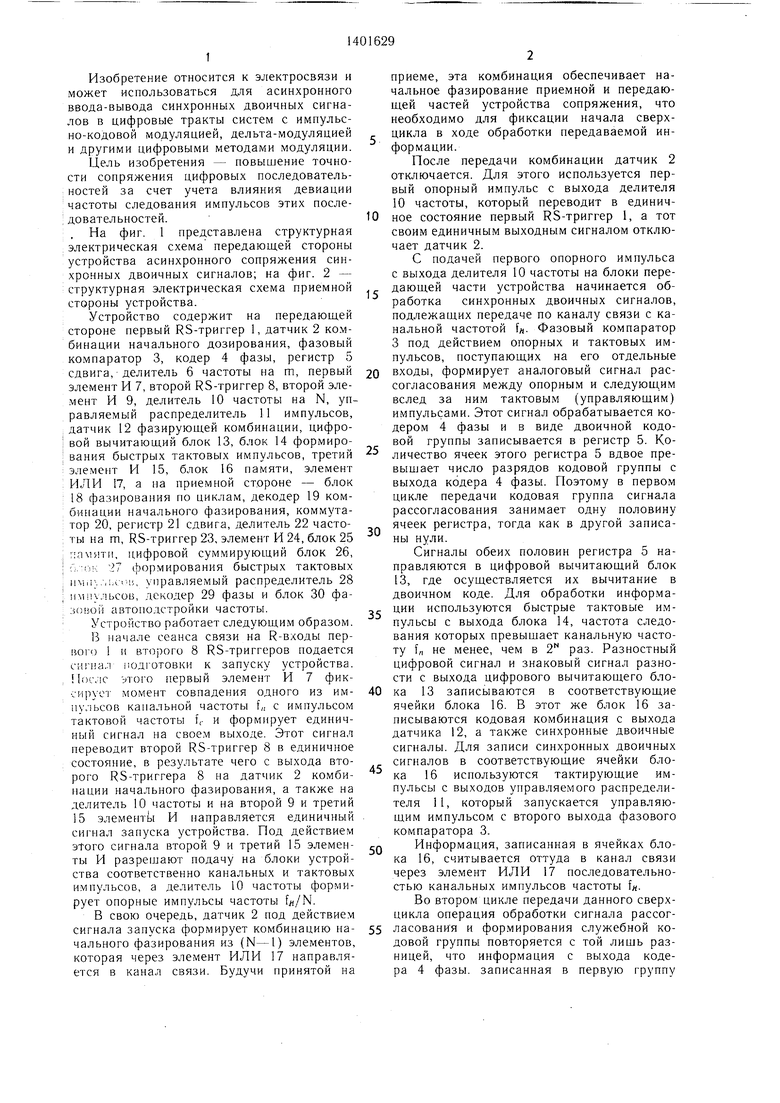

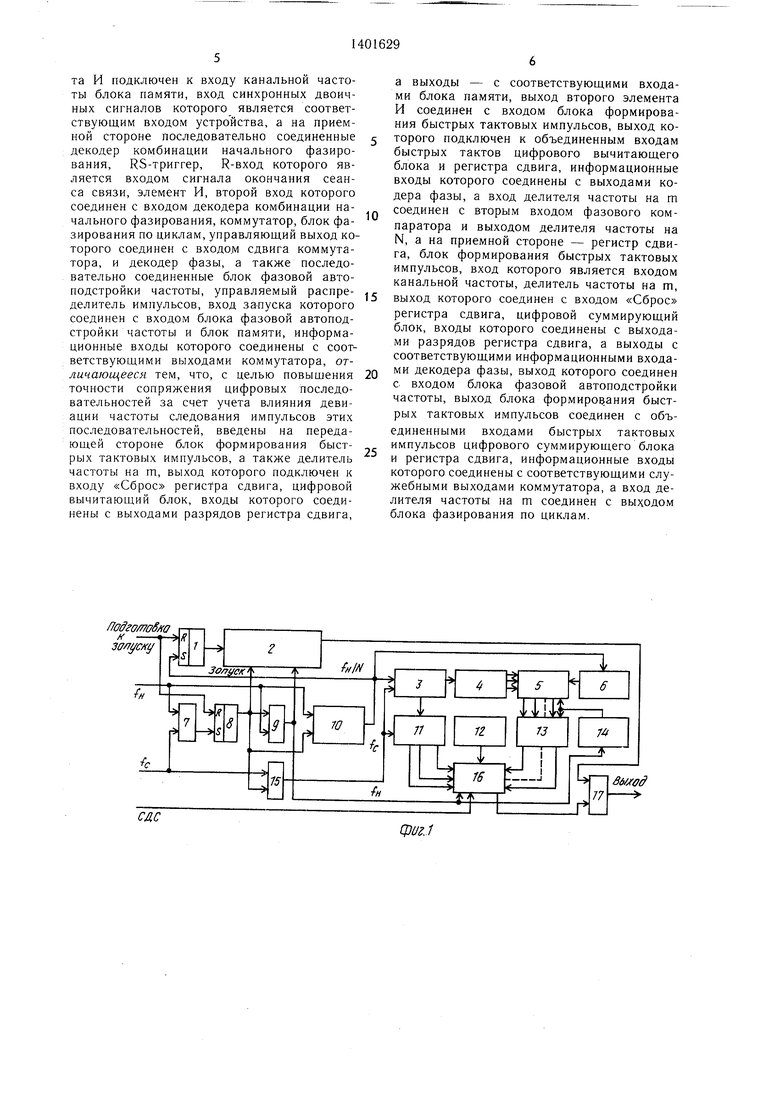

На фиг. 1 представлена структурная электрическая схема передающей стороны устройства асинхронного сопряжения синхронных двоичных сигналов; на фиг. 2 - структурная электрическая схема приемной стороны устройства.

Устройство содержит на передающей стороне первый RS-триггер 1, датчик 2 комбинации начального дозирования, фазовый компаратор 3, кодер 4 фазы, регистр 5 сдвига, делитель 6 частоты на т, первый элемент И 7, второй RS-триггер 8, второй элемент И 9, делитель 10 частоты на N, управляемый распределитель 11 импульсов, датчик 12 фазирующей комбинации, цифровой вычитающий блок 13, блок 14 формирования быстрых тактовых импульсов, третий элемент И 15, блок 16 памяти, элемент ИЛИ 17, а на приемной стороне - блок 18 фазирования по циклам, декодер 19 комбинации начального фазирования, коммутатор 20, регистр 21 сдвига, делитель 22 частоты на т, RS-триггер 23, элемент И 24, блок 25 п 1ят11, цифровой суммирующий блок 26, ;:.:;:. 27 формирования быстрых тактовых iiMii;,., 1л i4i, управляемый распределитель 28 импх.п.ьсов, декодер 29 фазы и блок 30 фазовой автоподстройки частоты.

Устройство работает следующим образом.

В начале сеанса связи на R-входы пер- 1Ю1) и второго 8 RS-триггеров подается .п 1 од1-отовки к запуску устройства. После этого первый элемент И 7 фиксирует момент совпадения одного из им- ny. ibcoB канальной частоты f,, с импульсом тактовой частоты f,- и формирует единичный сигнал на своем выходе. Этот сигнал переводит второй RS-триггер 8 в единичное состояние, в результате чего с выхода второго RS-триггера 8 на датчик 2 комбинации начального фазирования, а также на делитель 10 частоты и на второй 9 и третий 15 элементы И направляется единичный сигнал запуска устройства. Под действием этого сигнала второй 9 и третий 15 элементы И разрешают подачу на блоки устройства соответственно канальных и тактовых импульсов, а делитель 10 частоты формирует опорные импульсы частоты f/i/N.

В свою очередь, датчик 2 под действием сигнала запуска формирует комбинацию на- чального фазирования из (N-1) элементов, которая через элемент ИЛИ 17 направляется в канал связи. Будучи принятой на

5

0

0

0

5

0

5

5

0

приеме, эта комбинация обеспечивает начальное фазирование приемной и передающей частей устройства сопряжения, что необходимо для фиксации начала сверхцикла в ходе обработки передаваемой информации.

После передачи комбинации датчик 2 отключается. Для этого используется первый опорный импульс с выхода делителя 10 частоты, который переводит в единичное состояние первый RS-триггер 1, а тот своим единичным выходным сигналом отключает датчик 2.

С подачей первого опорного импульса с выхода делителя 10 частоты на блоки передающей части устройства начинается обработка синхронных двоичных сигналов, подлежащих передаче по каналу связи с канальной частотой д. Фазовый компаратор 3 под действием опорных и тактовых импульсов, поступающих на его отдельные входы, формирует аналоговый сигнал рассогласования между опорным и следующим вслед за ним тактовым (управляющим) импульсами. Этот сигнал обрабатывается кодером 4 фазы и в виде двоичной кодовой группы записывается в регистр 5. Количество ячеек этого регистра 5 вдвое превышает число разрядов кодовой группы с выхода кодера 4 фазы. Поэтому в первом цикле передачи кодовая группа сигнала рассогласования занимает одну половину ячеек регистра, тогда как в другой записаны нули.

Сигналы обеих половин регистра 5 направляются в цифровой вычитающий блок 13, где осуществляется их вычитание в двоичном коде. Для обработки информации используются быстрые тактовые импульсы с выхода блока 14, частота следования которых превышает канальную частоту In не менее, чем в 2 раз. Разностный цифровой сигнал и знаковый сигнал разности с выхода цифрового вычитающего блока 13 записываются в соответствующие ячейки блока 16. В этот же блок 16 записываются кодовая комбинация с выхода датчика 12, а также синхронные двоичные сигналы. Для записи синхронных двоичных сигналов в соответствующие ячейки блока 16 используются тактирующие импульсы с выходов управляемого распределителя И, который запускается управляющим импульсом с второго выхода фазового компаратора 3.

Информация, записанная в ячейках блока 16, считывается оттуда в канал связи через элемент ИЛИ 17 последовательностью канальных импульсов частоты f«.

Во втором цикле передачи данного сверхцикла операция обработки сигнала рассогласования и формирования служебной кодовой группы повторяется с той лишь разницей, что информация с выхода кодера 4 фазы, записанная в первую группу

ячеек регистра 5 в первом цикле передачи, переписывается в его вторую группу, а на ее место записывается информация второго цикла передачи. Сравнение блоком 13 этих кодовых групп позволяет ему сформировать во втором цикле передачи кодовую комбинацию разностного сигнала рассогласования.

В третьем цикле передачи первая группа ячеек регистра 5 отводится под информацию о рассогласовании сопрягаемых последовательностей в этом цикле, тогда как вторая группа ячеек - под информацию второго цикла передачи и т.д., т.е. от цикла передачи к циклу информация одной половины регистра 5 переписывается во вторую половину и стирается только в следующем цикле. В последнем (гп-м) цикле передачи данного сверхцикла после обработки быстрыми тактовыми импульсами информации, записанной в регистре 5, все ячейки последнего обнуляются сигналом с выхода делителя частоты 6, следующим с частотой IL ,

mN

Из канала связи цифровая информация поступает на вход приемной части устройства сопряжения. В начале сеанса связи декодер 19 принимает и обрабатывает соответствующую кодовую группу и формирует на своем выходе единичный сигнал, который переводит RS-триггер 23 в единиц- ное состояние, сохраняющееся до конца сеанса. Единичный выходной сигнал с выхода RS-триггера 23 открывает элемент И 24 для прохождения информации из канала связи на коммутатор 20. В частности, на коммутатор 20 поступает фазирующий импульс, следующий непосредственно за комбинацией начального фазирования, т.е. на N-й позиции цикла передачи. Он направляется в блок 18, управляющий выход которого соединен со сдвигающим входом коммутатора 20. Благодаря сигналам на этом входе гарантируется появление на i-м выходе коммутатора 20 именно i-ro импульса в пределах цикла передачи.

Информационные выходы коммутатора 20, с первого по (п+О-й, подключены к соответствующим входам блока 25. Служебные выходы коммутатора 20, с (п+2)-го по (N-1)-и.подключены к входам регистра 21. Запись служебных сигналов в регистр 21 осуществляется на частоте быстрых тактовых импульсов, поступающих из блока 27. Последний выполнен аналогично одноименному блоку 14, входящему в состав передающей части устройства сопряжения. Служебная кодовая группа направляется из ячеек регистра 21 в цифровой суммирующий блок 26, где с учетом знакового раз- ряда определяется кодовая группа фазового рассогласования соответствующего цикла передачи.

0

5 0

0

Обработка информации в цифровом суммирующем блоке 26 также осуществляется на частоте быстрых тактовых импульсов.

Сигналы с выхода цифрового суммирующего блока 26 направляются в декодер 29 фазы, который восстанавливает временное положение управляюн его импульса для данного цикла передачи. Этот импульс используется для регенерации тактовой частоты в блоке 30 фазовой автоподстройки частоты. Восстановленной тактовой частотой f,- с выхода блока 30 тактируется управляемый распределитель 28 импульсов. Под действием импульсов, следующих с восстановленной тактовой частотой f, на выходах управляемого распределителя 28 синхронные двоичные сигналы из ячеек блока 25 считываются в абонентскую линию потребителю информации.

После окончания обработки служебной информации в последнем (т-м) цикле передачи данного сверхцикла регистр 21 обнуляется импульсами частоты -т,-, поступающими с выхода делителя 22 частоты.

Формула изобретения

Устройство асинхронного сопряжения синхронных двоичных сигналов, содержащее на передающей стороне кодер фазы, регистр сдвига, датчик фазирующей комбинации, делитель частоты на N, первый RS-триггер, ,последовательно соединенные первый элемент И, второй RS-триггер, второй элемент И, датчик комбинации начального фазирования и элемент ИЛИ, а также последовательно соединенные третий элемент И, фазовый компаратор, управляемый распределитель импульсов, управляющий вход которого соединен с первым входом фазового компаратора, и блок памяти, в.ход записи кодовой комбинации которого подключен к выходу датчика фазирующей комбинации, при этом R-входы первого и второго RS-триггеров объединены между собой, а S-вход первого RS-триггера соединен с выходом делителя частоты на .N, первый вход которого является входом канальной частоты устройства и соединен с вторым входом второго элемента И и первым входом первого элемента И, второй вход которого является входом тактовой частоты устрой- , ства и соединен с первым входом третьего элемента И. второй вход которого соединен с вторым входом делителя частоты на N, первым входом второго элемента И и запускающим входом датчика комбинации начального фаз}1рования. вход «Сброс которого соединен с выходом первого RS- триггера, второй выход фазового компаратора соединен с входом кодера фазы, второй вход элемента ИЛИ подключен к выходу блока памяти, выход второго элемеи

та И подключен к входу канальной частоты блока памяти, вход синхронных двоичных сигналов которого является соответствующим входом устройства, а на приемной стороне последовательно соединенные декодер комбинации начального фазирования, RS-триггер, R-вход которого является входом сигнала окончания сеанса связи, элемент И, второй вход которого соединен с входом декодера комбинации начального фазирования, коммутатор, блок фазирования по циклам, управляющий выход которого соединен с входом сдвига коммутатора, и декодер фазы, а также последовательно соединенные блок фазовой автоподстройки частоты, управляемый распре- делитель импульсов, вход за-пуска которого соединен с входом блока фазовой автоподстройки частоты и блок памяти, информационные входы которого соединены с соответствующими выходами коммутатора, отличающееся тем, что, с целью повыщения точности сопряжения цифровых последовательностей за счет учета влияния девиации частоты следования импульсов этих последовательностей, введены на передающей стороне блок формирования быстрых тактовых импульсов, а также делитель частоты на ш, выход которого подключен к входу «Сброс регистра сдвига, цифровой вычитающий блок, входы которого соединены с выходами разрядов регистра сдвига.

0

0

а выходы - с соответствующими входами блока памяти, выход второго элемента И соединен с входом блока формирования быстрых тактовых импульсов, выход которого подключен к объединенным входам быстрых тактов цифрового вычитающего блока и регистра сдвига, информационные входы которого соединены с выходами кодера фазы, а вход делителя частоты на m соединен с вторым входом фазового компаратора и выходом делителя частоты на N, а на приемной стороне - регистр сдвига, блок формирования быстрых тактовых импульсов, вход которого является входом канальной частоты, делитель частоты на т, выход которого соединен с входом «Сброс регистра сдвига, цифровой суммирующий блок, входы которого соединены с выходами разрядов регистра сдвига, а выходы с соответствующими информационными входами декодера фазы, выход которого соединен с входом блока фазовой автоподстройки частоты, выход блока формирОЕ ания быстрых тактовых импульсов соединен с объединенными входами быстрых тактовых импульсов цифрового суммирующего блока и регистра сдвига, информационные входы которого соединены с соответствующими служебными выходами коммутатора, а вход делителя частоты на ш соединен с выходом блока фазирования по циклам.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1987 |

|

SU1649681A1 |

| Устройство асинхронного ввода-вывода синхронной информации | 1982 |

|

SU1053307A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1979 |

|

SU860326A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1982 |

|

SU1072278A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1974 |

|

SU510792A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1978 |

|

SU786024A1 |

| Устройство ввода-вывода синхронной двоичной информации в цифровые тракты | 1984 |

|

SU1374438A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение точности сопряжения цифровых последовательностей. Устр-во содержит передающую и приемную части. В начале сеанса связи обеспечивается начальное фазирование приемной и передающей частей устр-ва, что необходимо для фиксации начала сверхцикла в ходе обработки передаваемой информации. Затем по циклам начинается обработка синхронных двоичных сигналов, подлежащих передаче по каналу связи с канальной частотой. Из канала связи цифровая информация поступает на вход приемной части устр-ва, где осуществляется обработка информации на частоте «быстрых тактовых импульсов, и полученные синхронные двоичные сигналы считываются в абонентскую линию потребителю информации. Цель достигается за счет учета влияния девиации частоты следования импуль- сов цифровых последовательностей. 2 ил. §

Подга/по6/(о

3ff C/fi/

слс

36//off

фиг.1

Vx.

«Sj

I

VVkM

CN.

N

«« N

N

tXl

| Авторское свидетельство СССР № 1285608, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-06-07—Публикация

1986-10-08—Подача