(54) ИСТОЧНИК КАЛИБРОВАННЫХ НАПРЯЖЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Источник калиброванных напряжений | 1980 |

|

SU943672A1 |

| Источник калиброванных напряжений | 1980 |

|

SU907518A2 |

| Источник калиброванных напряжений | 1981 |

|

SU1029155A2 |

| Источник калиброванных напряжений | 1979 |

|

SU860025A2 |

| Источник калиброванных напряжений | 1980 |

|

SU877500A1 |

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

| Измерительный преобразователь напряжения | 1981 |

|

SU1075083A1 |

| Масштабный преобразователь напряжения и его варианты | 1980 |

|

SU922780A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU947958A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

1

Изобретение относится к электротехнике, в частности к источникам калиброванных напряжений.

По основному авт. св. № 758095 известен источник калиброванных напряжений, содержащий блок опорного напряжения, коммутатор, первый блок интегрирования, регистр 5 памяти, преобразователь кода во временной интервал и блок управления, причем выход блока опорного напряжения соединен с первым входом коммутатора, выход которого подключен ко входу первого блока интег- . рирования, вход регистра памяти соединен с входной клеммой, выход подключен ко входу преобразователя кода во временной ннтервал, а вход сигнализации регистра памяти соединен с соответствующим выходом блока управления, при этом выход пре- tS образователя кода во временной интервал через блок управления подключен к первому и второму управляющим входам коммутатора, а также преобразователь «код-напряжение, второй блок интегрирования и аналоговый сумматор, первый блок интегри- 2 рования дополнительно снабжен входом сброса, причем вход преобразователя «коднапряжение соединен с дополнительным

входом регистра памяти, выход данного преобразователя подключен к первому входу аналогового сумматора, выход первого блока интегрирования соединен со входом второго блока интегрирования, выход которого подключен ко второму входу аналогового сумматора, выходом соединенного с выходной клеммой и вторым входом коммутатора, а вход сброса первого блока интегрирования и вход управления второго блока интегрирования соединены с соответствующими выходами блока управления.

Выходное напряжение данного устройства достигает в течение п циклов установивщегося значения.

и pTi. рА

-вых.уа. у qгде Е - опорное напряжение;

Т - постоянный временной интервал;

Тх - временной интервал, пропорциональный входному коду N, Тх у-;

f - тактовая частота на входе пересчетного устройства, входящего в состав преобразователя кода во временной интервал, причем f Т q const 1.

Однако для заданной величины Тхтах разрешающая способность преобразователя кода во временной интервал и всего устройства в целом определяется допустимой величиной f. Последняя ограничивается возможностями формирующих схем и цифровых элементов, входящих в состав пересчетного устройства. Так, при разрешающей способности устройства Ш н мс необходимо обеспечить f 500 МГц, что не реализуется на интегральных элементах. В свою очередь уменьшение данной частоты сопряжено с увеличением длительности итерационного цикла и, следовательно, приводит к снижению быстродействия источника калиброванных напряжений.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в источник калиброванные напряжений введены источник опорного тока и ключ, причем выход источника опорного тока через ключ связан с дополнительным входом первого блока интегрирования, а дополнительный выход преобразователя кода во временной интервал через блок управления связан с управляющим входом ключа.

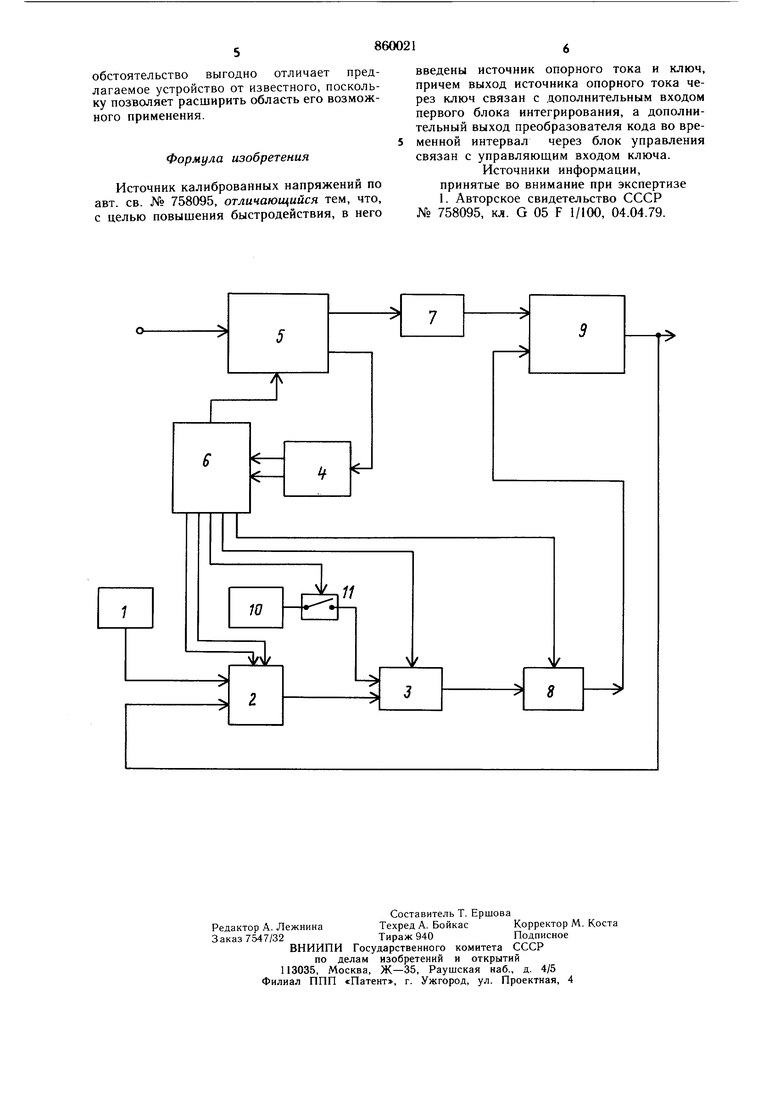

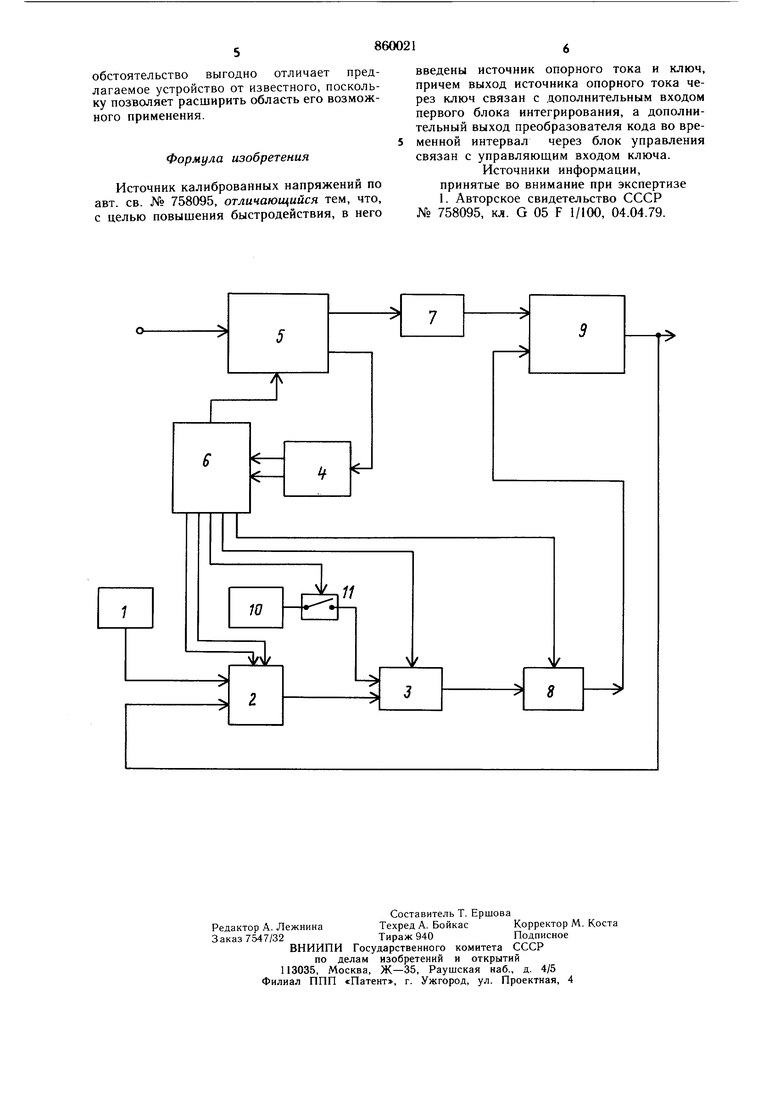

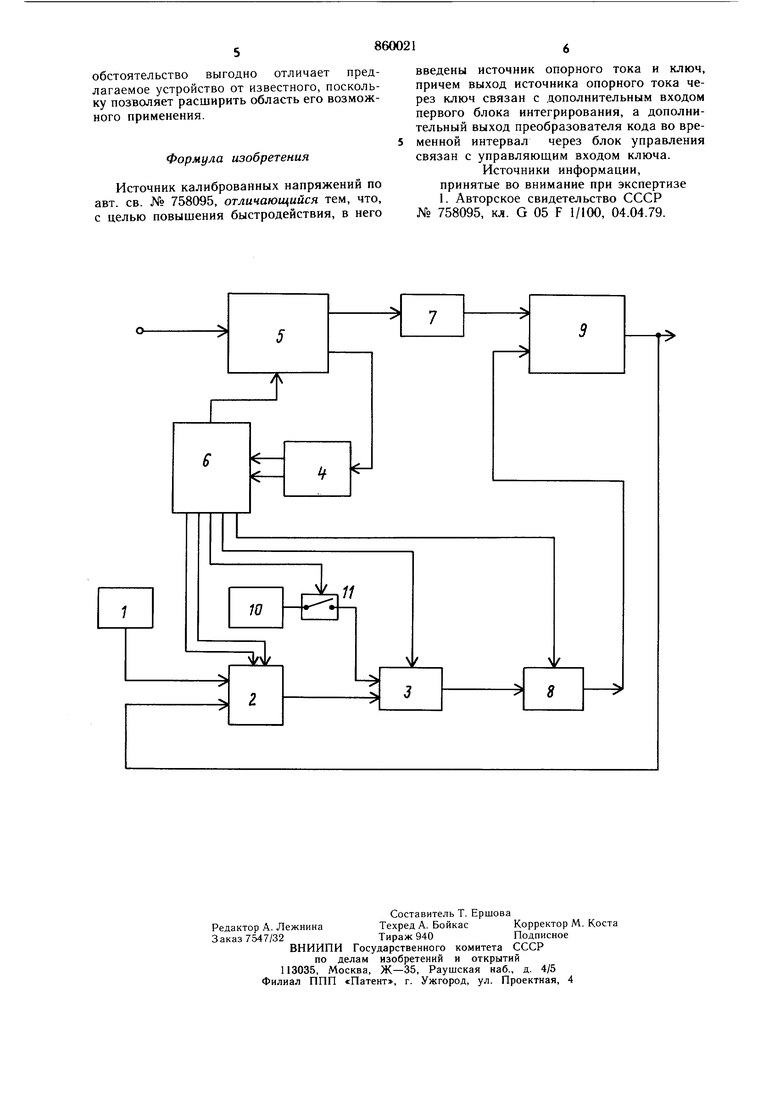

На чертеже представлена структурная схема предлагаемого устройства.

Источник калиброванных напряжений содержит блок 1 опорного напряжения, коммутатор 2, первый блок 3 интегрирования, преобразователь 4 кода во временной интервал, регистр 5 памяти, блок 6 управления, преобразователь 7 «код-напряжение, второй блок 8 интегрирования, аналоговый сумматор 9, источник 10 опорного тока и ключ И.

Устройство работает следующим образом.

По команде блока 6 управления входной код N переписывается в регистр 5, при этом на выходе преобразователя 7 «код-напряжение устанавливается пропорциональное данному коду напряжение EI, а выходное напряжение сумматора 9 определяется выражением

UBWX (t) - 4)iE,--)2Ua(t) (1)

где Ui (t) - напряжение на выходе блоке 8; ),Ог -коэффициенты передачи сумматора 9 по соответствующим входам.

Итерационный процесс установления выходного напряжения устройства осуществляется за п циклов. В начале очередного i-ro цикла блоком 6 производится сброс первого блока 3 интегрирования, по окончании сброса выход блока 1 опорного напряжения через коммутатор 2 подключается ко входу блока 3, и опорное напряжение Е интегрируется в течение интервала времени TXI . Этот интервал, пропорциональный числу NI, представляющему К старших разрядов S-разрядного кода N Ni -Ь с основанием Л, вырабатывается преобразователем 4 и через блок 6 подается на первый

управляющий вход коммутатора 2. Одновременно на дополнительном выходе преобразователя 4 формируется временной интервал Тха , длительность которого пропорциональна числу Na, представляющему S-K младших разрядов кода. Этот интервал через блок 6 подается на управляющий вход ключа 11, и в течение его выходной ток источника 10 I (1 + S), где R - масштабное сопротивление по основному входу блока 3, а 5 - относительное отклонение величины I от номинального значения, поступает на дополнительный вход блока 3 и интегрируется. По окончании данной части цикла, длительность которой составляет max(Txi, Тх2), вход блока 3 через коммутатор подключается к выходу сумматора 9, и производится интегрирювание выходного напряжения последнего i - 1 в течение постоянного временного интервала Т. По окончании данного интервала напряжение на выходе блока 3 имеет вид

E:T.,:)Tx3-b Usb, ,.,

l(,+T.)l/Bbix i-1 T , и

где l RC - постоянная времени по основному входу блока 3. Данное напряжение подается на вход блока 8 и интегрируется в течение постоянного временного интервала TO. На выходе блока 8 по окончании этой операции формируется напряжение ,U,l To-U, 1/Дт,

fb)

где Uzfi- 1 -выходное напряжение блока 8 в соответствующий момент i - 1-го цикла; Тз - постоянная времени блока 8. Аналогично основному устройству можно показать, что установившееся значение выходного напряжения сумматора 9, формируемого в соответствии с (1), принимает вид

U,,,,ycT.).E N,N.--(;n)

где Tj - ; i 1,2.

Из выражения (4) следует, что влияние величины (5 на выходной сигнал источника калиброванных напряжений ослабляется в .

Таким образом, предлагаемое устройство практически не снижает точность известного и обеспечивает требуемый динамический диа пазон выходных сигналов. Однако в отличие от известного устройства разбиение входного кода на старшие и младшие разряды и разделение операций интегрирования соответствующих опорных сигналов позволяет на несколько порядков уменьшить тактовую частоту преобразователя кода во временной интервал, и обеспечивая при заданной разрешающей способности существенное повышение быстродействия источника калиброванных напряжений. Последнее

обстоятельство выгодно отличает предлагаемое устройство от известного, поскольку позволяет расширить область его возможного применения.

Формула изобретения

Источник калиброванных напряжений по авт. св. № 758095, отличающийся тем, что, с целью повышения быстродействия, в него

введены источник опорного тока и ключ, причем выход источника опорного тока через ключ связан с дополнительным входом первого блока интегрирования, а дополнительный выход преобразователя кода во временной интервал через блок управления связан с управляющим входом ключа.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 758095, кл. G 05 F 1/100, 04.04.79.

Авторы

Даты

1981-08-30—Публикация

1979-09-04—Подача