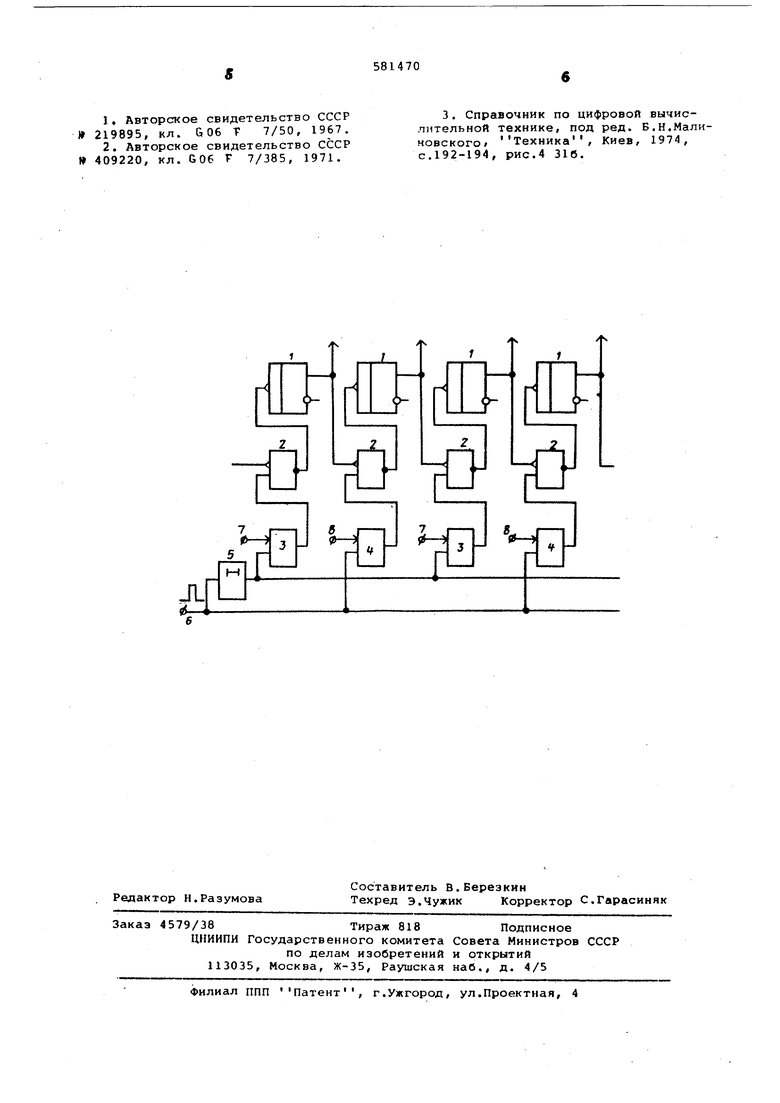

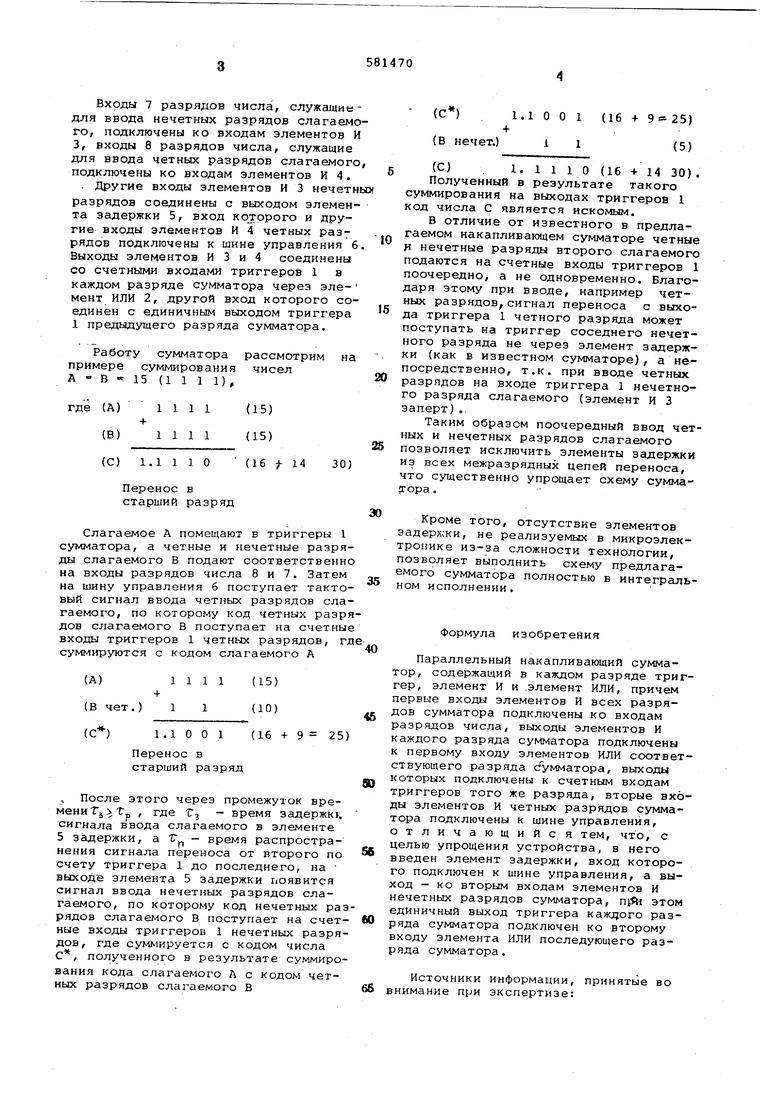

Изобретение отнодит.ся к цифровой вычислительной технике и может быть использовано для построения арифмеггических устройств. . -Известны накапливайщие сумматоры параллельного дейбтвия с.последовательным переносом l},2. Недостатком накапливающих сумматоров является сложность, обусловленная наличием линий задержек в цепях переноса между смежными триггерами. Причем в накапливающих сумматорах с последовательным переносом имеет место некоторое увеличение быстродействия, но оно достигается за счет введения в схему сумматора дополнительных элем нтов, т.е. за счет еще большего ус ложнения при сохранении линий задержек между смежными триггерами в цепях последовательного переноса. Известен также параллельный накапливающий сумматор, содержащий в каждом разряде триггер, элемент И и элемент ИЛИ, причем первые входы элементов И всех разрядов сумматора подключены ко входам разрядов числа, выходы элементов И каждого- разряда сумматора подключены к первому входу элементов ИЛИ соответствующего разряда сумматора, выходы которых подключены к счетным входам триггеров того же pa3pjfea, вторые входы элементов И четных разрядов :сумматора подключены к шине, управления з . Недостатком сумматора является сложность, обусловленная наличием в цепях переноса всех разрядов элемен тов задержки. Цель изобретения - упрощение сумматора за счет исключения элементов задержки из всех цепей последовательного переноса путем поочередного ввода четных и нечетных разрядов слагаемых. Эта цель достигается тем, что в сумматор введен элемент задержки, вход которого подключен к шине управления, а выход - ко вторым входам элементов И нечетных разрядов сумматора, при этом единичный выход триггера каждого Разряда сумматора подключен ко второму входу элемента ИЛИ последующего разряда сумматора. На чертеже приведена функциональная схема накапливающего сумматора. Предлагаемый накапливающий сумматор содержит тоиггеры 1 со счетным входом, элементы ИЛИ 2, элементы п j нечетных и 4 четных разрядов, элемент 5 задержки, и шину б управления Входы 7 разрядов числа, служащий для ввода нечетных разрядов слагаемо го, подключены ко входам элементов И 3, входы 8 разрядов числа, служащие для ввода четных разрядов слагаемого подключены ко входам элементов И 4. . Другие входы элементов И 3 нечетн разрядов соединены с выходом элемента задержки 5, вход которого и другие входы элементов И 4 четных разрядов подключены к шине управления 6 Выходы элементов И 3 и 4 соединены со счетными входами триггеров 1 в каждом разряде сумматора через элемент ИЛИ 2, другой вход которого со единен с единичным выходом триггера 1 предыдущего разряда сумматора, Работу сумматора рассмотрим на примере суммирования чисел А - В 15 (1 1 1 1), где (А)1111 + (В)1111 (С) 1.1 1 1 О (16 i- 14 30) Перенос в старший разряд Слагаемое А помещают в триггеры 1 сумматора, а четные и нечетные разря ды слагаемого В подают соответственн на входы разрядов числа В и 7. Затем на шину управления 6 поступает такто вый сигнал ввода четных разрядов сла гаемого, по которому код четных разр дов слагаемого В поступает на счетны входы триггеров 1 четных разрядов, г суммируются с кодом слагаемого А (В чет.) (16 + 9 25 1.1 О О 1 Перенос в старший разряд После этого через промежуток времени , где Tj - время задержку сигнала ввода слагаемого в элементе 5 задержки, а Т - время распространения сигнала переноса от второго по счету триггера 1 до последнего, на вьосоде элемента 5 задержки появится сигнал ввода нечетных разрядов слагаемого, по которому код нечетных ра рядов слагаемого В поступает на счет ные входы триггеров 1 нечетных разря дов, где суммируется с кодом числа С, полученного в результате суммиро вания кода слагаемого А с кодом четных разрядов слагаемого В (С)1.1001 (16 + ) + (В нечет.)11(5) (С) , 1.1110 (16 + 14 30). Полученный в результате такого суммирования на выходах триггеров 1 код числа С является искомым. В отличие от известного в предлагаемом накапливающем сумматоре четные 1 нечетные разряды второго слагаемого подаются на счетные входы триггеров 1 поочередно, а не одновременно. Благодаря этому при вводе, например четных разрядов,сигнал переноса с выхода триггера 1 четного разряда может поступать на триггер соседнего нечетного разряда не через элемент задержки (как в известном сумматоре), а непосредственно, т.к. при вводе четных разрядов на входе триггера 1 нечетного разряда слагаемого (элемент И 3 заперт) .. Таким образом поочередный ввод четных и нечетных разрядов слагаемого позволяет исключить элементы задержки из всех межразрядных цепей переноса, что существенно упрощает схему сумма -ора, Кроме того, отсутствие элементов задерх;ки, не реализуемых в микроэлектронике из-за сложности технологии, позволяет выполнить схему предлагаемого сумматора полностью в интегральном исполнении. Формула изобретения Параллельный накапливающий сумматор, содержащий в каждом разряде триггер, элемент И и .элемент ИЛИ, причем первые входы элементов И всех разрядов сумматора подключены ко входам разрядов числа, выходы элементов И каждого разряда сумматора подключены к первому входу элементов ИЛИ соответствующего разряда сГумматора, выходы которых подключены к счетным входам триггеров того же разряда, вторые входы элементов И четных разрядов сумматора подключены к шине управления, отличающий CRTем, что, с целью упрощения устройства, в него введен элемент задержки, вход которого подключен к шине управления, а выход - ко вторым входам элементов И нечетных разрядов сумматора, пуй этом единичный выход триггера каждого разряда сумматора подключен ко второму входу элемента ИЛИ последующего разряда сумматора. Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР 219895, кл. G06 Т 7/50, 1967.

2.Авторское свидетельство СССР О 409220, кл. G06 Г 7/385, 1971.

3. Справочник по цифровой вычислительной технике, под ред. Б.Н.Малиновского Техника, Киев, 1974, с.192-194, рис.4 316.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1978 |

|

SU744568A2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1578710A2 |

| Накапливающий сумматор | 1987 |

|

SU1418701A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Параллельный накапливающий сумматор | 1984 |

|

SU1242934A2 |

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Отсчетное устройство | 1976 |

|

SU661548A1 |

Авторы

Даты

1977-11-25—Публикация

1975-11-24—Подача