Изобретение относится к радиотехнике и может использоваться в системах фазовой автоподстройки частоты (ФАПЧ).

Цель изобретения - повьшениеточностиизмерения в фазовом режиме путем регулировки порога дискриминации при одновременном расширении диапазона измерения в фазовом режиме до 12 Л..

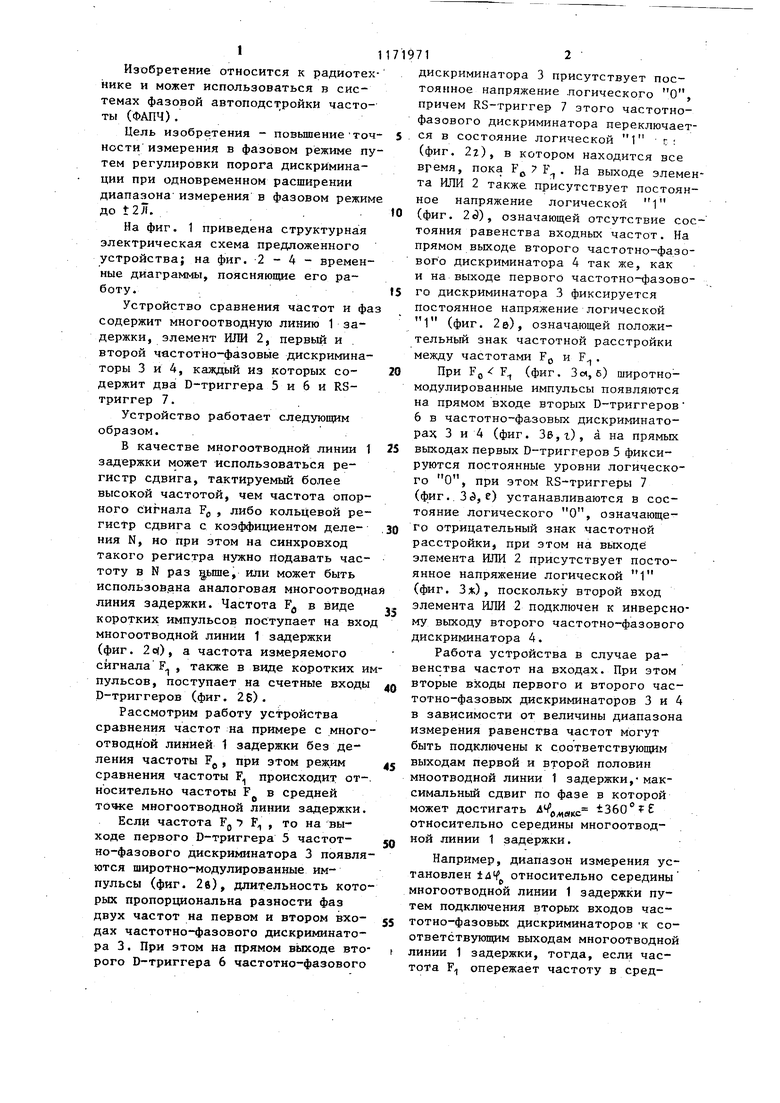

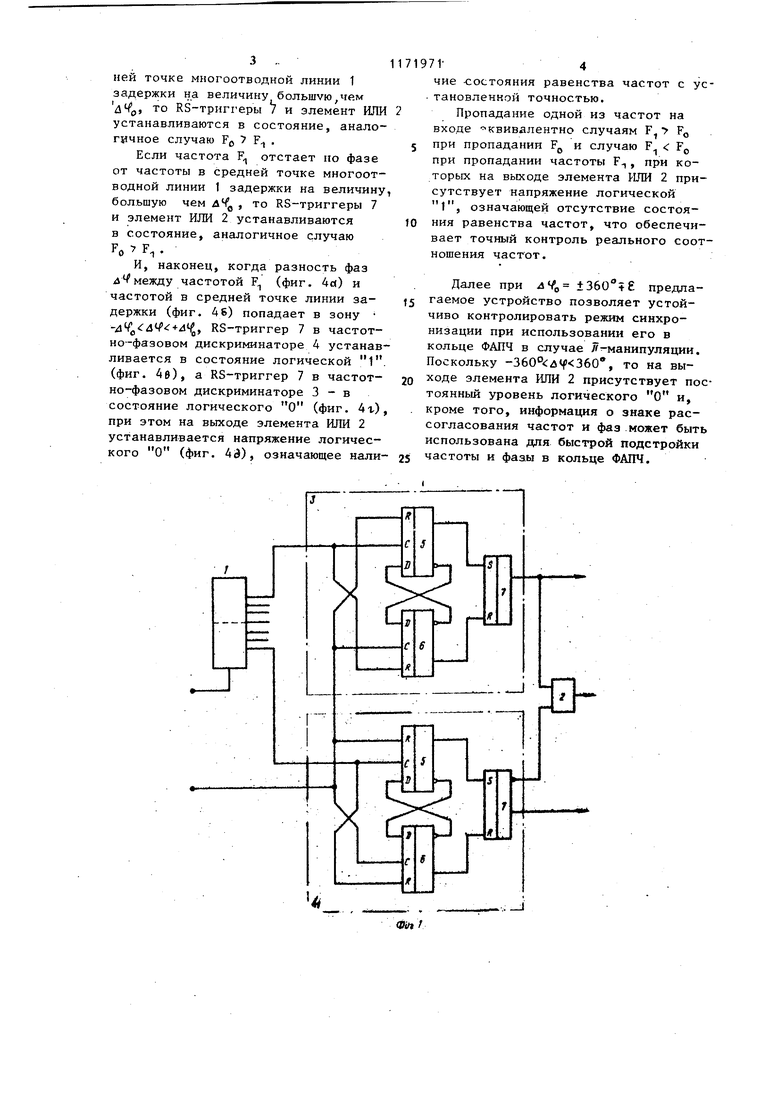

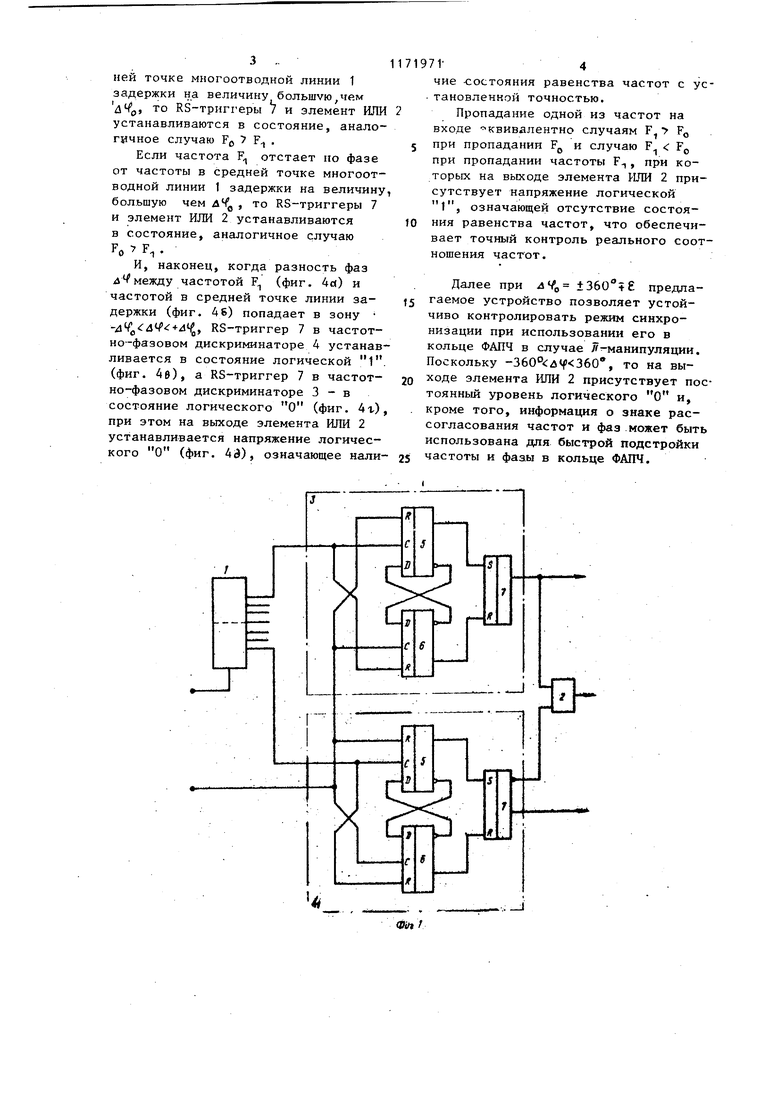

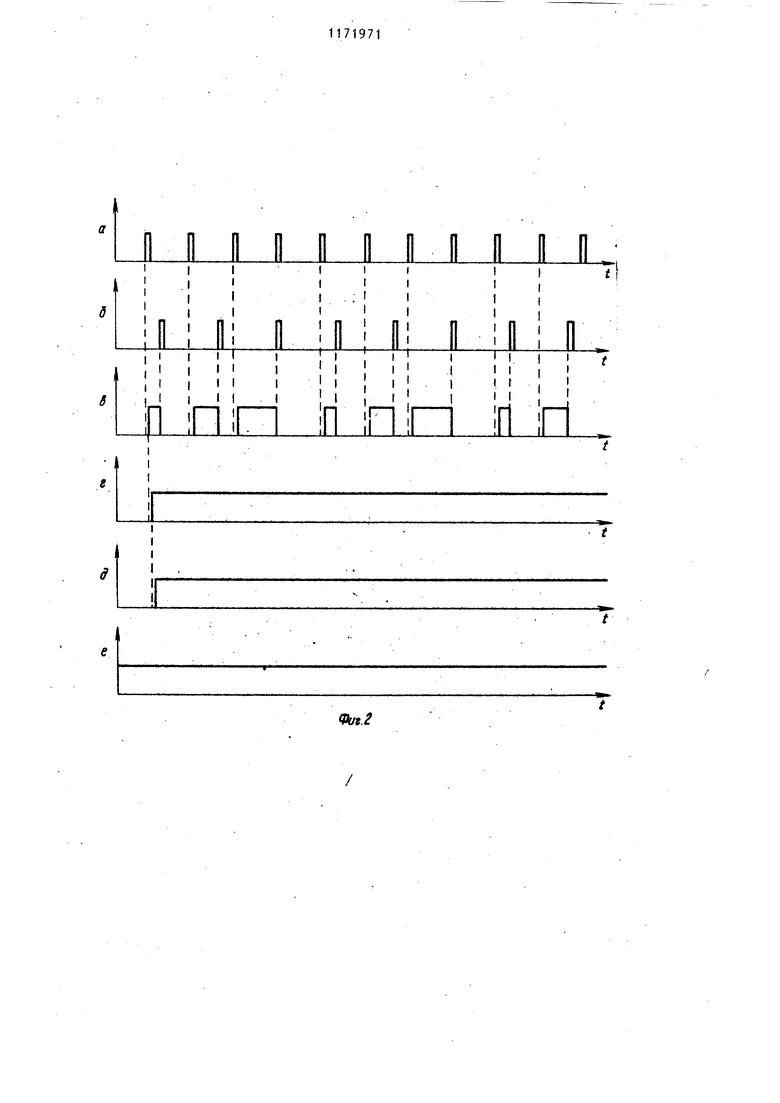

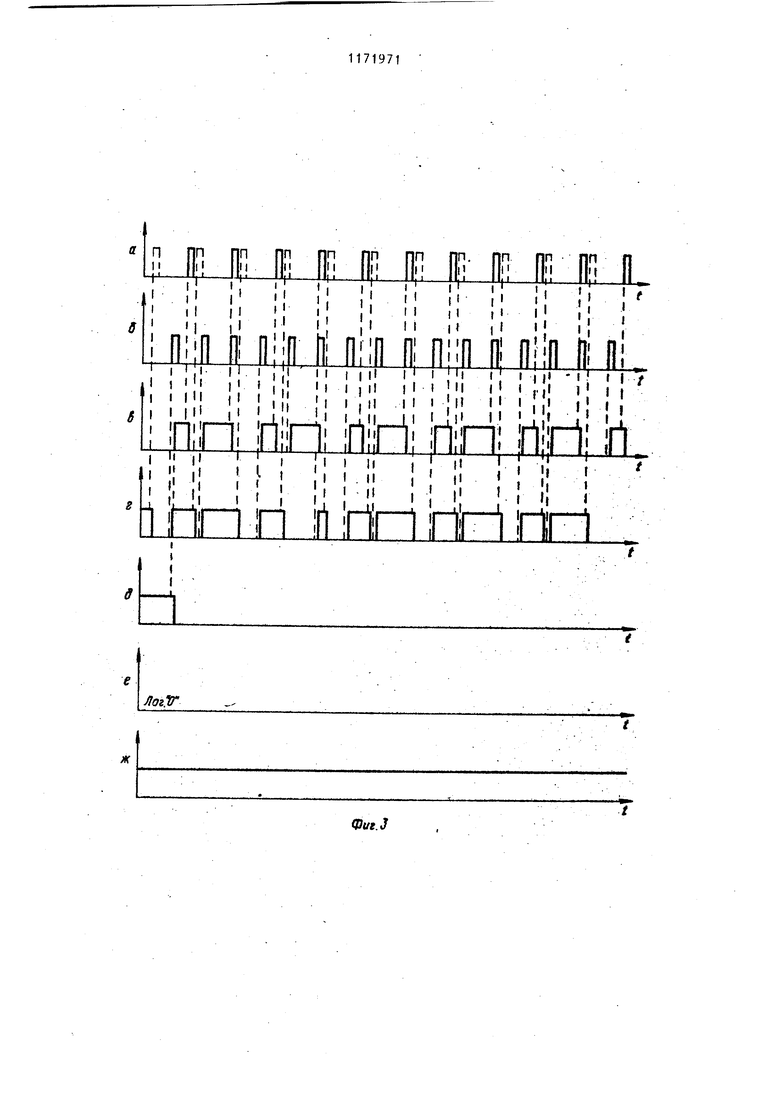

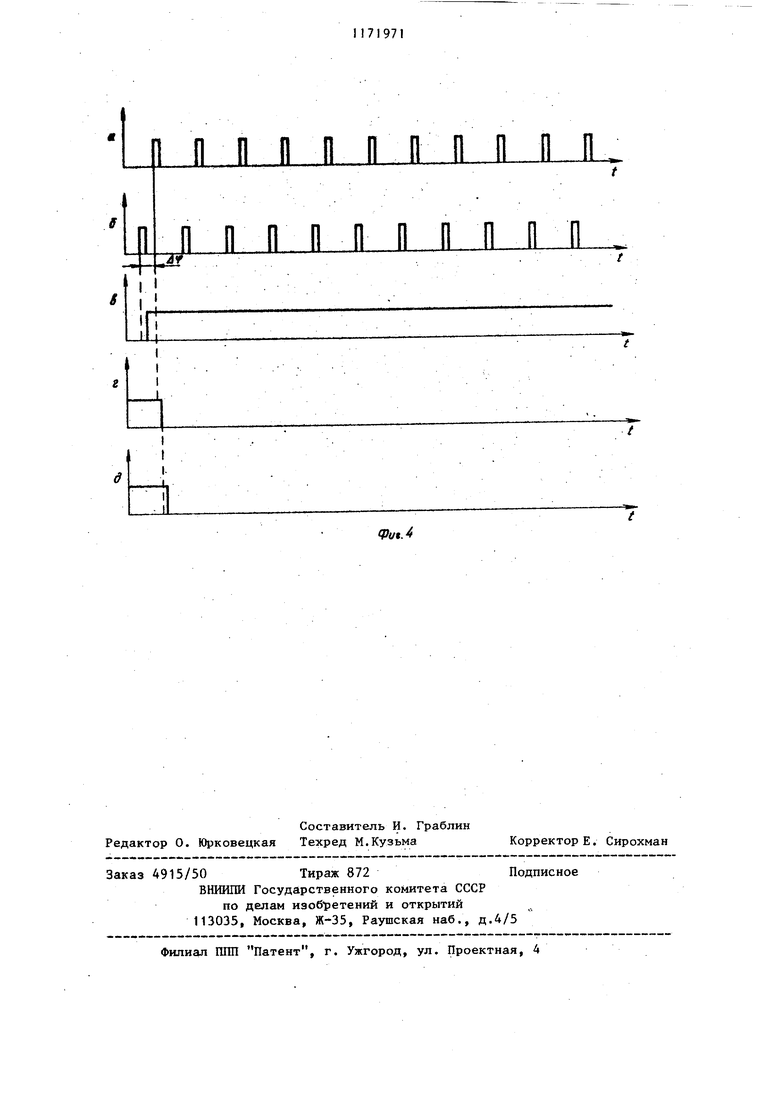

На фиг. 1 приведена структурная электрическая схема предложенного устройства; на фиг. 2 - 4 - временные диаграммы, поясняющие его работу.

Устройство сравнения частот и фаз содержит многоотводную линию 1 задержки, элемент ИЛИ 2, первый и . второй частотно-фазовые дискриминаторы 3 и 4, каждый из которых содержит два D-триггера 5 и 6 и RSтриггер 7.

Устройство работает следующим образом.

В качестве многоотводной линии 1 задержки может использоваться регистр сдвига, тактируемый более высокой частотой, чем частота опорного сигнала F , либо кольцевой регистр сдвига с коэффициентом деления N, но при этом на синхровход такого регистра нужно Додавать частоту в N раз |ьше, или может быть использов.ана аналоговая многоотводна линия задержки. Частота F в виде коротких импульсов поступает на вход многоотводной линии 1 задержки (фиг. 2о(), а частота измеряемого сигналаF. , также в виде коротких импульсов, поступает на счетные входы р-триггеров (фиг. 26).

Рассмотрим работу устройства сравнения частот на примере с многоотводной линией 1 задержки без деления частоты Fg, при этом режим сравнения частоты F происходит от-. носительно частоты F в средней то«се многоотводной линии задержки.

Если частота FQ F, , то на выходе первого D-триггера 5 частотно-фазового дискриминатора 3 появляются широтно-модулированные импульсы (фиг. 2в), длительность которых пропорциональна разности фаз двух частот на первом и втором входах частотно-фазового дискриминатора 3. При этом на прямом выходе второго D-триггера 6 частотно-фазового

дискриминатора 3 присутствует постоянное напряжение логического О, причем RS-триггер 7 этого частотнофазового дискриминатора переключается в состояние логической 1

с : (фиг. 22), в котором находится все время, пока F 7 F, . На выходе элемента ИЛИ 2 также присутствует постоян1

ное напряжение логической

(фиг. 2й), означающей отсутствие сотояния равенства входных частот. На прямом выходе второго частотно-фазового дискриминатора 4 так же, как и на выходе первого частотно-фазового дискриминатора 3 фиксируется постоянное напряжение логической 1 (фиг. 2и), означающей положительный знак частотной расстройки между частотами F;, и F .

При Fg F (фиг. Зо1, Б) широтномодулированные импульсы появляются на прямом входе вторых D-триггеров 6 в частотно-фазовых дискриминаторах 3 и 4 (фиг. 36, г), а на прямых выходах первых D-триггеров 5 фиксируются постоянные уровни логического О, при этом RS-триггеры 7 (фиг..3й, е) устанавливаются в состояние логического О, означающего отрицательный знак частотной расстройки, при этом на выходе элемента ИЛИ 2 присутствует постоянное напряжение логической 1 (фиг. Зж), поскольку второй вход элемента ИЛИ 2 подключен к инверсному выходу второго частотно-фазового дискриминатора 4.

Работа устройства в случае равенства частот на входах. При этом вторые входы первого и второго частотно-фазовых дискриминаторов 3 и 4 в зависимости от величины диапазона измерения равенства частот могут быть подключены к соответствующим выходам первой и второй половин мноотводной линии 1 задержки,- максимальньй сдвиг по фазе в которой может достигать (atx- -360 относительно середины многоотводной линии 1 задержки.

Например, диапазон измерения установлен ±4f относительно середины многоотводной линии 1 задержки путем подключения вторых входов частотно-фазовых дискриминаторов к соответствующим выходам многоотводной линии 1 задержки, тогда, если частота F опережает частоту в сред3 .. ней точке многоотводной линии 1 задержки на величину большую,чем 44. то RS-триггеры 7 и элемент ИЛИ устанавливаются в состояние, анало гичное случаю FO 7 F . Если частота F отстает по фазе от частоты в средней точке многоотводной линии 1 задержки на величину большую чем , то RS-триггеры 7 и элемент ИЛИ 2 устанавливаются в состояние, аналогичное случаю FO F, . И, наконец, когда разность фаз лVмежду частотой (фиг. 4с() и частотой в средней точке линии задержки (фиг. 46) попадает в зону -/l/; 4V +.«(, RS-триггер 7 в частотно-фазовом дискриминаторе 4 устанав ливается в состояние логической 1 (фиг. 4в), а RS-триггер 7 в частотно-фазовом дискриминаторе 3 - в состояние логического О (фиг. 4г) при этом на выходе элемента ИЛИ 2 устанавливается напряжение логического О (фиг. 4д), означающее нали714чие состояния равенства частот с установленной точностью. Пропадание одной из частот на входе -эквивалентно случаям F F,, при пропадании F и случаю F F при пропадании частоты Р, при которых на выходе элемента ИЖ 2 присутствует напряжение логической 1, означающей отсутствие состояния равенства частот, что обеспечивает точный контроль реального соотношения частот. Далее при 4% предлагаемое устройство позволяет устойчиво контролировать режим синхронизации при использовании его в кольце ФАПЧ в случае /7-манипуляции. Поскольку -360° 4«f 360, то на выходе элемента ИПИ 2 присутствует постоянный уровень логического О и, кроме того, информация о знаке расогласования частот и фаз может быть спользована для быстрой подстройки астоты и фазы в кольце ФАПЧ.

fl О n n П n n Я Я Г i

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый детектор | 1982 |

|

SU1095351A1 |

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1285558A1 |

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1246334A1 |

| Цифровой частотно-фазовый компаратор | 1985 |

|

SU1248025A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Импульсный частотно-фазовый детектор | 1985 |

|

SU1312718A1 |

| Формирователь разностной частоты импульсных последовательностей | 1985 |

|

SU1307567A1 |

1. УСТРОЙСТВО СРАВНЕНИЯ ЧАСТОТ И ФАЗ, содержащее два частотно-фазовых дискриминатора, линию задержки, вход которой является входом опорного сигнала, а первый выход линии задержки соединен с первым входом первого частотно-фазового дискриминатора, второй вход которого является входом измеряемого v сигнала, и элемент ИЛИ, входы которого соединены соответственно с прямым выходом первого частотно-фазового дискриминатора и инверсным выходом второго частотно-фазового дискриминатора, причем прямые выходы частотно-фазовых дискриминаторов и элемента ИЛИ являются выходами .устройства, отличающееся тем, что, с целью повышения точности измерения в фазовом режиме путем регулировки порога дискриминации при одновременном расширении диапазона измерения в фазовом режиме до 12F, линия задержки выполнена многоотводной, причем ее второй выход соединен с первым входом второго частотно-фазового дискриминатора, второй вход которого является входом измеряемого сигнала. 2. Устройство по п. 1, отлис S чающееся тем, что каждый частотно-фазовый дискриминатор содержит два D-триггера и RS-триггер, выходы которого являются выходами частотно-фазового дискриминатора, а 5 и R-входы соединены соответст венно с прямьми выходами первого и второго D-триггеров, причем инверсные выходы каждого D-триггера соедиVI нены с D-входом противоположного . D-триггера, а входы синхронизации каждого D-триггера соединены с IRVI входом противоположного D-триггера и являются входами частотно-фазового; дискриминатора.

I

I

Q

rI

1 П П П О П П П П П П J П П П П П П П о П

| Авторское свидетельство СССР по заявке № 3596612, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Импульсно-фазовый дискриминатор | 1973 |

|

SU450309A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-08-07—Публикация

1983-08-03—Подача