i.1

Изобретение относится к автоматике и вычислительной технике и может найти применение в управляющих системах и гибридных вычислительных устройствах для вычисления в следящем режиме экспоненциальной функции от аналогового сигнала с представлением результата в цифровой форме.

Цель изобретения - повышение быстродействия вычислителя.

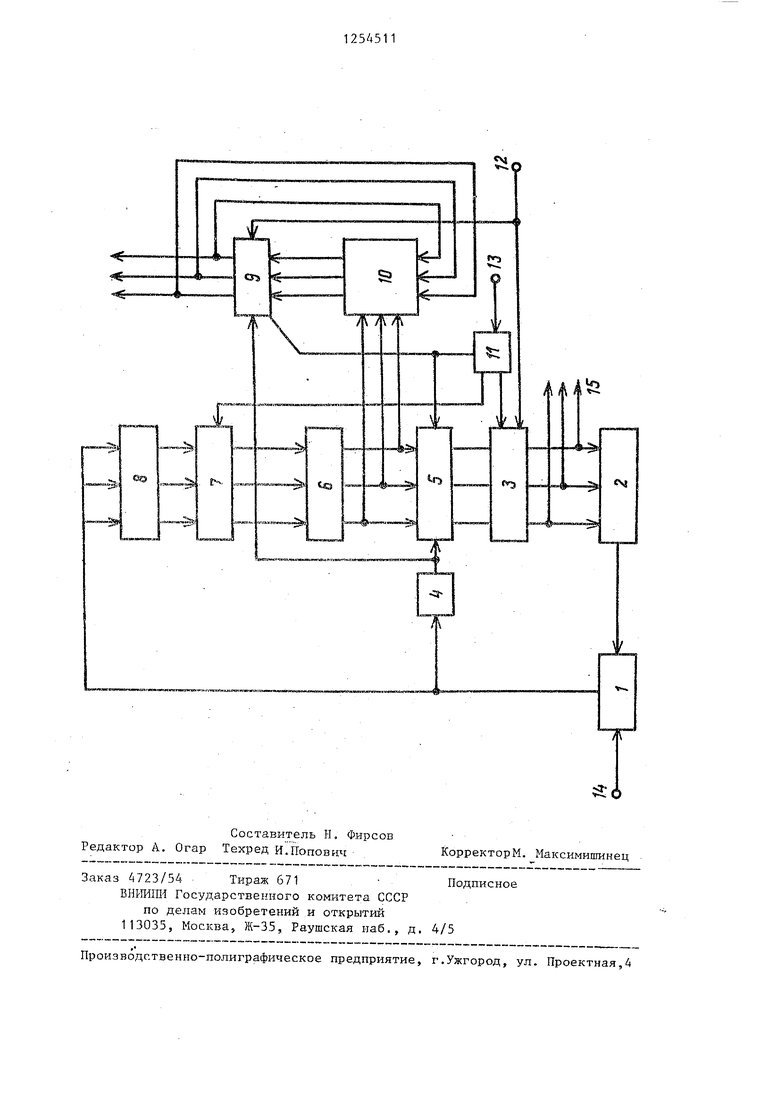

На чертеже изображена функциональная схема предлагаемого аналого- цифрового инкрементного вычислителя экспоненциальной функции.

Вычислитель содержит вычитающий блок 1, цифроаналогЪвый преобразователь 2, сумматор 3 аргумента, нуль .орган 4, блок 5 памяти, шифратор 6, приоритетный блок 7, группу 8 пороговых элементов, сумматор 9 функции, блок 10 сдвига, генератор 11 импульсов, вход 12 Начальная установка, вход 13 Запуск -устройства, вход 14 устройства, выходы 15 аргумента и выходы 16 функции устройства.

Вычислитель работает следующим образом.

Перед началом работы подается сигнал Начальная установка по входу 12 который обнуляет сумматор 3 аргумента и устанавливает код 1 в сумматор 9 функции, т.е. п разрядов младшей и п. разрядов старшей чати сумматора 9 функции обнуляются, а в младший разряд целой части это- гр сумматора заносится единица. Таким образом, для нулевого значения аргумента х О в сумматоре 3 устанавливается единичное значение функции у 1 в сумматоре 9 функции

который для 1x1 1 содержит п младших, п старших разрядов и два раз- ,ряда целой части числа. Блок 5 памя 1ти содержит 2п слов для выбранной разрядности устройства п, причем в первой половине (странице) блока 5 памяти записаны коды функции 1п(1+х для значений аргумента х 2 (, 2,.,.,п), а во второй половине этого блока записаны коды функции In(1-х) для тех же значений аргумента. Адре сация к той или ино.й половине блока 5 осуществляется сигналом с выхода нуль-органа 4, а адресация внутри каждой половины блока 5 происходит по сигналам с выхода шифратора 6. Сигнал, поступивший по входу 13 Запуск устройства, запускает генератор 11 импульсов, который выдает

5

51

Q 5

о

5

5

0

1 .2

три серии импульсов: основная серия- по третьему выходу, задержанная на время (t ) перехидного процесса в приоритетном блоке 7 - по второму выходу и задержанная на время (1:, ) переходного процесса в сумматоре 9 и блоке памяти 5 - по первому выходу генератора 11 импульсов.

Напряжение (flU) рассогласования (между входным напряжением аналогового сигнала по входу 14 устройства и напряжением обратной связи с выхода цифроаналогового преобразователя 2) с выхода вычитающего блока 1 прикладывается к входу нуль-органа 4 -и входам группы 8 пороговых элементов. Пороговые элементы группы 8 срабатывают при достижении напряжением рассогласования значений порогов, на которые настроены соответствующие пороговые элементы (например, по двоичному закону: 1,2,4,.. условных единиц младшего разряда 2 сумматора 3 аргумента).

8первом такте приоритетный блок 7 в моменты, определяемые тактовыми импульсами с третьего выхода генератора 1 1 импульсов, определяют старший по весу пороговый элемент группы 8 из числа сработавших и вьщает сигнал на соответствующий вход шифратора б, на выходе которого формируется номер позиции (разряда), в котором находится единица в позиционном двоичном коде с выходов приоритетного блока 7. Двоичный код номера позиции с выходов шифратора 6 поступает на управляющие входы блока 10 сдвига, который осуществляет передачу содержимого, сумматора 9 функции на вход того же сумматора

9со сдвигом на соответствующее число разрядов для суммирования или вычитания с предыдущим значением функции, причем выбор операции суммирования или вычитания производится сигналом с выхода нуль-органа 4, причем эта операция выполняется

во втором такте в моменты, определяемые тактовыми импульсами с второго выхода генератора 11 импульсов, задержанными относительно первой основной серии на время t, . По этой же серии производится считывание с блока 5 памяти кода функции Еп(1 + +дх) из ячейки, адрес которой определяется знаком приращения с выхода нуль-органа 4 (выбирается соответствующая половина блока 5 памяти) в

31

качестве старшего разряда адреса и кодом с выхода шифратора 6 в ка- честве младших разрядов адреса, т.е. для приращения сигнала x ±2 выби-г рается функция. In (1+2) записанная по адресу Т в соответствующей половине блока 5 памяти. Код функции In () с выхода блока 5 памяти поступает на вход сумматора 3 аргумента, в котором он суммируется с предыдущим содержимым сумматора 3 аргумента. Эта операция вьтолняется в третьем такте по сигналу с первого выхода генератора 11 импульсов, на котором формируется серия им- пульсов, задержанная относительно предыдущей серии по второму выходу генератора 11 импульсов на времяt определяемое временем считывания кода с блока 5 памяти. Полученный код с выхода сумматора 3 аргумента поступает на выход 15 аргумента и на вход цифроаналогового преобразователя 2, в котором он преобразуется в аналоговую величину и подается в качестве сигнала обратной связи на второй вход вычитающего блока 1. Таким образом, в каждый текзгщий момент в сумматоре 3 аргумента содержится цифровой код входного аналогового сигнала

X -bAX--X ;.-t-fn(1 s;g-h(uUVQ )

- ..

где sign luUlj - знак напряжения рас

. согласования, причем точность его представления зависит от выбранной разрядности сумматора 3 аргумента и блока 5 памяти.

Одновременно с этим в сумматоре 9 функции формируется текущее значение экспоненциальной фун.сции

-г

Y.

г.,) ,

так как

. xi лх

Y- -е L t + i

- р

-У, е

3;g-h(uU)-2. 1

- + sig-u{uU)-2 З .

Вычисление текущего цифрового значения функции и аргумента с точностью до младшего разряда 2 производится максимально за п тактов, причем в каждом такте генерируется

j to 5 20 25 зо

5

0

5

0

5

1 14

по одному импульсу на каждом из трех выходов генератора импульсов.

Формула изобретения

Аналого-цифровой инкрементный вычислитель экспоненциальной функции, содержащий вычитающий блок, цифро- аналоговый преобразователь, сумматор аргумента, нуль-орган, группу пороговых элементов, сумматор функции, блок сдвига и генератор импульсов, причем вход вычислителя соединен с первьм входом вычитающего блока, подключенного вторым входом к выходу цифроаналогового преобразователя, а выходом - к информационным входам пороговых элементов группы и к входу нуль-органа, выход которого пЬдключен к входу выбора режима сумматора функции, выходы старших разрядов которого соединены с выходами функции вычислителя и с информационными входами блока сдвига, подключенного выходами к входам сумматора функции, вход начальной установки Которого соединен с входом Начальная установка вычислителя и с входом начальной установки сумматора аргумента, подключенного выходами к входам цифроаналогового преобразователя и выходам аргумента вычислителя, а стробирующим входом - к первому выходу генератора импульсов, подключенного входом к входу Запуск вычислителя, а вторым выходом - к стробирующему входу сумматора функции, отличают и й- с я тем, что, с целью повышения быстродействия, в него введены блок памяти, шифратор и приоритетный блок, причем выходы пороговых элементов группы подключены к входам приоритетного блока, выходы которого соединены с входами шифратора, выходы которого соединены с входами управления величиной сдвига блока сдвига и с адресными входами блока памяти, кроме входа старшего разряда адреса блока памяти, подключенного входом к выходу нуль-органа, выходами - к входам сумматора аргумента, стробирзтощим входом - к второму выходу генератора импульсов, а третий выход генератора импульсов соединен со стробирующим входом приоритетного блока.

1

Oil

.

JTH ©

f

Irs

f

fS

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой вычислитель логарифмической функции | 1985 |

|

SU1247904A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

| Аналого-цифровое устройство для возведения в куб | 1985 |

|

SU1251113A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Аналого-цифровой инкрементный дифференциатор | 1985 |

|

SU1343410A1 |

| Устройство для вычисления тригонометрических функций | 1987 |

|

SU1427362A1 |

Изобретение относится к автоматике и вычислительной технике и может найти применение в управляющих системах и гибридных вычислительных устройствах для вычисления в .следящем режиме экспоненциальной функции от аналогового сигнала с представлением результата в цифровой форме. Цель изобре1 ения - повышение быстродействия. Сущность изобретения заключается в том, что в устройство, .содержащее вычитающий узел, цифро- аналоговый преобразователь, сумматоры аргумента и функции, нуль-орган, группу пороговых элементов, блок сдвига и генератор импульсов, дополнительно введены блок памяти, шифратор и приоритетный блок 1 ,ил. о 5g

Составитель PI. Фирсов Редактор A. Orap Техред И.ГГоповнч

Заказ 4723/54 Тираж 671 Подписное ВНШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная,4

КорректорМ. Максимишинец

| ВСЕСОЮ8ЫЛЯ f пши^ш-т;';'':;;^' :::•:: | 0 |

|

SU363973A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Введение в кибернетическую технику | |||

| Обработка физической информа-; ции /Под ред | |||

| Б.Н | |||

| Малиновского | |||

| Киев: Наукова думка, 1979, с.163- 166, рис.66. | |||

Авторы

Даты

1986-08-30—Публикация

1985-02-05—Подача