2,Устройство ПОП.1, ОТЛИчающееся тем, что блок запус ка генератора тактовых импульсов содержит элемент И,, элементы ИЛИ, элемент задержки и триггеры, -выход первого элемента ИЖ соединен через эле мент задержки с первым входом второго элемента ИЛИ, выход элемента И с первым входом первого триггера, вы ход которого соединен с вторым входо второго элемента ШШ, выход второго элемента ИЛИ соединен с первым входом второго триггера, второй вход ко торого подключен к выходу третьего элемента ИЛИ,, входы элемента И являются первыми входами -блока запуска генератора тактовых импульсов,, первы вход третьего элемента ИЛИ объединен с вторым входом первого триггера и является вторым входом блока запуска генератора тактовых импульсов, .входы первого элемента ИЛИ являются третьими входами блока запуска генерато ра тактовых импульсов, второй вход третьего элемента ИЛИ объединен с третьим входом первого триггера и яв ляется четвертым входим блока запуска генератора тактовых импульсов, выход второго триггера является выхо дом блока запуска генератора тактовых импульсов. 3.Устройство по П.1, о т л и чающееся тем, что логический блок содержит элементы памяти, элемент ШШ, элемент сравнения, ключи и триггер,, первый и второй выходы триггера соединены с первыми входами соответственно первого и второго клю чей, выход первого ключа соединен с первыми входами триггера и элемента ИЛИ, вых.од элемента ИЛИ соединен с первым входом первого элемента памяти,- выход которого соединен с первым входом элемента срав нения, выход элемента сравнения соединен с первым входом третьего ключа выход которо-го соединен с вторым входом элемента ИЛИ,- выход второго ключа соединен с первым входом второго элемента памяти, выход которого соединен с вторым входом третьего ключа, вторые входы первого и BTopoto ключей объединены и являются первым входом логического блока,- вторые входы первого и второго элементов памяти и триггера объединены и являются вторым входом логического блока, выход элемента 1 1 сравнения является выходом логического блока. 4.Устройство по П.1, о г л и ч аю Ще е с я тем, что анализатор содержит счетчики, ключи, триггеры, регистр, генератор тактовых импульсов элементы задержки и элемент ИЛИ, выход первого счетчика соединен с первыми входами первого триггера и.элемента ИЛИ, выход элемента ИЖ соединен через первый элемент задержки с первым входом генератора тактовых импульсов, выход которого соединен с первым входом регистра и через второй счетчик с входом второго элемента задержки, первым входом первого ключа и вторым входом генератора тактовых импульсов, выход первого ключа соединен С первыми входами второго и третьего триггеров, выход второго триггера соединен с первым входом второго ключа, выход регистра соединен с первым входом четвертого триггера, выход второго элемента задержки соединен с вторыми входами первого, второго, третьего и четвертого триггеров и второго ключа, выход третьего триггера соединен с первым входом третьего ключа, выход четвертого триггера соединен с вторьм входом первого ключа, .вход счетчика, второй вход третьего ключа, вторые входы регистра и вторые входы элемента ИЛИ являются соответственно первым, вторым, третьим и четвертым входами .анализатора J выходы первого ключа, первого триггера, второго и третьего ключей являются соответственно первым, вторым, третьим и четвертым выходами анализатора. 5.Устройство по П.1, о т л и ч аю щ е е с я тем, что блок коррекции символов содержит элементы задержки, ключи и инверторы, выходы элементов задержки соединены с первыми входами соответствующих ключей, выходы которых соединены с первыми входами соответствуклцих инверторов, входы элементов задержки объединены с вторыми входами соответствующих ключей и являются первыми входами блока коррекции символов, вторые входы инверторов являются вторыми входами блока коррекции символов, выходы инверторов и выходы ключей являются соответственно первыми и вторыми выходами блока коррекции символов. 1 ,1 Изобретение относится к электросвязи и может быть использовано в устройствах для приема и обработки составных сигналов с избыточностью, формируемых на основе кодов с про-веркой на четность. Известно устройство для посимволького приема сигналов, содержащее демодулятор, пороговый блок и решающий блок 1 j .. Недостатком данного устройства является низшая помехоустойчивость приема инфбрмации. Наиболее близким по техническо г сущности к предлагаемому является . устройство для приема-сигналов с избыточностью, содержащее демодулятор, вход которого является входом устрой ств.а, выход демодулятора соединен через аналого-цифровой преобразователь с первым входом первого блока памяти выход первого блока памяти соединен с входами второго блока памяти, вы- числительного блока и чере.з преобразователь сигналов с первым входом первого регистра, выход первого регистра соединен через декодер с входом Третьего блока памяти, вход (выход) которого соединен с выходом (входом) вычислительного блока, выход третьего блока памяти является выходом устройства, первый и второй выходы второго блока памяти соединены с первьо4И входами соответственно ключа и блока сравнения-, выход ключасоединен через четвертый блок памяти с вторым входом блока сравнения, первый и второй выходы которого соединены соответственно с вторым входом ключа и первым входом первого блока ключей, генератор тактовых импульс ов, выход которого соединен с входами первого, второго счетчиков и вторым входом neprfbro блока памяти, выходы первого счетчика соединены с соответствующими вторьми входами первого блока ключей, выходы которого соединены через второй регистр с первыми входами второго блока ключей, второй вход которого подключен к выходу второго счетчика, выходы второго блока ключей соединены через дешифратор, третий регистр и блок коррекции символов с соответствующими вторыми входами первого регистра 21. .Недостатком известного устройства является сложность, поскольку оно включает в свой состав блоки памяти и декодер, служащий для декодирова81ния избыточных сигналов с больпшм кодовым расстоянием. В случае использования избыточных сигналов, формируемых на основе кодов с проверкой на четность, для которых минимальное кодовое расстояние между кодовыми комбинациями равно двум,данное устройство можно значительно упростить. Цель изобретения - упрощение устройства. Указанная цель достигается тем, i что в устройство для приема сигналов с избыточностью, содержащее демодулятор, вход которого является входом устройства, выход демодулятора соединен через аналого-цифровой преобразователь с первым входом блока памяти, генератор тактовых импульсов, выход, которого соединение входами Первого и втооого счетчиков, выходы первого счетчика соединены с соответст-г вующими первыми входами первого блока ключей, выходы которого соединены через первый регистр с соответствукнцими первыми входами второго блока ключей, выход второго счетчика соединен с вторым входом второго блока ключей, выходы которого соединены через последовательно соединенные дешифратор и второй регистр с соответствующими первыми входами -блока коррекции символов, первые выходы блока коррекции символов соединены с соответствующими первыми входами третьего регистра, И ключ, введены, пороговый блок, анализатору злемент задержки, блок запусг ка генератора тактовых импульсов и логический блок, первые выходы блока памяти соединены с соответствующими первыми входами блока запуска генератора тактовых импульсов, второй выход - с первым входом логического блока и через пороговый блок с первым входом ключа, выход ключа соединен с вторым входом третьего регистра и.первым входом анализатора, первый выход и второй вход анализатора соединены соответственно с третьим входом и первым выходом третьего регистра, второй выход анализатора соединен с вторым входом ключа третий выход - с вторым входом блока запуска генератора тактовых импульсов, четвертый выход анализатора является выходом устройства, вторые выходы третьего регистра соединены с соответствующими третьими входами анализатора и вторыми 11 входами блока коррекции символов, вторые выходы блока коррекции символов соединены с соответствующими чет вертымй входами анализатора, вторыми входами блока памяти и третьими входами блока запуска генератора тактовых импульсов, выход блока запуска генератора тактовых импульсов соединен с входом генератора тактовых импульсов, выход которого соединен через элемент задержки с третьим входом блока памяти, выход второго счет чика соединен с четвертым входом бло ка запуска генератора тактовых импульсов и вторым входом логического блока, выход которого соединен с вто рым входом первого блока ключей. Кроме того, блок запуска генерато ра тактовых импульсов содержит элемент И, элементы ШШ, элемент задерж ки и триггеры, -выход первого элемента ИЛИ соединен через элемент задерж ки с первым входом второго элемента ИЛИ, выход элемента И - с первым входом первого триггера, выход которого соединен с вторым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с первым входом второго триггера, второй вход которо го подключен к выходу третьего элемента ШШ, входы элемента И являются первыми входами блока запуска генера тора тактовых импульсов, первый вход третьего элемента- ИЛИ объединен с вТорьм входом первого триггера и является вторым входом блока запуска генеоатооа тактовых импульсов, вхопы пеового элемента ШШ являются третьи ми входами блока запуска генератора тактовых импульсов, второй вход третьего элемента ИЛИ объединен с третьим входом первого триггера и является четвертым входом блока запуска генератора тактовых импульсов, выход второго триггера является выходом блока запуска генератора тактовых импульсов. Логический блок содержит элементы памяти, элемент ИЛИ, элемейт срав нения, ключи и триггер, первый и вто рой выходы триггера соединены с первыми входами соответственно первого и второго ключей, выход первого ключа соединен с первыми входами тригге ра и элемента ШШ, выход элемента ИЛИ соединен с первым входом первого эле мента памяти, выход которого соедине с первым входом элемента сравнения, выход элемента сравнения соединен с 1 первым входом третьего ключа, выход которого соединен с вторым входом элемента ИЛИ, выход второго ключа соединен с первым входом второго элемента памяти, выход которого соединен с вторым входом третьего ключа, вторые входы первого и второго ключей объединены и- являются первь1м входом логического блока, вторые входы первого и второго элементов памяти и триггера объединены и являются вторым входом логического блока, выход элемента сравнения является выходом логического блока.. Анализатор содержит счетчики, ключи, триггеры, регистр, генератор тактовых импульсов, элементы задержки и элемент .ИЛИ, выход первого счетчика соединен с первыми входами первого триггера и элемента ИЛИ, вьгход элемента ИЛИ соединен через первый элемент задержки с первым входом генератора тактовых импульсов, выход которого соединен с первым входом регистра и. через второй счетчик, с входом второго элемента задержки, первым входом первого-ключа и вторым входом генератора тактовых импульсов, выход первого ключа соединен с первыми входами второго и третьего триггеров, -выход второго триггера соединен с первым входом второго ключа, выход регистра соединен с первым входом чет вертого триггера, вьгход второго элемента задержки соединен с вторыми входами первого, второго, третьего, четвертого триггеров и второго ключа, выход третьего триггера соединен с первым входом третьего ключа, выход четвертого триггера соединен с вторым входом первого ключа, вход счетчика, второй вход третьего ключа, вторые входы регистра и вторые входы элемента ИЛИ являются соответственно первым, вторым, третьим и четвертым входами анапизатдра, выходы первого ключа, первого триггера, второго и третьего ключей являются соответственно первым,вторым, третьим и четвертым выходами анализатора. Кроме того, блок коррекции символов содержит элементы задержки, ключи и инверторы, выходы элементов задержки соединены с первыми входами соответствукядих ключей, выходы которых соединены с первыми входами соответствующих инверторов, входы элементов задержки объединены с вторыми входами соответствугацих ключей и являются первыми входами блока коррекции символов, вторые вхс. .ы инверторов являются вторыми входами- блока коррекции символов, выходы инверторов и выходы ключей являются соответственно первыми и вторыми выходами блока коррекции символов. На фиг.1 представлена структурная схема предлагаемого устройства, на фиг.2 - структурная схема блока запуска генератора тактовых импульсовJ на фиг.З - структурная схема логического блока, на фиг.4 - структурная схема анализатораJ на фиг.5 - структурная схема блока коррекции символов. Устройство для приема сигналов с избыточностью содержит демодулятор 1,аналого-цифровой преобразователь 2,блок 3 памяти,блок 4 запуска генератора тактовых импульсов, пороговый блок 5, ключ 6, логический блок 7, блок 8 ключей, регистры 9 и 10, блок 11 ключей, дешифратор 12, регистр 13, анализатор.14, счетчики 15 1и 16, генератор 17 тактовых импульсов, элемент 18 задержки и блок 19 коррекции символов. Блок 4 запуска генератора тактовых импульсов содержит элемент И 20, элемент 21 задержки, элементы ИЛИ 22 24, и триггеры 25 и 26. Логический блок 7 содержит элемент ИЛИ 27, элементы 28 и 29 памяти, элемент 30 сравнения, ключи 31-3 и триггер 34, анализатор 14 - счетчик 35, элемент ИЛИ 36, регистр. 37, триггеры 38-41, ключи 42-44, элементы 45 и 46 задержки, счетчик 47 и гё нератор /;8 тактовых импульсов, блок 19 коррекции символов - элементы 49 задержки, ключи 50 и инверторы .51. Демодулятор 1 преобразует входной высокочастотный сигнал в выходной аналоговый составной сигнал. Аналого цифровой преобразователь 2 преобразу ет амплитуду каждого элементарного аналогового сигнала в цифровой сигна который запоминается в блоке 3 па-., г мяти Блок 4 запуска генератора формиру

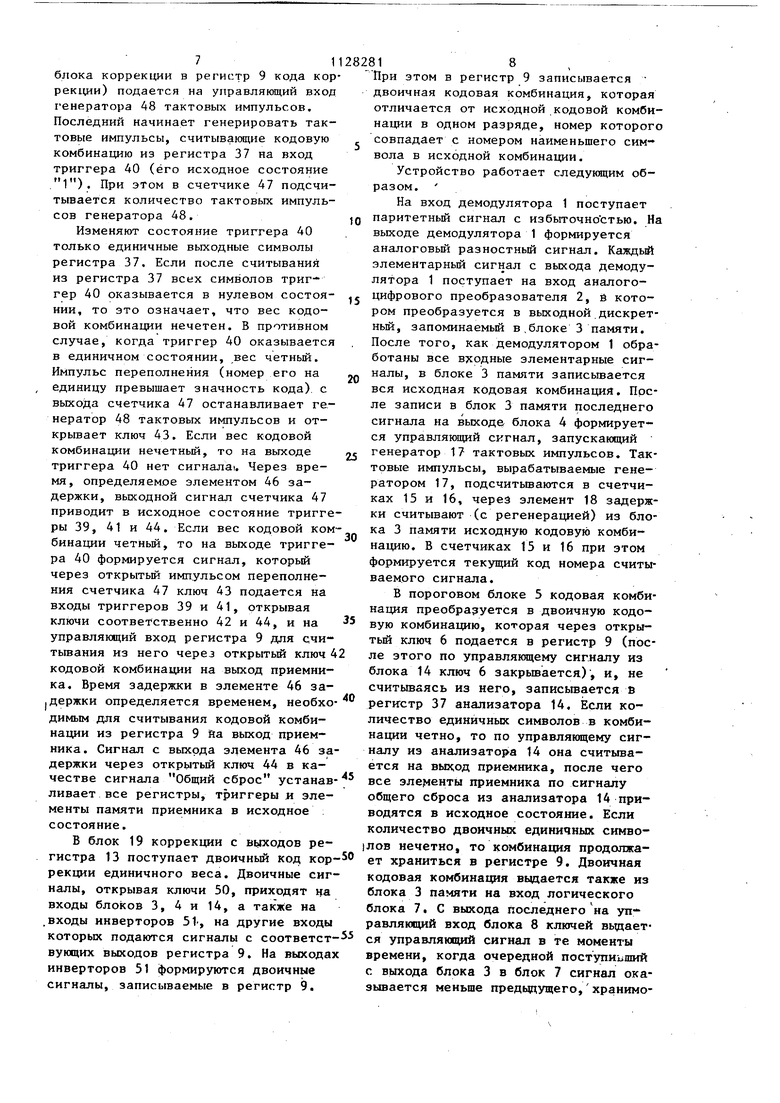

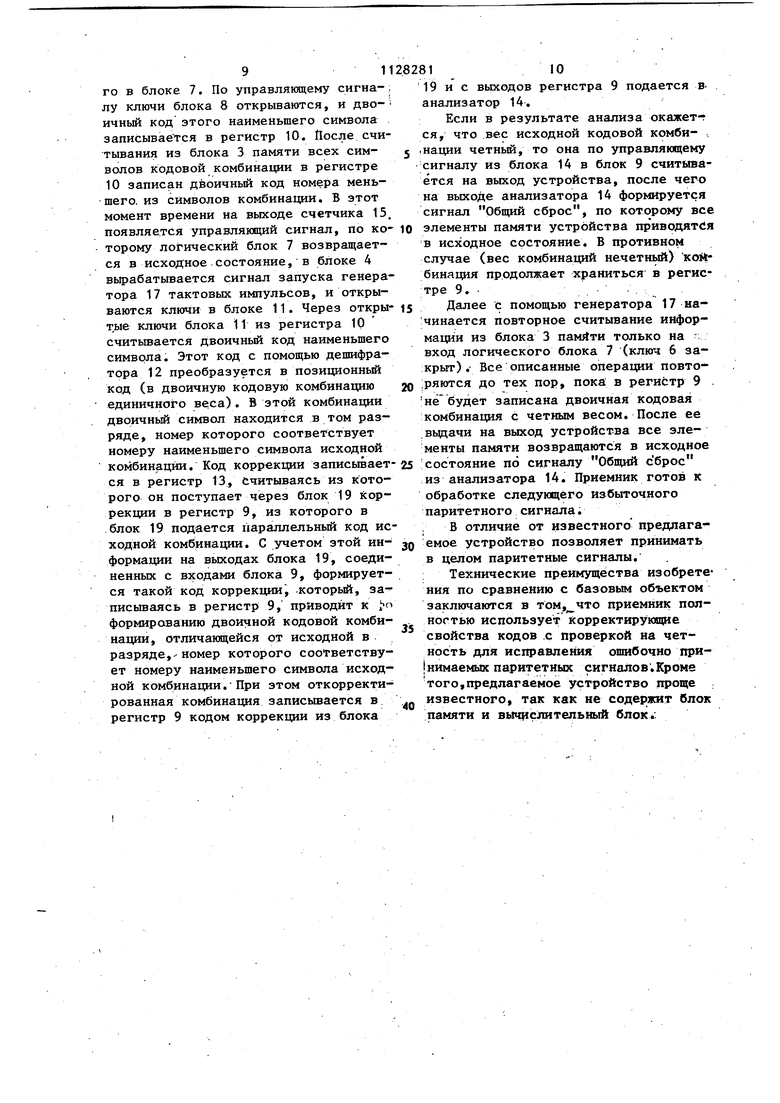

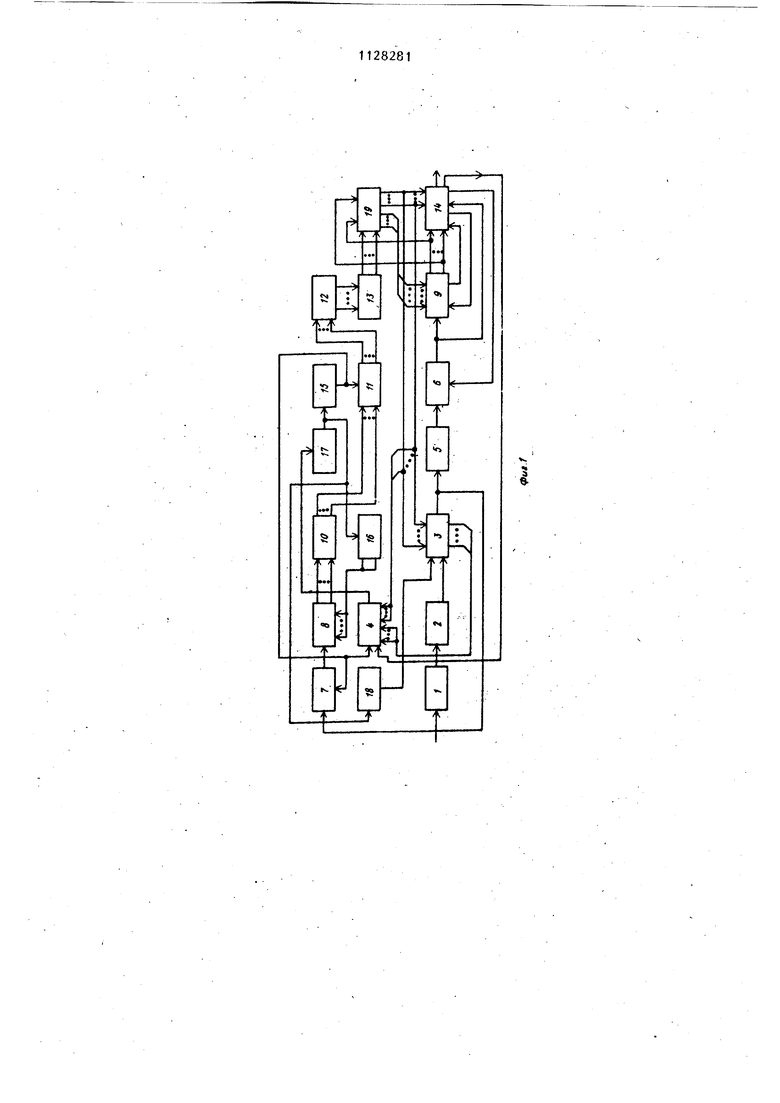

ет управляющий сигнал на выходе элемента И 20 как то.лько все ячейки блока 3 памяти заполняются. При этом .триггер 25 устанавливается в единичное состояние (исходное состояние триггера 25 - нулевое), на его выходе появляется сигнал, который через элемент ИЛИ 23 устанавливает триг11

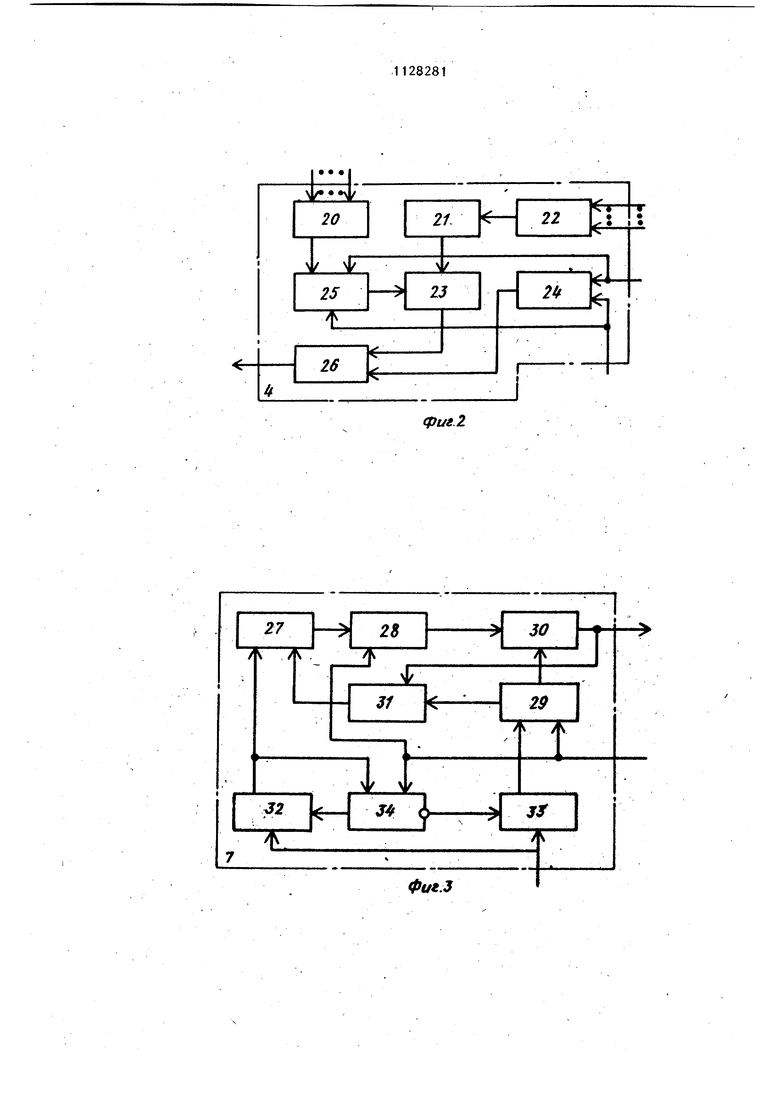

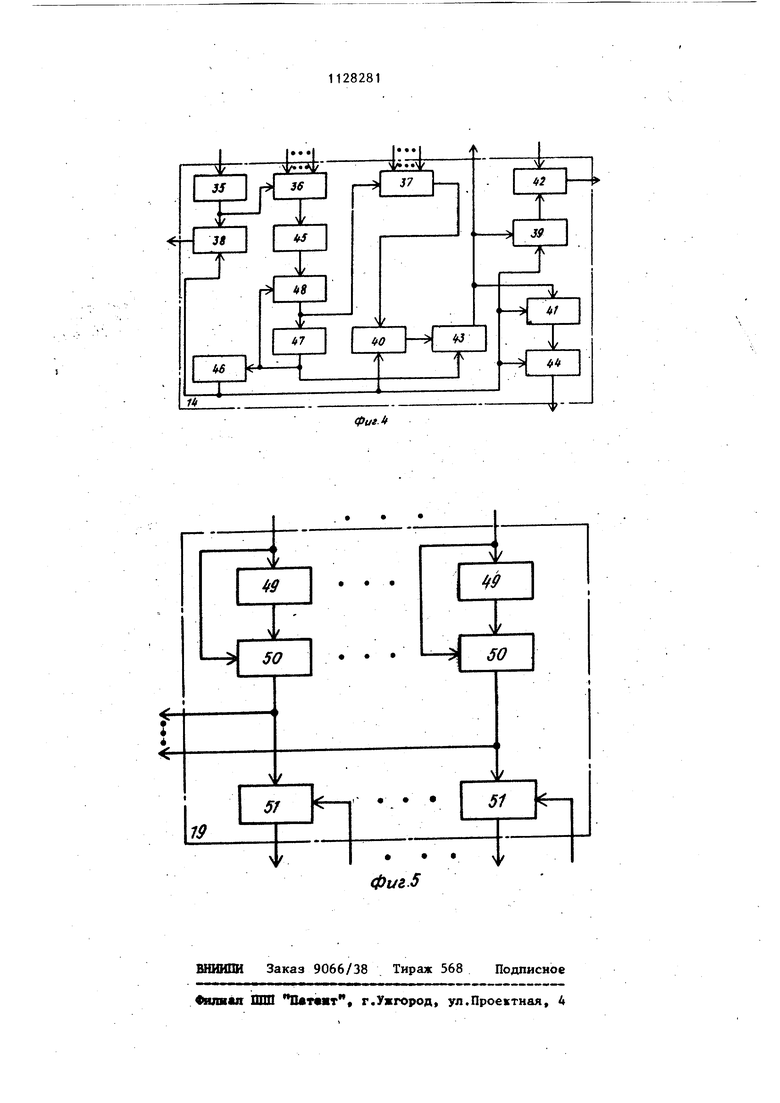

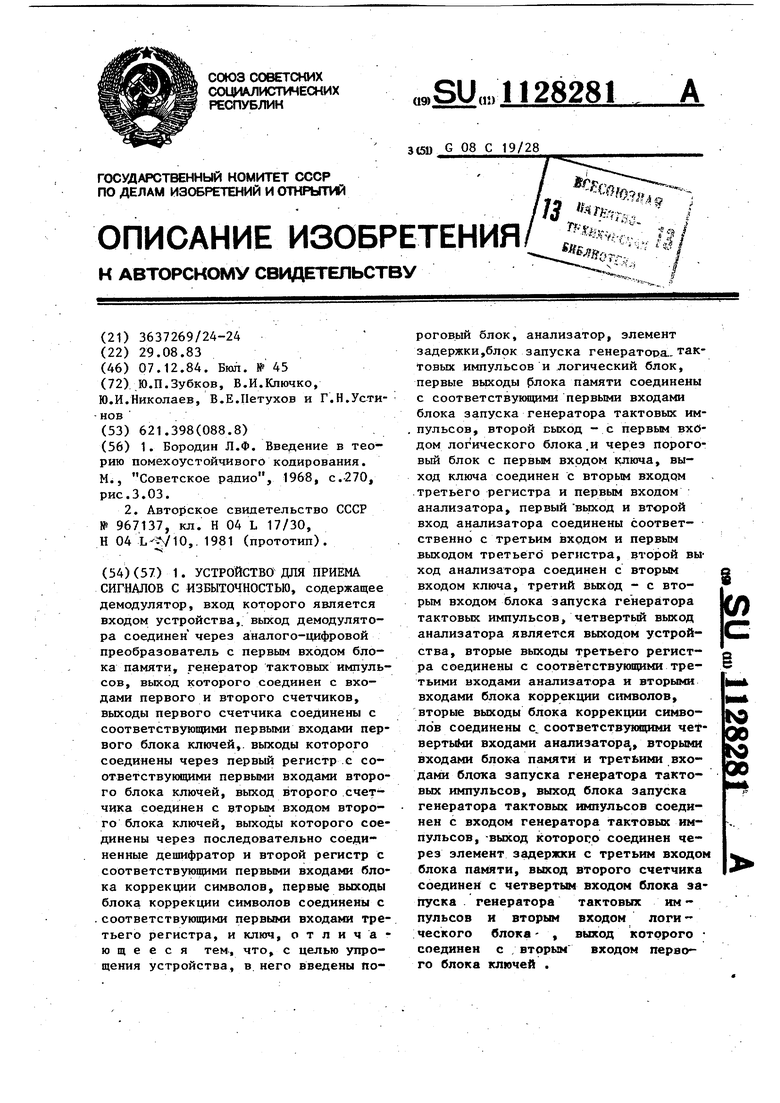

из исходного нулевого состояния в единичное, ключ 6 закрывается.. Кодо вая комбинация из регистра 9 по параллельным выходам записывается в регистр 37.. Выходной-сигнал счетчика 35 через элемент ШШ 36 и элемент А5 задержки (время задержки определяется необходимым временем для записи -из 1 гер 26 в единичное состояние (исходное состояние триггера 26 - нулевое),« тем самым запуская генератор 17 тактовых импульсов. Сигнал с выхода счетчика 15 сбрасьшает триггеры 25 и 26 в исходное состояние. При этом триггер 25 запоминает это нулевое состояние до тех пор, пока не будет получен сигнал общего сброса с выхогда анализатора 14. При формировании и считывании кода коррекции с выходов блока 19 на выходе элемента ИЛИ 22 формируется сигнал, который через элемент 21 задержки и элемент ИЛИ 23 переводит триггер 26 в единичное состояние, запуская генератор 17. Логический блок 7 запоминает элементарньй сигнал в элементе 28 памяти, которьм поступает из блока 3 памяти через ключ 32 и элемент ИЛИ 27, На вькоде элемента 30 сравнения появляется сигнал в TOM случае, если величина сигнала, записанного в элементе 28 памяти, меньше величины сигнала, записанного в элементе 29 памяти. Выходной сигнал ключа 32 переводит триггер 34 в состояние, при котором ключ 32 закрывается, а ключ 33 открьгоается. Поэтому следующий сигнал через открытый ключ 33 записьшается в элемент 29 памяти. Если сигнал, записанный в элементе 28 памяти, больше сигнала, записанного в элементе 29 памяти, то на выходе элемента 30 сравнения формируется управляняций сигнал, открываю(ций ключ 31, и сигнал из элемента 29 памяти переписывается в элемент 28 памяти. После того, как отработан весь сложный сигнал, на выходе счетчика 15 формируется управлякн1Ц1й сигнал, устанавливающий триггер 34 в исходное состояние и обнулящий ячейки элемен- : тов 28 н 29 памяти. В анализаторе 14 сигналы с выхода ключа 6. поступают на вход счетчика 35, в котором подсчитывается их количество. Как только это число станс вится равным значности кода на выходе счетчика 33 появляется управляищий сигнал, переводящий триггер 38 блока коррекции в регистр 9 кода кор рек1у1и) подается на управляющий вход генератора 48 тактовых импульсов. Последний начинает генерировать тактовые импульсы, считыванщие кодовую комбинацию из регистра 37 на вход триггера 40 (его исходное состояние .1). При этом в счетчике 47 подсчитывается количество тактовых импульсов генератора 48, Изменяют состояние триггера 40 только единичные выходные символы регистра 37. Если после считывания из регистра 37 всех символов триг- гер 40 оказывается в нулевом состоянии, то это означает, что вес кодовой комбинации нечетен. В противном случае, когда триггер 40 оказывается в единичном состоянии, вес четный. Импульс переполнения (номер его на единицу превышает значность кода), с выхода счетчика 47 останавливает генератор 48 тактовых и myльcoв и открывает ключ 43. Если вес кодовой комбинации нечетный, то на выходе триггера 40 нет сигнала). Через время, определяемое элементом 46 задержки, выходной сигнал счетчика 47 приводит в исходное состояние тригге ры 39, 41 и 44, Если вес кодовой ком бинации четНьй, то на выходе триггера 40 формируется сигнал, которьй через открытый импульсом переполнения счетчика 47 ключ 43 подается на входы триггеров 39 и 41, рткрывая ключи соответственно 42 и 44, и на управляющий вход регистра 9 для считьшания из него через открытый ключ кодовой комбинации на выход приемника. Время задержки в элементе 46 за.держки определяется временем, необхо димым для считывания кодовой комбинации из регистра 9 йа выход приемника. Сигнал с выхода элемента 46 з держки через открытый ключ 44 в качестве сигнала Общий сброс устана ливает все регистры, триггеры и элементы памяти приемника в исходное состояние, В блок 19 коррекции с выходов регистра 13 поступает двоичньй код коррекции единичного веса. Двоичные сигналы, открывая ключи 50, приходят на входы блоков 3, 4 и 14, а также на .входы инверторов St, на другие входы

-55

которых подаются сигналы с соотаетст вующих выходов регистра 9. На выходах инверторов 51 формируются двоичные сигналы, записываемые в регистр 9,

кодовая комбинация вццается также из блока 3 памяти на вход логического блока 7. С выхода последнего на управляющий вход блока 8 ключей выдается управлякхций сигнал в те моменты времени, когда очередной поступи11ший с выхода блока 3 в блок 7 сигнал оказывается меньше предыдущего,хранимоПри этом в регистр 9 записывается двоичная кодовая комбинация, которая отличается от исходной кодовой комбинации в одном разряде, номер которого совпадает с номером наименьшего сим вола в исходной комбинации. Устройство работает следукяцим образом. На вход демодулятора 1 поступает паритетный сигнал с избыточностью. На выходе демодулятора 1 формируется аналоговый разностный сигнал, Кс1ЖдьА элементарный сигнал с выхода демодулятора 1 поступает на вход аналогоцифрового преобразователя 2, и котором преобразуется в выходной дискретньй, запоминаемьй в.блоке 3 памяти. После того, как демодулятором 1 обработаны все входные элементарные сигналы, в блоке 3 памяти записьшается вся исходная кодовая комбинация, Прсле записи в блок 3 памяти последнего сигнала на выходе, блока 4 формируется управляющий сигнал, запускающий генератор 17 тактовых импульсов. Тактовые импульсы, вырабатываемые генератором 17, подсчитьшаются в счетчиках 15 и 16, через элемент 18 задержки считывают (с регенерацией) из блока 3 памяти исходную кодовую комбинацию. В счетчиках 15 и 16 при этом формируется текущий код номера считываемого сигнала. В пороговом блоке 5 кодовая комбинация преобразуется в двоичную кодовую комбинацию, которая через откры- тьй ключ 6 подается в регистр 9 (после этого по управляющему сигналу из блока 14 ключ 6 закрьтается), и, не считываясь из него, записьшается в регкстр 37 анализатора 14. Если количество единичных символов в комбинации четно, то по управляницему сигналу из анализатора 14 она считывается на выход приемника, после чего все элементы приемника по сигналу общего сброса из анализатора 14 приводятся в исходное состояние. Если количество двоичных единичных симво|лов нечетно, то комбинация продолжа50 ет храниться в регистре 9. Двоичная го в блоке 7. По управляющему сигналу ключи блока 8 открываются, и двоичный код этого наименьшего символа записывается в регистр 10. Йосле считывания из блока 3 памяти всех символов кодовой комбинации в регистре 10 записан двоичньй код номера меньшего, из символов комбинации. В этот момент времени на выходе счетчика 15 появляется управляющий сигнал, по ко торому логический блок 7 возвращается в исходное состояние, в блоке 4 вырабатьшается сигнал запуска генера тора 17 тактовых импульсов, и открываются ключи в блоке 11. Через откры тые ключи блока 11 из регистра 10 считьшается двоичный код наименьшего символа. Этот код с помощью дешифратора 12 преобразуется в позиционный код (в двоичную кодовую комбинацию единичного веса). В этой комбинации двоичный символ находится в том разряде, номер которого соответствует номеру наименьшего символа исходной комбинации. Код коррекции записывает ся в регистр 13, Считываясь из которого он поступает через блок 19 коррекции в регистр 9, из которого в блок 19 подается параллельный код ис

ходной комбинации. С учетом этой информации на выходах блока 19, соединенных с входами блока 9, формируется такой код коррекции, которьй, записываясь в регистр 9, приводит к п формированию двоичной кодовой комбинации, отличаняцейся от исходной в разряде,номер которого соответствует номеру наименьшего символа исходной комбинации.При этом откорректированная комбинация записывается в регистр 9 кодом коррекции из блока

емое устройство позволяет принимать в целом паритетные сигналы. : Технические преимущества изобретения по сравнению с базовым объектом заключаются в том,что приемник полностью использует корректирующие свойства кодов .с проверкой на четность для исправления ошибочно при|нимаемых паритетных сигналов;Кроме того,предлагаемое устройство проще ; известного, так как не содержит блок памяти и вычислительный блок.. 19 и с выходов регистра 9 подается в. анализатор 14. Если в результате анализа окажется, что вес исходной кодовой комби.нации четный, то она по управляющему сигналу из блока 14 в блок 9 считывается на выход устройства, после чего на выходе анализатора 14 формируется сигнал Общий сброс, по которому все элементы памяти устройства приводятСя в исходное состояние. В противном случае (вес комбинаций нечетный) койбинация продолжает храниться в регистре 9.. Далее с помощью генератора 17 на:чинается повторное считывание информации из блока 3 памйти только на вход логического блока 7 (ключ 6 закрыт) . Все описанные операции повто:ряются до тех пор, пока в регистр 9 . не будет записана двоичная кодовая комбинация с четным весом. После ее вьдачи на выход устройства все элементы памяти возвращаются в исходное состояние по сигналу Общий сброс из анализатора 14. Приемник готов к обработке следующего избыточного паритетного сигнала. В отличие от известного предлагаJCvTl

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152017A2 |

| Устройство для мажоритарного декодирования в целом | 1984 |

|

SU1243101A1 |

| Устройство для преобразования кодов в системе передачи данных | 1982 |

|

SU1086449A1 |

| Устройство для приема и обработки избыточной информации | 1983 |

|

SU1140141A1 |

| Устройство для приема избыточных сигналов | 1989 |

|

SU1695353A1 |

| Устройство для приема избыточной информации | 1984 |

|

SU1167638A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

1. УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ С ИЗБЫТОЧНОСТЬЮ, содержащее демодулятор, вход которого является входом устройства,, выход демодулятора соединен через аналого-цифровой преобразователь с первым входом блока памяти, генератор тактовых импульсов, выход которого соединен с входами первого и второго счетчиков, выходы первого счетчика соединены с соответствующими первыми входами первого блока ключей,, выходы которого соединены через первый регистр .с соответствующими первыми входами второго блока ключей, выход второго счетчика соединен с вторым входом второго блока ключей, выходы которого соединены через последовательно соединенные дешифратор и второй регистр с соответствующими первыми входами блока коррекции символов, первые выходы блока коррекции символов соединены с соответствующими первыми входами третьего регистра, и ключ, отличающееся тем, что, с целью упрощения устройства, в. него введены Пороговый блок, анализатор, элемент задержки,бл9к запуска генератора.- тактовых импульсов и логический блок, первые выходы рлока памяти соединены с соответствующими первыми входами блока запуска генератора тактовых им, пульсов, второй выход - с первым входом логического блока,и через пороговый блок с первым входом ключа, выход ключа соединен с вторым входом третьего регистра и первым входом анализатора, первый вькод и второй вход анализатора соединены соответственно с третьим входом и первым выходом третьего регистра, второй выход анализатора соединен с вторым г входом ключа, третий выход - с вторым входом блока запуска генератора тактовых импульсов, четвертьй выход анализатора является выходом устройства, вторые выходы третьего регист§ ра соединены с соотвётствукицими третьими входами анализатора и вторыми входами блока коррекции символов, вторые выходы блока коррекции символов соединены с соответствующими четвертыми входами анализатора,, вторыми входами блок-а памяти и третьими входаьш блока запуска генератора тактовых импульсов, выход блока запуска генератора тактовых импульсов соединен с входом генератора тактовых импульсов, -выход которого соединен через элемент задержки с третьим входом блока памяти, выход второго счетчика соединен с четвертым входом блока запуска генератора тактовых импульсов и вторым входом логи . ческого блока - , выход которого соединен с , вторым входом первого блока ключей .

Jt

Фиг.5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бородин Л.Ф | |||

| Введение в теорию помехоустойчивого кодирования | |||

| М., Советское радио, 1968, с.-270, рис.3.03 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 967137, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1984-12-07—Публикация

1983-08-29—Подача