Изобретение относится к вычислительной технике и может быть использовано в контрольно-измерительных, информационных и радиотехнических системах различного назначения.

Известны аналого-цифровые преобразователи, построенные по методу поразрядного уравновешивания. Устройство включает преобразователь кода в напряжение (ПКН), компаратор и устройство управления, причем на один вход компаратора подается входное напряжение, другой вход подключен к выходу ПКН, входы ПКН соединены с Выходами устройства управления, на вход устройства управления поступает сигнал с выхода компаратора ij .

Недостатком данного устройства является малая величина динамического диапазона входного сигнала.

Наиболее близким к предлагаемому является аналого-цифровой преобразователь поразрядного уравновешивания, который содержит регистр последовательного приближения (РШ), источник тактовых импульсов, источник запускающего импульса, компаратор и цифро-аналоговый преобразователь (ЦАП), причем выходы регистра последовательных приближений подключены к выходам ЦАП, первый и второй входы РПП подключены к генератору тактовых импульсов и генератору запускающих импульсов соответственно, а также к входу компаратора. Первый вход компаратора соединен с выходом ЦАГ1, а второй подключен к входной шине 2j ,

Недостатком известного устройства является малый динамический диапазон входного сигнала.

Цель изобретения - расширение динамического диапазона преобразуемого сигнала.

Поставленная цель достигается тем что в аналого-цифровой преобразователь, содержащий регистр последовательных приближений, цифро-аналоговый преобразователь, генератор тактовых импульсов, генератор запускающих импульсов и компаратор, первый вход которого подключен к входной шине, второй вход - к выходу цифроаналогового преобразователя, входы которого соединены с соответствующими выходами регистра последовательных приближений, первьш и второй входы которого подключены к выходам генератора тактовых импульсов и генератора запускающих импульсов соответственно, введены первый и второй дополнителЫ1ЫС компараторы, первый и второй элементы И, элемент гШИ

инвертор, распределитель кодов, источник порогового уровня и масштаЭирующий усилитель вход которого соединен с входной шиной, а выход - с первыми входами первого и второго дополнительного компаратора, второй вход первого дополнительного компаратора соединен с источником порогового уровня, а второй вход второго дополнительного компаратора соединен

с выходом цифро-аналогового преобразователя, при этом выходы компа эатора и второго дополнительного компаратора соединены соответственно с первьми входами первого и второго

элементов И, второй вход второго элемента И через инвертор подключен к выходу первого дополнительного компаратора, первому входу распределителя кодов и второму входу первого

элемента Невыход которого соединен с первым входом элемента ИЛИ, BTOpofi вход которого соединен с выходом второго элемента И, а выход - с тр етьим входом регистра последовательных приближений, выходы которого соединены соответственно с вторыми входами распределителя кодов.

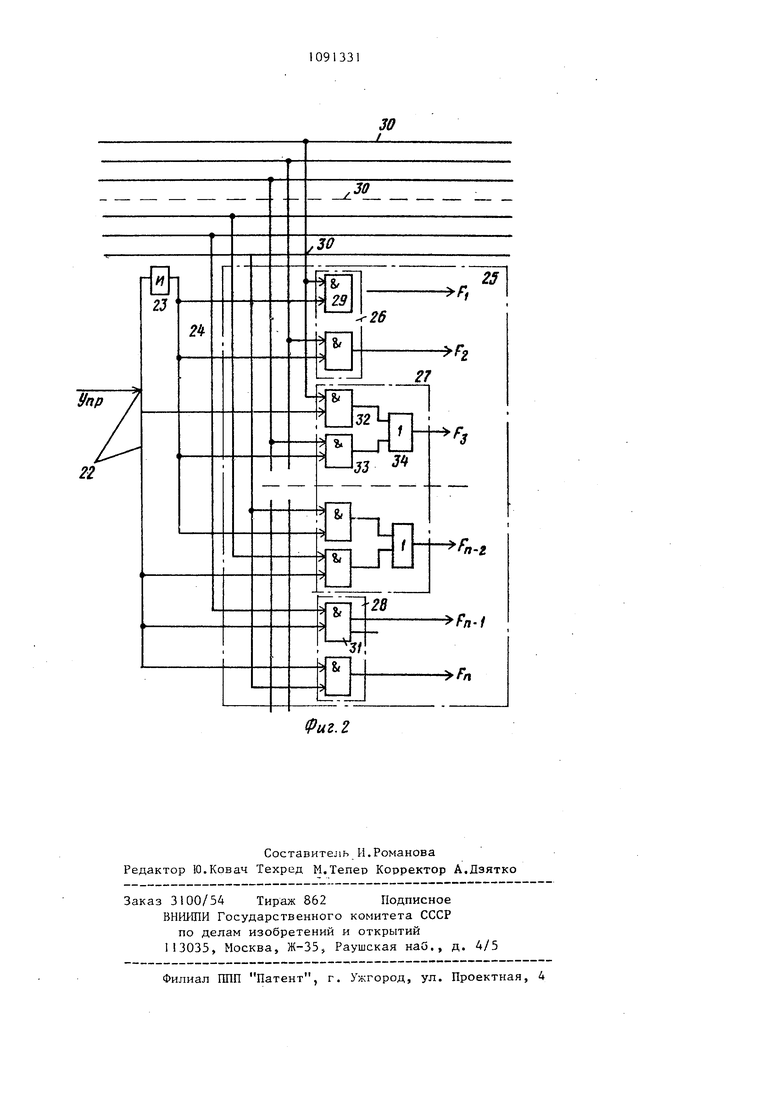

На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг.2распределитель кодов (вариант.

Входная шина I соединена с входом компаратора 2 и входом масштабирующего усилителя 3, к управляющим входам регистра 4 последовательных приблнжений подключены генератор 5 тактовых импульсов и генератор 6 запускающих импульсов, вькод масштабирующего усилителя подключен к первым входам.первого и второго дополнительных компараторов 7 и 8, вторые входы основного и второго дополнительного компараторов соединены с зыходом ЦАП 9, второй вход первого Д1Эполнительного компаратора соединен с

источником 0 порогового уровня, выход, первого дополнительного компаратора соединен с входом инвертора II, а также с первым входом первого элемента И 12, первый вход второго элемента И 13 подключен к выходу инвертора 11, выход первого дополнительного компаратора 7 соединен с управляющим входом распределителя 4 кодов, вторые входы первого и второго элементов И 12 и I3 подключены соответственно к выходам компаратора 2 и второго дополнительного компаратора 8, выходы первого и второго элементов И 12 и 13 соединены с входами элемента ИЛИ 15, выход которого подключен к информационному входу регистра 4, выходы регистра 4 соединены с информационными входами рас пределителя 14 кодов, выходы распределителя кодов подключены к выходной шине 16, вход первого дополнительного компаратора подключен к шине I 7 строба. Усилитель 3 состоит из резисторного делителя 18, состоящего из резисторов 19 и 20, и усилителя 21, входы резисторного делителя соединены с выходом усилителя и общей точ кой, выход подключен к инвертирующему входу усилителя 21, неинвертирующий вход подключен к входной шине 1 . Управляющая входная шина 22 подключена к входу инвертора 23 управления , выход которого соединен с управляющей шиной 24. Формирователь 25 выходного кода состоит из формирователей 26-28 младших, средних и старших разрядов соответственно. Формирователь младших разрядов, в свою очередь, состоит из К отдельных двухвходовых элементов И 29 (к - коэффициент масштабирования, в рассмат риваемом примере ), один вход которых подключен к управляющей выходной шине 24, а другой соединен с одной из младших шин, входящих в шину 30 входного кода. Формирователь стар ших разрядов состоит из К отдельных двухвходовых элементов И 31, один из входов которых подключен к управляющей входной шине, а другой соединен с одной из шин старших разрядов входящих в шину 30. Формирователь ко да средних разрядов состоит из п-2К отдельных формирователей, каждьй из которых включает первый 32 и второй 33 дополнительные элементы И, выходы которых подключены к входам дополнительного элемента ИЛИ 34, первый вход первого дополнительного элемента И соединен с (1-2)-й шиной- входного кода, где i - номер разряда выходного кода, второй вход первого дополнительного элемента И 32 подключен к входной управляющей шине, первьш вход второго дополнительного элемента И 33 соединен с 3314 входом i-й шины 30 входного кода, второй вход второго дополнительного элемента И 33 соединен с управляющей выходной шиной 24. Устройство работает следующим образом. Фрагмент схемы, состоящий из входной шины 1, компаратора 2, первого элемента И 12, элемента ИЛИ 15, регистра 4 последовательных приближений, ЦАП 9, генератора 5 тактовых импульсов и генератора 6 запускающих импульсов, представляет собой известную схему АЦП поразрядного уравновешивания. Дополнительными по сравнению с известной схемой здесь являются первый элемент И 12, и элемент ИЛИ 13, однако здесь будем полагать, что на первый вход первого элемента И 12 с выхода первого дополнительного компаратора 7 подается логическая единица т. к, что сигнал с выхода компаратора 2 беспрепятственно проходит через указанные элементы И и ИЛИ на информа ционный вход регистра 4. Указанный Фрагмент схемы работает как классический АЦП поразрядного уравновешивания. Функционирование происходит под действием управляющих импульсов регистра последовательных приближений. В каждом такте регистр 4 вырабатывает код типа 10...О или 011.,. в зависимости от принятой логики. Сигнал с выхода компаратора 2 с приходом тактового импульса устанавли- . вает старш ш разряд регистра в О или 1 в зависимости от того, сработал или нет компаратор 2, одновременно устанавливается в нуль следующий по старшин ству разряд регистра. С приходом очередного тактового импульса определяется цифра во втором разряде и устанавливается единица в третьем разряде и т.д. По заполнению регистра завершается цикл преобразования, разряды регистра блоки- i руются по входам и информация хранится до начала нового цикла. В исходное состояние регистр приводится соответствующим сигналом с выхода генератора запускающих импульсов. Фрагмент схемы, состоящий из масштабирующего усилителя, второго дополнительного компаратора, второго элемента И, элемента Ш1И, регистра, генератора тактовых импульсов, генератора запускающих импульсов и ЦАП, представляет собой также схему поразрядного уравновешивания здесь полагается, что с выхода первого дополнительного компаратора снимается нулевой сигнал так, что выходной сигнал второго дополнительного компаратора через второй элемент И и элемент ИЛИ беспрепятственно прохода1т на информационный вход регистра). Отличие второго фрагмента схемы от лервого заключается в том, что входной сигнал ус танавливается масштабирующим усилителем в К раз. Таким образом, величина кванта q второго фрагмента в К раз меньше, чем у первого - q. Соответственно верхняя граница диапазона входной величины у второго фрагмента (и|„о) оказывается в К раз меньше, чем у первого ( ).

При работе АЦП диапазон входного сигнала делится на два jniacTKa Д1 и Д2. Участок Д1 соответствует малым значениям входного сигнала от О до , участок Д2 - большим значениям от lima fio ,.

Пороговый уровень, поступда вд1Й от источника 10 порогового уровня, ра- : вен UIYIOX Таким образом, если выходной сигнал находится в пределах диапазона Д1, то компаратор 7 не сработает, первый элемент И блокирует сигнал компаратора и на информационный вход регистра поступает сигнал второго дополнительного компаратора т.е. работает второй фрагмент схемы.

Код, полученный в результате преобразования, записывается на выходе регистра и с помощью распределителя кодов подается на п младших шин выходного кода устройства, где п - :количество разрядов первого и второго фрагментов. На остальные старшие разряды выходного кода при помощи схемы распределителя кодов подаются нули. Если же входной сигнал находится з пределах диапазона Д2, то компаратор 7 сработает, второй элемент И 13 заблокируется, а первый элемент И 12 откроется. В зтом случае будет работать первый фрагмент схемы, выходной код с выхода регистра подается на k-n старших шин выходной шины, при этом на п остальных младших шин подается нуль. Чтобы сигнал с выхода компаратора в процессе преобразования не менял своего значения, он фиксируется подачей строб-импульса.

Технико-экономический эффект заключается в том, что предлагаемая схема позволяет на базе разрядного АЦП поразрядного уравновешивания получить n+KL-разрядный преобразоватехи, который при больших значениях сигка- ла имеет квант аналогичен прототипу, а при малых - в К раз меньше, кроме того, по сравнению с прототипом существенно расширяется динамический диапазон входного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1981 |

|

SU945977A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1358094A1 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1499495A1 |

| Цифровой стробоскопический преобразователь электрических сигналов | 1983 |

|

SU1087895A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1410271A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий регистр последовательных приближений, цифро-аналоговый преобразователь, генератор тактовых импульсов, генератор запускающих импульсов и компаратор, первый вход которого подключен к входной шине, второй вход - к выходу цифро-аналогового преобразователя, входы которого соединены с соответствую щими выходами регистра последовательных приближений, первый и второй входы которого подключены к выходам генератора тактовых импульсов и генератора запускающих импульсов соответственно, о тли ч ающийс я тем, что, с целью расширения динамического диапазона преобразуемого сигнала, в него введены первый и второй дополнительные компараторы, первый и второй элементы И, элемент ШШ, инвертор, распределитель кодов, источник порогового уровня и масштабируюш 1й усилитель, вход которого соединен с входной шиной, а выход - с первыми входами первого и второго дополнительного компаратора, второй вход первого дополнительного компаратора соединен с источником порогового уровня, а второй вход второго дополнительного компаратора соединен с выходом цифро-аналогового i преобразователя, при этом выходы компаратора и второго дополнительного (Л компаратора соединены соответственно С с первыми входсШи первого и второго элементов И, второй вход второго элемента И через инвертор подключен к выходу первого дополнительного компаратора, первому входу распределителя кодов и второму входу первого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй х вход которого соединен с выходом второго элемента Ы, а выход - с третьим 2 входом регистра последовательных jO приближений, выходы которого соедине-i ны соответственно с вторыми входами распределителя кодов.

I

f- & S

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых вычислительных устройств | |||

| М., Энергия, 1970, с.309 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

Авторы

Даты

1984-05-07—Публикация

1982-07-14—Подача