Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ.

Цель изобретения - повышение производительности устройства.

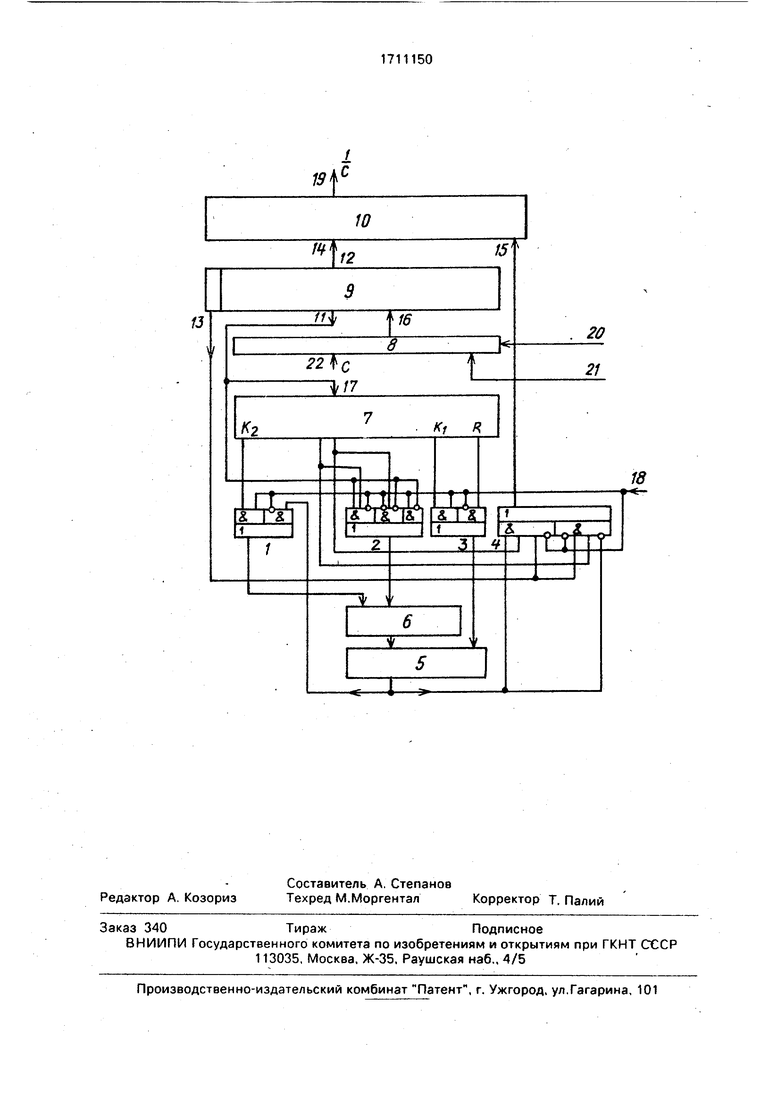

На чертеже представлена структурная схема устройства для вычисления обратной

величины.;Г

-Устройство содержит коммутаторы 1-4,, сумматор 5, умножитель 6, шифратор 7 на- чального приближения, входной регистр 8, блок 9 нормализации и сдвигатель 10. Блок

9нормализации содержит информационный выход 11, выход 12 кода величины сдвига, выход 13 старшего разряда, сдвигатель

10имеет управляющий 14 и .информационный 15 входы, входной регистр 8 имеет выход 16; шифратор 7 содержит вход 17 и выходы 18-22. Устройство имеет также управления, сброса, разрешения записи, вход операнда и выход результата.

Устройство осуществляет итеративный алгоритм деления. При этом за счет радиального выбора структуры шифратора начального приближения удается число итераций для получения необходимой точности до 1-2 при 16-32 разрядных операндах.

Устройство осуществляет вычисление по формуле

-i (Ki + K2-C)C + R.

V-

где С - исходный операнд;,

Ki, «2, R - коэффициенты, формируемые

шифратором начального приближения. В зависимости от значения С или вся

величина - и/или С перед умножением на

v

(Ki + Кг-С) инвертируется.

сл о

Устройство работает следующим образом.

На его вход 26 поступает целое число (для примера рассмотрим 16-разрядные числа), которое запоминается в регистре 8 по сигналу на входе 25 разрешения записи. Далее входной операнд поступает в блок 9 нормализации, где сдвигается в сторону старших разрядов до появления 1 на выходе 13 старшего разряда. Код величины сдвига запоминания передается на выход 13 для последующей денормализации в сдвигателе 10. 15-разрядный нормализованный операнд С поступает в шифратор 7 и на коммутатор 2. При единичном потенциале на входе 23 осуществляется вычисление (Кг -C+Ki), а при нулевом - второе умножение полученного результата на С и добавле- ние R. Выходы 19 и 20 шифратора определяют необходимость инвертирования С при втором умножении и общего инвертирования результата при его передаче с выхода сумматора 5 через коммутатор 4 в сдвигатель 10, Старший разряде выхода 13 приформировывается к полученному результату на коммутаторе 4.

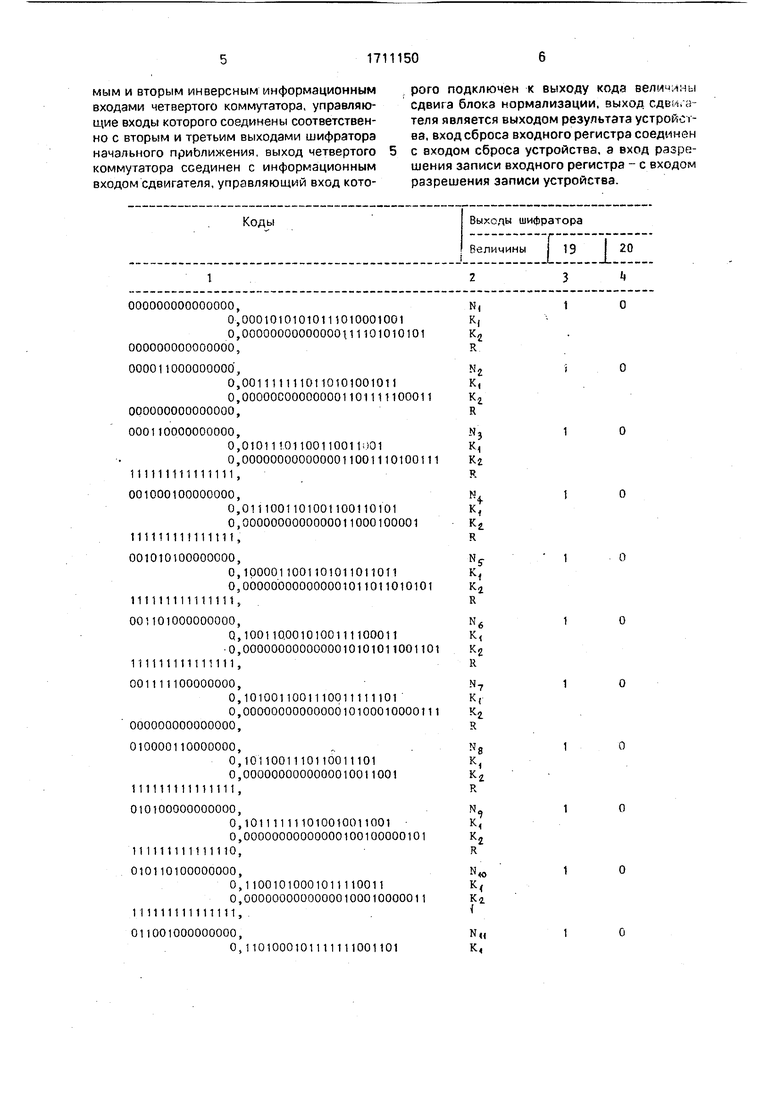

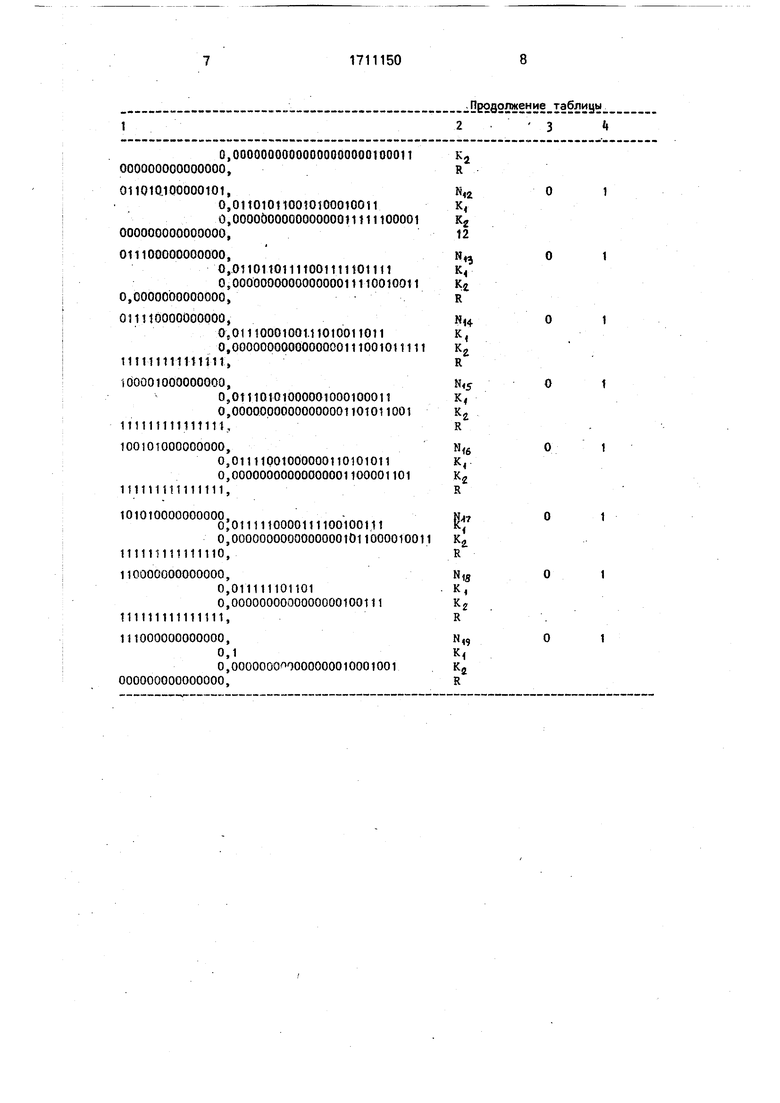

Шифратор 7 начального приближения построен на базе ПЗУ. Для 16-разрядных операндов он имеет 7-разрядный вход 17. Шифратор построен в соответствии с таблицей. Он осуществляет шифрацию величин Ki, K2, R и условий инвертирования в зависимости от принадлежности входного кода соответствующей зоне (всего 19 зон).

Пример. Пусть С 0000101010010111, 010100101110000 - на выходе 11 блока нормализации, 0101001 - на входе 17 шифратора 7.

Согласно таблице входной код на входе 17 попадает в зону Ng, т.е. Ng - ближайшее большее число; тогда на выходе 19- 1, на выходе , величины4 Ki, Ка, и R будут соответственно 0,101111111010010011001 ; 0.000 000 0000 Об ОО 10 001 00 000-11: 111111111Ш110.

По 1 на входе устройства инверсия нормализованного С без старшего разряда через третий инверсный вход второго коммутатора проходит на второй вход умножителя и умножается на Ка.

Результат +0,11000011001011011111 001011 суммируется с Ki и с выхода сумматора 1,10000.010110100101011101011 поступает на второй вход первого коммутатора, до прихода О, на вход устройства.

Далее 010100101110000, нормализованное С в прямом коде, через первый вход второго коммутатора проходит на второй вход умножителя и умножается на

1,10000010110100101011101011 с выхода коммутатора 1.

Далее результат суммируется с величиной R, инвертируется на коммутаторе 4 и

объединяется С 1 в старшем разряде. Полученный результат 0,1100000101100101 поступает на сдвигатель. где сдвигается на 11 разрядов. Окончательно получается результат 1/С 0,000000000001100000101100101

на выходе устройства.

Формула изобретения Устройство для вычисления обратной величины, содержащее входной регистр,

умножитель, шифратор начального приближения, первый и второй коммутаторы и сумматор, причем выходы первого и второго коммутаторов соединены с первым и вторым входами умножителя соответственно,

первый информационный вход первого коммутатора соединен с первым выходом шифратора начального приближения, вход, входного регистра соединен с входом операнда устройства, отличающ ее с я тем,

что, с целью повышения производительности, устройство дополнительно содержит блок нормализации, сдвигатель, третий и четвертый коммутаторы, причем выход входного регистра соединен с входом блока нормализации, разряды информационного выхода которого, кроме старшего разряда, соединены с соответствующими разрядами входа шифратора начального приближения, а также с разрядами первого прямого, второго и третьего инверсных информационных входов второго коммутатора, первый и второй управляющие входы которого соединены соответственно с вторым и третьим выходами шифратора начального приближения, третий управляющий вход второго коммутатора подключен к управляющему входу устройства, первый и второй инверсные стробирующие входы второго коммутатора соединены с управляющим входом устройства, с первым прямым и вторым инверсным управляющими входами первого и третьего коммутаторов, а также с первым и вторым инверсными стробирующими входами четвертого коммутатора, третий и четвертый стробирующие входы которого подключены к выходу старшего разряда блока нормализации, выход умножителя соединен с первым входом сумматора, второй вход которого подключён к

выходу третьего коммутатора, информационные входы которого соединены с четвертым и пятым выходами шифратора начального приближения, выход сумматора соединен с вторым информационным входом первого коммутатора и с первым прямым и вторым инверсным информационным входами четвертого коммутатора, управляющие входы которого соединены соответственно с вторым и третьим выходами шифратора начального приолижения, выход четвертого коммутатора соединен с информационным входом сдвигателя, управляющий вход которого подключен к выходу кода величины сдвига блока нормализации, выход сдвигателя является выходом результата устройства, вход сброса входного регистра соединен с входом сброса устройства, а вход разрешения записи входного регистра - с входом разрешения записи устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Операционное устройство | 1985 |

|

SU1367012A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Цель изобретения - повышение производительности устройства. Цель достигается введением в устройство. Содержащее регистр, умножитель, шифратор начального приближения, первый и второй коммутаторы и сумматор, блока нормализации, сдвигателя, третьего и четвертого коммутаторов, а также новых связей. Устройство осуществляет вычисление обратной величины по итеративной формуле с использованием двух умножений для получения 16-разрядного результата. Производительность повышается благодаря уменьшению числа итерации для получения результата с требуемой точностью. Для этого шифратор начального приближения генерирует три коэффициента и два условия инвертирования. 1 ил.. 1 табл.

0,000000000000001101111100011Кг

000000000000000,R

000110000000000,Я3

0,010111.011001 J00.11001К,

0,0000000000000011001110100111Кг

111111111111111,R

001000100000000,N ч

0,0111001101001100110101К,

0,0000000000000011000100001К

111111111111111, :R

001010100000000,N50,1000011001101011011011Kj

0,000000000000001011011010101К2

111111111111111,R

001101000000000,N6

0,100110.0010100111100011К1 0,0000000000000010101011001101 , К2

111111111111111,R

001111100000000,N7

0,1010011001110011111101к,0,0000000000000010100010000111К2

000000000000000,R

010000110000000,„ .Ng

0,10 11001110116011101K4

0,0000000000000010011001К 2

111111111111111,R

010100000000000,К,,

0,101111111010010011001К,

0,00000000000000100100000101K2

111111111111110,R

010110100000000,NW

0,11001010001011110011Kf

0,00000000000000100010000011K4

111111111111111, - .

011001000000000,-NM

0,1101000101111111001101K,

0

0

„„...iQB2a9{ $St S- §§2H KL.

tг з

0,00000000000000000000100011K2

pooooooooooodoo,R

0,011010110010100010011Kf

0,000060000000000011111100001кг

000000000000000,12

011100000000000,N«01

0,.011011Q1111001111101111Kf

0,000600000000000011110010011Kz

o.ooooobooooooo,R

011110000000000,NH01

0,01110001001.11010011011k.

0,0000000000000000111001011111K,

111111111111111:,R

100001000000000,N45 0 1

0,01110101000001000100011R«

0,00000000000000001101011001Кг

11П11111111111,R100101000000000, 0 - 1

0,01111001000000110101011Kr

0,00000000000000001100001101K2

111111111111111,R

101010000000000,--.-NJT 0 1

O. O111110000111100100111K7

0,00000000000000001011000010011 K4 111111111111110,R

110000000000000,Ntf 0 1

0,011111101101. К4

0,0000000000000000100111K2

111111111111111,R .

111000000000000,Nw . 0 1

0,1K4

0,000000000000000010001001Ka

000000000000000,R

| Гаврилов Ю.В., Пучко А.Н | |||

| Арифметические устройства быстродействующих ЭЦВМ | |||

| М.: Советское радио | |||

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| с | |||

| Переносное устройство для вырезания круглых отверстий в листах и т.п. работ | 1919 |

|

SU226A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Прангишвили И.В., Абрамова Н.А | |||

| и др | |||

| Микроэлектроника и однородные структуры для построения логических и вычислительных устройств | |||

| М.: Наука | |||

| Запальная свеча для двигателей | 1924 |

|

SU1967A1 |

| Переносная мусоросжигательная печь-снеготаялка | 1920 |

|

SU183A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-02-07—Публикация

1989-03-23—Подача