1

Изобретение относится к средствам контроля цифровы объектов и может быть использовано для проверки правильности работы интегральных схем при контроле объектов, содержащих такие схемы, а также для .моделирования (имитации) их леисиравностей при подборе и проверке эффективности тестов цифровых объектов.

Известны устройства для контроля неисправностей интегральных схе.м, установленных в различных цифровых объектах 1, 2, 3 и 4.

Эти устройства обеспечивают контроль цифрового объекта поочередной проверкой входяншх в его состав интегральных схем путем сравнения выходных сигналов контролируемой схемы и однотипной эталонной схемы, иа входы которой прикладываются сигналы, снимаемые с входов контролируемой интегральной схемы объекта, при этом объект либо находится в режиме нормального функционирования, либо на его входы прикладываются контрольные сигналы от отдельного генератора тестов.

Недостатком известных устройств является ограниченность функций.

Наиболее близким но технической сущности является устройство для контроля неисправностей интегральных схем, содержащее эталонную схему, блок контактирования и

связанные с ним развязывающие усилители и дискриминаторы потенциалов, блок сравнения, входы которого связаны с дискриминаторами потенциалов, и соединенный с блоком сравнения блок регистрации 5.

Недостатком этого устройства является невозможность его применения прн решении других задач, связанных с контролем цифровых объектов, в частности при подборе и .проверке качества тестов функционального контроля обтзектов.

С целью моделирования nencnpaBHocTcii интегральных схем в него введены входные и выходные вентили, последовательно соединенные счетчик и дешифратор, причем входные вентили включены между выходами развязывающих усилителей и входом эталонной схемы, выходные вентнли - между выходом эталонной схемы и входом блока сравнения, выходы выходных вентилей связаны с блоком контактирования, а вторые входы входных и выходных вентилей подключены к выходу дешифратора, выход счетчика соединен с блоком регистрации, который связан также с выходами дискриминаторов потенциалов.

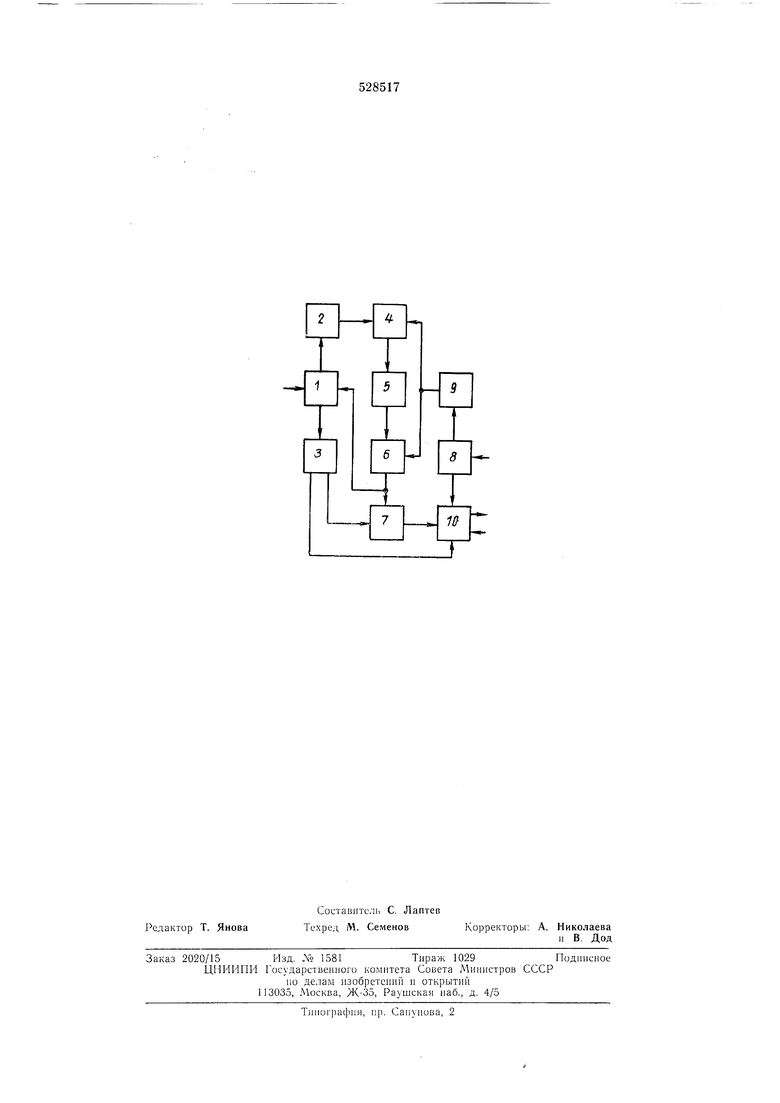

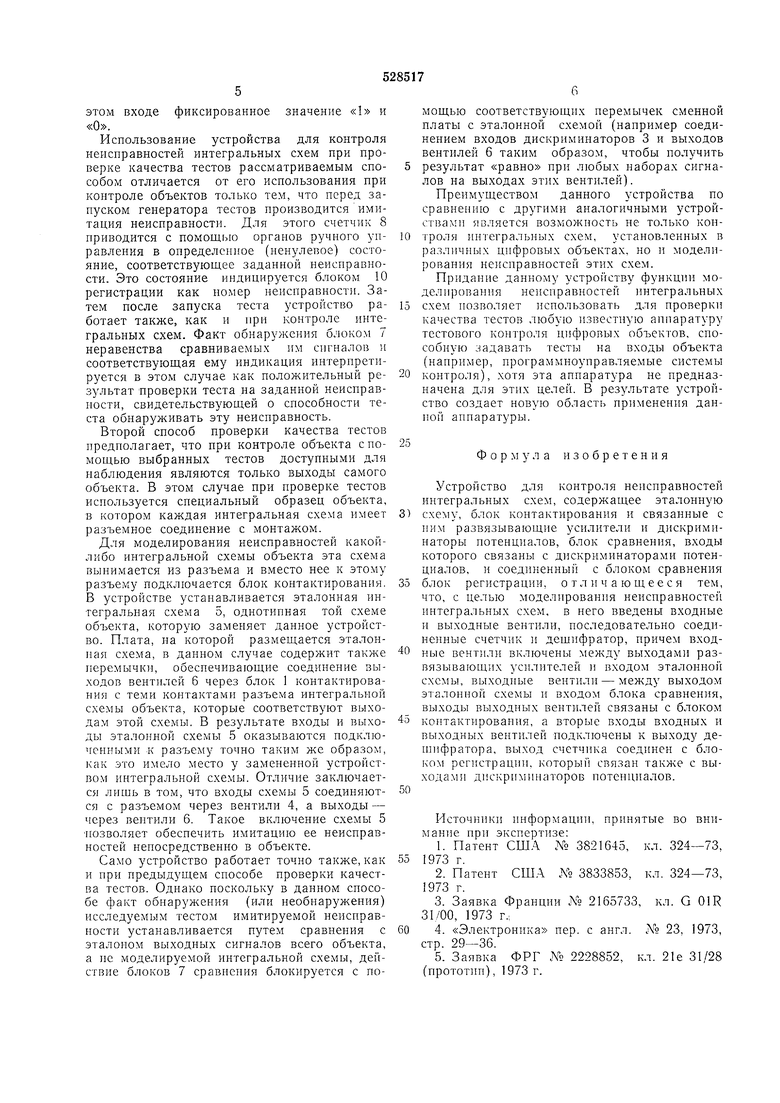

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство содержит блок 1 контактировання, развязывающие усилители 2, дискриминаторы 3 потенциалов, входные вентили 4.

эталонную схему 5, выходные вентили 6, блок 7 сравнения, счетчик 8, дешнфратор 9 и блок 10 регистрации.

При номощи блока 1 коитактирования устройство нодключается к внешним выводам интегральных схем объекта контроля или соединяется с монтажол объекта в тех случаях, когда оно включается вместо какой-либо ннтегральной схел1ы. Блок 1 связан с входами развязывающнх уснлнтелси 2 и дискриминаторов 3 нотенциалов. Те и другие элементы служат для снижения иагрузки на цеии обьекта, к которым иодключаегся ycTpoiicTBo. а дискрил1инаторы 3 потенциалов, кроме того. обесценивают распознавание логических значений «1 н «О сигна,;ов на выходах контролируемой интегральной схемы. Быхо;1Ы развязывающих усилителей 2 соединены с нервыми входами входных вентилей 4, нредназначенных для имитации обрывов входов и других цеисправностей интегральных схем. Вентили 4 связаны е входами эталонной схемы 5, выходы которой нодключены к нервым входам выходных вентилей 6. Эти вентцли служат для имитации неисцравностей выходов интегральных схем (фиксированное значение «1 или «О на выходе). Выходы вентилей 6 соединены с блоком 1 контактирования и с входами блока 7 сравнения, другие входы которого связаны с дискриминаторами 3 нотецциалов.

Счетчик 8 слул.ит для образования н запоминания кода (номера) имитируемой неисцравности. Изменение состояния этого счетчика обеспечивается „тибо е помоиило оргаио 5 ручного управления, либо по сигналам от внешней аппаратуры, совмеспш с которой используется устройство. Выходы счетчика 8 через дешифратор 9 соедппеиы с вторыми входами вентилей 4, 6.

Блок 10 регистрации предназначен для nriдикации результатов сравнения выходных сигналов контролируемой интегральной схемы ц эталонной ехемы 5, результатов допускового контроля выходных сигналов пнтегральцой схемы, номера имитируемой ненсправпости, а также для формирования сигналов управления внешней аинаратурой. Входы блока 10 регистрации связаны с выходами дискримннаторов 3 потенциалов, блока 7 сравнения и счетчика 8.

Для обеспечения контроля и моделирования пепсправностей различных нптегральпых схем объектов эталонная схема должна быть сменной. В простейшем случае в качестве эталонной схемы может иецользоваться интегральная схема того же тина, что и контролируемая схема объекта. Эталонные интегральные схемы устанавливаются па платах.

Устройство работает следующим образом.

При контроле интегральных схем чакоголибо объекта блок 1 контактирования нодключается к внешним выводам выбраиной интегральной схемы, нрн этом в устройстве устанавливается соответствующая эталонна и

схема 5. Затем с помощью органов ручного управления счетчик 8 н блок 10 регнстрации сбрасывается в исходное состояние (нули во всех разрядах). После этого к контролируемому устройству нрнкладывается тест. При нулевом состоянии счетчика 8 неисправности не имитируются, поэтому сигналы, действующие в процессе выполнения теста на входах проверяемой нптегральпой схемы, через блок

1 контактнровапия, развязывающие усилители 2 и входпые вентили 4 без каких-либо из-меиеннй нрикладываются к входам эталонНой схемы 5.

Блок 7 сравнения в каждом такте теста

сравнивает выходные сигналы этой схемы, поступаюпи-к также без какнх-;1нбо изменений через выходные вентили 6, с выходными сигналами дискриминаторов 3 потенциалов, логические значения которых совнадают с

значениями выходных сигналов контролируемой интегральной схемы. Если в некотором такте теста блок 7 обнаруживает неравенство значений хотя бы на одной паре одноименных выходов обеих схем, то этот факт фикеируется блоком 10 регистрации и индицируется соответствующей лампой этого блока как неправильное функционирование контролируемой схемы (логическая неисправность). Если в каком-либо такте дискриминаторы 3

обнаруживают отклонение нотенциала на каком-нибудь выходе к:оптролпруемой интегральной схемы, то блок 10 ф1 ксирует и индицирует параметрическую неисправность схемы.

Проверка качества тестов для цнфровых объектов с пснользованием устройства для контроля неиснравпостей интегральных схем может выполняться двумя снособамп.

Первый них нредпазначен для того слу4i r,, когда нрн KOHipo.ie объекта с помони,ю 1(|)1бпанных i-CCTOt ДОСТУПНЫМИ д.чя наблюдения являются все выходы его интегральных схем (например, и с.лучае контроля объекта с ПОМОН1ЫО да1П101о устройства). Проверка

1-еста ,ест1;,1яется на .побом заведомо псправ1 ом образце обьекта, а данное устройство обеснечи: ает дтоде,1пр;) поведения его пптсгр;к:пл1ых схем при паличин неисправностей н сра 5нение выходных снгналов выбранной нпте1ральпой схемы объекта п схемымодели.

Фупкцпп схемы-модели для выбранно); интегральной схемы объекта, неиснравностн которой нмитируются с помощью данного устройства, выполняет однотипная ей эталонпая схема 5 вместе с входпыми и выходными вентилями 4, 6. Например, для имитации ненсправности Tinia «обрыв входа, с помощью cooiiiCTCTBXMOHiero входного вептнля этот вход

схемы 5 отключается от управляюн1его им раз15язываюн1его уснлнтеля. Если имитируется неиснравность тппа «неизменное значение «1 или «О выхода, то соответствуюи1ий выходной вептнль отключает этот выход схемы

5 от нхода блока 7 сравпепия О и задает иа

этом входе фиксированное значение «I и «О.

Использование устройства для контроля неисправностей интегральных схем при проверке качества тестов рассматриваемым способом отличается от его использования при контроле объектов только тем, что перед запуском генератора тестов производится имитация неисправности. Для этого счетчик 8 приводится с помощью органов ручного управления в определенное (ненулевое) состояние, соответствуюш,ее заданной неисправности. Это состояние индицируется блоком 10 регистрации как номер неисправности. Затем после запуска теста устройство работает также, как и при контроле интегральных схем. Факт обнаружения блоком 7 неравенства сравниваемых им сигналов и соответствуюш,ая ему индикация интерпретируется в этом случае как положительный результат проверки теста на заданной неисправности, свидетельствующей о способности теста обнаруживать эту неисправность.

Второй способ проверки качества тестов предполагает, что при контроле объекта с помощью выбранных тестов доступными для наблюдения являются только выходы самого объекта. В этом случае при проверке тестов используется специальный образец объекта, в котором каждая интегральная схема имеет разъемное соединение с монтажом.

Для моделирования неисправностей какойлибо интегральной схемы объекта эта схема вынимается из разъема и вместо нее к этому разъему подключается блок контактирования. В устройстве устанавливается эталонная интегральная схема 5, однотипная той схеме объекта, которую заменяет данное устройство. Плата, на которой размещается эталонпая схема, в данном случае содержит также перемычки, обеспечивающие соединение выходов вентилей 6 через блок 1 контактирования с теми контактами разъема интегральной схемы объекта, которые соответствуют выходам этой схемы. В результате входы и выходы эталонной схемы 5 оказываются нодключенными к разъему точно таким же образом, как это имело место у замененной устройством интегральной схемы. Отличие заключается лищь в том, что входы схемы 5 соединяются с разъемом через вентили 4, а выходы - через вентили 6. Такое включение схемы 5 позволяет обеспечить имитацию ее неисправностей непосредственно в объекте.

Само устройство работает точно также, как и при предыдущем способе проверки качества тестов. Однако поскольку в данном способе факт обнаружения (или необнаружения) исследуемым тестом имитируемой неисправности устанавливается путем сравнения с эталоном выходных сигналов всего объекта, а ПС моделируемой интегральной схемы, лействие блоков 7 сравнения блокируется с помощью соответствующих перемычек сменной платы с эталонной схемой (например соединением входов дискриминаторов 3 и выходов вентилей 6 таким образом, чтобы получить результат «равно при любых наборах сигналов на выходах этих вентилей).

Преимуществом данного устройства по сравнению с другими аналогичными устройствами является возможность не только контроля интегральных схем, установленных в различных цифровых объектах, но и моделирования неисправностей этих схем.

Придание данному устройству функции моделирования неисправностей интегральных

схем позволяет использовать для проверки качества тестов любую известную аппаратуру тестового контроля цифровых объектов, способную задавать тесты на входы объекта (нанример, программпоуправляемые системы

контроля), хотя эта аппаратура не предназначена для этих целей. В результате устройство создает новую область нр 1менения данной аппаратуры.

25

Формула изобретения

Устройство для контроля неисправностей интегральных схем, содернсащее эталонную

схему, блок ;онтактирования и связанные с ним развязывающие усилители и дискриминаторы нотенциалов, блок сравнения, входы которого связаны с дискриминаторами потенциалов, и соединенный с блоком сравнения

блок регистрации, отличающееся тем, что, с целью моделирования неисправностей интегральных схем, в него введены входные и выходные вентили, последовательно соединенные счетчик и дещифратор, причем входиые вентили включены выходами развязывающих усилителей и входом эталонной схемы, выходные вентили - между выходом эталонной схемы и входом блока сравнения, выходы выходных вентилей связаны с блоком

контактирования, а вторые входы входных и выходных вентилей подключепы к выходу дещифратора, выход счетчпка соединен с блоком регистрации, который связан также с выходами диcкpи iииaтopoв потенциалов.

Источники информации, принятые во внимание при экспертизе:

1.Патент США № 3821645, кл. 324-73. 1973 г.

2.Патент США №. 3833853, кл. 324-73, 1973 г.

3.Заявка Франции Л 2165733, кл. G 01R 31/00, 1973 г.;

4. «Электроника пер. с англ. N° 23, 1973, стр. 29-36.

5. Заявка ФРГ Л 2228852, кл. 21е 31/28 (прототип), 1973 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля неисправностей интегральных схем | 1980 |

|

SU1083138A1 |

| Устройство для контроля цифровых модулей и проверки качества тестов | 1974 |

|

SU519713A1 |

| Устройство для автоматического контроля цифровых объектов | 1977 |

|

SU656063A1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Устройство для контроля интегральных схем | 1981 |

|

SU1029146A1 |

| Устройство для синтеза тестов | 1980 |

|

SU886003A1 |

| Адаптивное устройство многоточечного контроля | 1974 |

|

SU600484A1 |

| Устройство для контроля интегральных схем | 1975 |

|

SU553618A1 |

| Устройство для контроля логических схем | 1985 |

|

SU1252786A1 |

| Способ и система для контроля радиолокационной станции | 2016 |

|

RU2648585C1 |

Авторы

Даты

1976-09-15—Публикация

1974-02-11—Подача