Изобретение относится к вьгаислительной технике и может быть использовано в устройствах управления СЦВМ лля обеспечения отладки программ.

Известно устройство для отладки программ, содержащее регистр первого перехода, регистр второго перехода, схему сравнения, счетчик команд, дешифратор, блок операций, первый, второй и третий переключатели, регистр команд, первый, второй и третий триггеры, а также первый и второй элементы задержки Cl.

Однако данное устройство не позволяет отлаживать программы, работгиощие в реальном масц1табе времени, так как для контроля хода выполнения программы производится останов, что приводит к потере входной инфОЕЯиации и искажению обрабатываемой информации.

Наиболее близким к предлагаемому является устройство для управления памятью, содержащее регистр адреса команд, блок буферных регистров, распределитель, счетчик, триггер, три элемента И, элемент ИЛИ, элемент задержки, регистр исполнительного адреса, выход которого через первый элемент И соединен с входом регистра адреса команд, выход которого соединен с входом блока буферных регистров, элемент ИЛИ, входы которого соединены с входами устройства, а выход через элемент задержки - с входом первого элемента И, распределитель, два элемента И, счетчик и триггер, причем выходы элемента ИЛИ и триггера соединены через второй элемент И с входами счетчика, блока буферных регистров и распределителя, выходы которого соединены с группой входов блока буферных регистров, выходы которого соединены с группой устройства, выход счетчика и управляющий вход устройства соединены через третий элемент И с первым входом триггера, второй вход ко.торого соединен с входом установки устройства С2.

Недостатком известного устройства является отсутствие возможности формирования сигнала прерывания в любой заданной точке программы, а также фиксации начальной точки (адреса) включения режима контроля (трассировки) за ходом выполнения программы. Кроме того, в таком устройстве отсутствует возможность оперативного изменения количества команд переходов, после выполнения котоЕ«4х вырабатывается сигнал прерывания. Все это уменьшает производительность операторов, ведущих отладку программ

Цель изобретейия - повышение производительности при отлещке программ

Поставленная цель достигается тем, что в устройство для отладки nporpaNW, содержащее регистр исполнительного адреса, регистр адреса команд, блок буферных регистров, распределитель, счетчик, триггер, три элемента И, первый элемент ИЛИ и Элемент задержки, причем выход регистра исполнительного адреса соеди5 иен с первым входом первого элемента И, выход которого соединен с входом регистра адреса команд, выход последнего соединен с информационным , входом блока буферных регистров,

0 входы команд условного и безусловного переходов признака устройства соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первым

5 входом второго элемента И и через элемент задержки с вторым входом первого элемента И, вькод второго элемента И соединен с управляющим входом записи блока буферных регистQ ров и счетньами входами счетчика и распределителя, выходы которого соединены с адресными входами блока буферных регистров, выходы которого являются информационньдми выходами устройства, выход счетчика и первый управляющий вход режима работы устройства соединены соответственно с первым и вторым входами третьего элемента И, выход которого соединен с нулевым входом триггера и являет0 ся первым выходом прерывания устройства, выход триггера соединен с вторьлл входом второго элемента И, введены регистр начального адреса, схема сравнения, два элемента И и второй

5 элемент ИЛИ, причем информационный вход устройства соединен с входом регистра начального адреса и информационным входом счетчика, выход регистра начального адреса соединен с

Q первым входом схемы сравнения, выход регистра адреса команд соединен с Вторым входом схемы сравнения, выход которой соединен с первыми входами четвертого и пятого элементов И, первый и«второй управляющие входы режима работы устройства соединены с вторыми входами четвертого и пятого элементов И соответственно, выход четвертого элемента И соединен с первым входом второго элемента ИЛИ, вы0 ход которого соединен с единичным входом триггера, управляквдий вход трассировки программы устройства соединен с вторым входом второго элемента ИЛИ, выход пятого элемента И явля5 ется вторам выходом прерывания устройства.

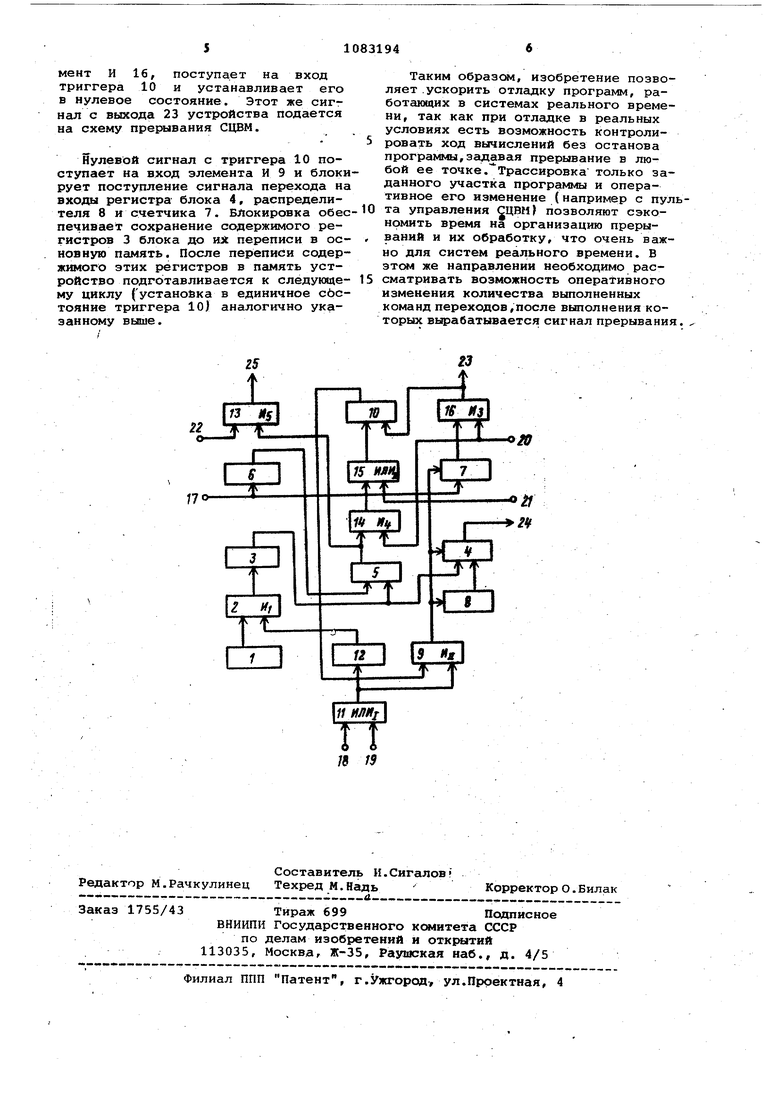

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит регистр 1 исполнительного адреса, первый элемент и 2, регистр 3 адреса команд, блок 4 буферных регистров, схему 5 сравнения, регистр б начального адреса, счетчик 7, распределитель 8, второй эле5 мент И 9j триггер 10, первый элемент ИЛИ 11, элемент 12 задержки, пятый и четвертый элементы И 13 и 14, второй элемент ИЛИ 15, третий элемент И 16, информационный вход И 17, входы 18 н 19 признаков команд условного и безусловного переходов, первый управляющий вход 20 режима работы устройства, управляющий вход 21 трас сировки программы, второй управляю-щий вход 22 режима работы устройст ва, первый выход 23 прерывания устройства, информационный выход 24 и второй выход 25 прерывания устройства Выход регистра 1 исполнительного адреса соединен через первый элемент И 2 с входом регистра 3 адреса коман выход которого подключен к входу бло ка 4 буферных регистров и входу схемы 5 сравнения, второй .вход которой соединен с выходом регистра б началь ного адреса, вход которого подключен к входу счетчика 7, второй вход кото рого соединен с входом блока 4 буфер ных регистров, входом распределителя 8 и выходом второго элемента И 9, первый вход которого соединен с выхо дом триггера 10, а второй - с выходо первого элемента ИЛИ 11 и через элемент 12 задержки с вторым входом пер вого элемента И 2. Выход схемы 5 сра нения соединен с входом пятого элеме та И 13 и через четвертый элемент И 14 с входом второго элемента ИЛИ .1 выход которого соединен с входом три гера 10. Второй вход триггера 10 сое динен с выходом третьего элемента И 16, входы которого соответственно соединены с вторым входом четвертого элемента И 1-4 к выходом счетчика 7, группа входов блока 4 буферных регистров соединена с группой выходов распределителя 8. , Входы 17-22 служат для приема управляющих сигналов, а выходы 23-25 .для их выдачи. Устройство работает следующим образом.. Режим работы устройства определяется подачей управляющего сигнала на вход 22 (режим 1) или вход 20 (режим 2). В режиме 1 устройство обеспечивает формирование сигнала прерывания в любой заданной точке программы. Для этого адрес команды, после вьшолнения которой необходимо произвести прерывание, записывается по входной шине 17 в регистр начального адреса . Адрес выполняемой команды находится на регистре 3 адреса команд, с выхода которого адрес поступает на первый вход схемы 5 сравнения, на второй вход которой подается содержимое регистра 6 начального ад.. При равенстве содержимого регистров 3 и 6 схемой 5 сравнения выграбатывается сигнал, который проходи через элемент И 13 на выход 25 устройства и далее на схему прерывания СЦВМ. Вызванная программа производит фиксирование состояния процессора в оперативной памяти СЦВМ, что позволяет программисту анализировать и контролировать ход выч слений. В режиме 2 устройство обеспечивает формирование сигнала прерывания при выполнении заданного количества команд условных и безусловных переходов . В этом случае при выполнении команды условного или безусловного п -1-1ехода на вход 18 или 19 устройства поступает сигнал перехода, который проходит через элемент ИЛИ 11 и поступает на ёходы элемента 12 задержки и элемента И 9. На второй вход этого элемента подается единичный сигнал с выхода триггера 10, установка в единичное состояние которого производится двумя способами в зависимости от режима трассировки. При трассировке заданного участка программы начальный адрес этого участка записывается в регистр б по входной шине 17. Адрес выполняемой команды, как и в режиме 1, находится на регистре 3. При равенстве содержимого регистров 3 и 6 схемой 5 сравнения вырабатывается сигнал, который проходит через элементы И 14 и ИЛИ 15, устанавливая триггер 10 в единичное состояние. При трассировке программы сигнал с входа 21 устройства через элемент ИЛИ 15 поступает на вход триггера 10 и устанавливает его в единичное состояние. Количество команд переходов, после выполнения которых необходимо произвести прерывание, записывается в дополнительном коде в счетчик 7 по входной шине 17. При наличии единичного сигнала на входе элемента И 9 сигнал перехода с выхода этого элемента производит . запуск распределителя 8, осуществляет прибавление 1 к счетчику 7 и пере писывает содержимое регистра 3 на первый регистр блока 4. Сигнал с выхода элемента 12, задержанный на время, необходимое для занесения регистра 3 на регистр блока 4, осуществляет перепись содержимого регистра 1 на регистр 3. Распределитель 8 вырабатывает управляпощие импульсы, которяле разрешают перепись информации с одного регистра на другой и т.д. Работа распределителя завершается за время выполнения одной команды перехода. Содержимое регистров блока 4 выводится для переписи в основную оперативную память по выходной шине 24. Счетчик считает количество выполненных команд переходов и выдает сигнал переполнения при выполнении заданного количества команд. Сигнал переполнения проходит через элемент И 16, поступает на вход триггера 10 и устанавливает его в нулевое состояние. Этот же сигнал с выхода 23 устройства подается на схему прерывания СЦВМ. Нулевой сигнал с триггера 10 поступает на вход элемента И 9 и блоки рует поступление сигнала перехода на входы регистра блока 4, распределителя 8 и счетчика 7. Блокировка обес печивает сохранение содержимого регистров 3 блока до их переписи в основную память. После переписи содержимого этих регистров в память устройство подготавливается к следукмцему циклу (устанойка в единичное сбстояние триггера 10J аналогично указанному выше.

о/ Таким образсм, изобретение позволяет .ускорить отладку программ, работаивдих в системах реального времени, так как при отладке в реальных условиях есть возможность контролировать ход вычислений без останова программы,задавая прерывание в любой ее точке.Трассировка только заданного участка программы и оперативное его изменение (например с пульта управления СЦВМ) позволяют сэкономить время на организацию прерываний и их обработку, что очень важно для систем реального времени. В этом же направлении необходимо рассматривать возможность оперативного изменения количества выполненных команд переходов,после выполнения которых вырабатывается сигнал прерывания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1985 |

|

SU1280636A1 |

| Устройство для отладки программ | 1989 |

|

SU1689955A1 |

| Устройство для отладки программ | 1986 |

|

SU1363221A1 |

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

| Устройство для отладки программ | 1988 |

|

SU1583744A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки программ | 1982 |

|

SU1049914A1 |

| Устройство для отладки программ | 1981 |

|

SU980096A1 |

| Устройство для отладки программ | 1988 |

|

SU1501102A1 |

УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ, содержащее регистр исполнительного адреса, регистр адреса -) команд, блок буферных регистров, распределитель, счетчик, тригГер три элемента И, первый элемент ИЛИ и элемент задержки, причем выход, : регистра исполнительного адреса соединен с первым входом первого элемента И,.выход которого соединен с входом регистра адреса команд, выход последнего соединен с информационным входом блока буферных регист- ров, входы команд условного и безусловного переходов признака устройства соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первьлм входом второго элемента И и через элемент задержки с вторым входом первого элемента И,-выход втброг6 элемента И соединен с управляющим входом записи блока буферных регистipOB и счетными входами счетчика и , распределителя, выходы которого соединены с адресными входами блока буферных регистров, выходы которого являются информационными выходами устройства, выход счетчика и первый управляющий вход режима работы устройства соединены соответственно с первым и вторым входами третьего элемента И, выход которого соединен с нулевым входом триггера и является первым выходом прерывания устройства, выход триггера соединен с вторым входом второго элемента И, отличающееся тем, что, с целью повышения производительности, в него введены регистр начального адреса, схема сравнения, два элемента И и второй элемент ИЛИ, причем информационный вход устройства соединен с входом регистра начального адреса (Л и информационным входом счетчика, выход регистра начального гщреса сое динен с первым входом схемы сравнения, выход регистра адреса команд соединен с вторым входом схемы сравнения, выход которой соединен с первыми входами четвертого и пятого элементов И, первый и второй управляющие входы режима работы устройст00 00 ва соединены с вторыми входами четг вертого и пятого элементов И соответственно, выход четвертого элемента И соединен с первым входом второ го элемента ИЛИ, выход которого соединен с единичном входом триггера, управляющий вход трассировки прогрги мы устройства соединен с вторым йходом второго элемента ИЛИ, выход пятого элемента И является вторьм выходом прерывания устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для отладки программ | 1974 |

|

SU598077A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР 754419, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-30—Публикация

1982-12-17—Подача