Изобретение относится к вычислительной технике и может быть использовано в устройствах управления СЦЕШ для обеспечения отладки программ.

Цель изобретения - повышение производительности при отладке программы,

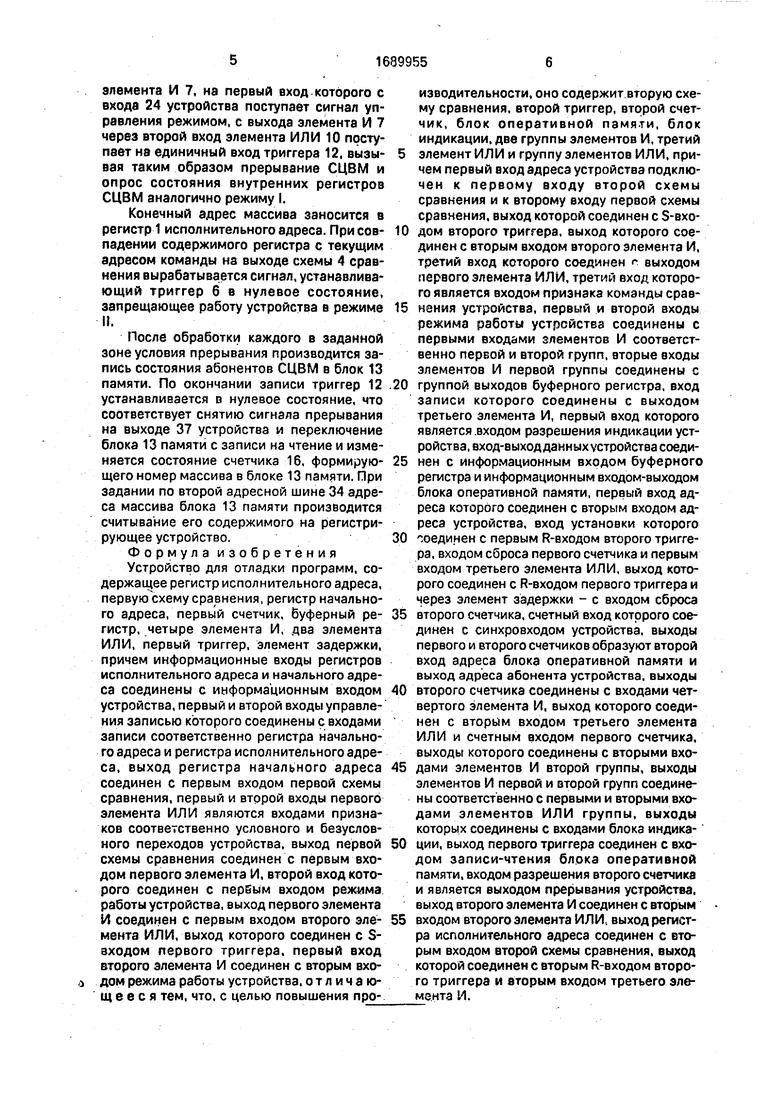

На чертеже представлена схема устройства.

Устройство содержит регистр 1 исполнительного адреса, регистр 2 начального адреса 2, первую 3 и вторую А схемы сравнения, третий элемент И 5, второй триггер 6, второй элемент И 7, первую группу элементов И 8, первый элемент ИЛИ 9, второй элемент ИЛИ 10, первый элемент И 11, первый триггер 12, блок 13 оперативной памяти, второй счетчик 14, четвертый элемент И 15, первый счетчик 18, группу элементов ИЛИ 17, вторую группу элементов И 18, блок 19 индикации, элемент 20 задержки, третий элемент ИЛ И 21, буферный регистр 22, первый 23 и второй 24 входы режима работы, первый вход 25 адреса, первый вход 26 управления записью, второй вход 27 управления записью, информацигнный вход 28, входы 29 - 31 признаков команд условного, безусловного перехода и команды сравнения соответственно, вход 32 разрешения индикации, вход-выход 33 данных, второй вход 34 адреса, вход 35 установки, синхров- ход 36, выход 37 прерывания, выход 38 адреса абонента устройства. Входы 23-26 служат для приема управляющих сигналов, а выходы 37 к 38 --для выдачи управляющих сигналов с устройства.

Устройство работает следующим образом.

Режим работы устройства определяется подачей управляющего сигнала на вход 23 (режим I) или на вход 24 (режим II). Перед заданием режима производится установка в исходное состояние подачей управляющего сигнала на вход 35 устройства,

В режиме I устройство обеспечивает формирование сигнала прерывания в любой заданной точке программы и индикацию содержимого любой ячейки памяти, к которой было обращение при трассировке любого участка программы, Для этого адрес команды, по которому необходимо произвести прерывание, с информационного входа 28 при наличии сигнала управления записью на входе 26 заносится в регистр 2 начального адреса, с выхода, которого поступает на группу входов схемы 3 сравнения, другая группа входов которой подключена ; входной первой адресной шине 25 устройства.

При равенстве информации на входах, выходе схемы 3 сравнения вырабатывается

сигнал, устанавливающий триггер б в единичное состояние м через элемент И 11 и первый вход элемента ИЛИ 10 поступающий на единичный сход триггера 12. Устаповка триггера с единичное состояние соответствует выработке сигнала, который через управляющий выход 37 поступает на схему прерывания СЦВМ. Кроме того, этот сигнал поступает на четвертый вход управ0 ления записью-чтением в блок 13 и вход счетчика 14, который при наличии синхроимпульса с СЦВМ на входе 36 устройства формирует на выходе 38 адреса абонентов СЦВМ и адреса ячеек бло;$а 13 памяти, в

5 которые производится запись состояния регистров СЦВМ. После опроса всех абонентов СЦВМ элементом И 15 вырабатывается сигнал, который поступает на счетный вход счетчика 16, формирующий номер массива

0 в блоке 13. Кроме того, сигнал с выхода элемента И 15 через первый вход элемента ИЛИ 21 поступает на нулевой вход триггера 12 и чер%з элемент 20 задержки на управляющий вход счетчика 14, устанавливая его в

5 исходное состояние. Установка триггера 12 в нулевое состояние соответствует снятию сигнала прерывания в СЦВМ и продолжению выполнения программы.

Адрес, интересующий оператора ячей0 к и памяти, заносится в регистр 1 исполнительного адреса. При совпадении сигналов на входах схемы 4 сравнения на ее выходе вырабатывается сигнал, поступающий на нулевой вход триггера 6, а через элемент И

5 5 при подаче на него управляющего воздействия с входа 32 устройства - на вход управления записью буферного регистра 22, на информационный вход которого поступает информация с шины 33 да иных устройства.

0 Состояние буферного регистра через элементы И 18 и ИЛИ 17 индицируется устройством индикации.

В режиме II устройство обеспечивает формирование сигнала прерывания при вы5 полнении команд условного, безусловного перехода или команды сравнения в любом заданном интервале исследования. Задание интервала исследования осуществляется следующим образом.

0 ,j Начальный адрес массива заносится в регистр 2 начального адреса, который при сравнении с текущим адресом выполняемой команды на схеме-3 сравнения устанавливает триггер 6 в единичное состояние. Единич5 ный выход этого триггера разрешает работу устройства в режиме II. В этом случае при выполнении одной из указанных команд на входы 29-31 устройства поступает признак соответствующей команды, который через элемент ИЛИ 9 поступает на третий вход

элемента И 7, на первый вход которого с входа 24 устройства поступает сигнал управления режимом, с выхода элемента И 7 через второй вход элемента ИЛИ 10 поступает на единичный вход триггера 12, вызывая таким образом прерывание СЦВМ и опрос состояния внутренних регистров СЦВМ аналогично режиму I.

Конечный адрес массива заносится в регистр 1 исполнительного адреса. При совпадении содержимого регистра с текущим адресом команды на выходе схемы 4 сравнения вырабатывается сигнал, устанавливающий триггер б в нулевое состояние, запрещающее работу устройства в режиме II.

После обработки каждого в заданной зоне условия прерывания производится запись состояния абонентов СЦВМ в блок 13 памяти. По окончании записи триггер 12 устанавливается в нулевое состояние, что соответствует снятию сигнала прерывания на выходе 37 устройства и переключение блока 13 памяти с записи на чтение и изменяется состояние счетчика 16, формирующего номер массива в блоке 13 памяти. При задании по второй адресной шине 34 адреса массива блока 13 памяти производится считывание его содержимого на регистрирующее устройство.

Формула изобретения

Устройство для отладки программ, содержа ш,ее регистр исполнительного адреса, первую схему сравнения, регистр начального адреса, первый счетчик, буферный регистр, четыре элемента И, два элемента ИЛИ, первый триггер, элемент задержки, причем информационные входы регистров исполнительного адреса и начального адреса соединены с информационным входом устройства, первый и второй входы управления записью которого соединены с входами записи соответственно регистра начального адреса и регистра исполнительного адреса, выход регистра начального адреса соединен с первым входом первой схемы сравнения, первый и второй входы первого элемента ИЛИ являются входами признаков соответственно условного и безусловного переходов устройства, выход первой схемы сравнения соединен с первым входом первого элемента И, второй вход которого соединен с первым входом режима работы устройства, выход первого элемента И соединен с первым входом второго элемента ИЛИ, выход которого соединен с S- зходом первого триггера, первый вход второго элемента И соединен с вторым вхо- дом режима работы устройства, отличающееся тем. что. с целью повышения производительности, оно содержит вторую схему сравнения, второй триггер, второй счетчик, блок оперативной памяти, блок индикации, две группы элементов И, третий

5 элемент ИЛИ и группу элементов ИЛИ, причем первый вход адреса устройства подклю- чек к первому входу второй схемы сравнения и к второму входу первой схемы сравнения, выход которой соединен с S-вхо0 дом второго триггера, выход которого соединен с вторым входом второго элемента И, третий вход которого соединен г выходом первого элемента ИЛИ, третий вход которого является входом признака команды срав5 кения устройства, первый и второй входы режима работы устройства соединены с первыми входами элементов И соответственно первой и второй групп, вторые входы элементов И первой группы соединены с

0 группой выходов буферного регистра, вход записи которого соединены с выходом третьего элемента И, первый вход которого является .входом разрешения индикации устройства, вход-выход данных устройства соеди5 нен с информационным входом буферного регистра и информационным входом-выходом блока оперативной памяти, первый вход адреса которого соединен с вторым входом адреса устройства, вход установки которого

0 соединен с первым R-входом второго триггера, входом сброса первого счетчика и первым входом третьего элемента ИЛИ, выход которого соединен с R-входом первого триггера и через элемент задержки - с входом сброса

5 второго счетчика, счетный вход которого соединен с синхровходом устройства, выходы первого и второго счетчиков образуют второй вход адреса блока оперативной памяти и выход адреса абонента устройства, выходы

0 второго счетчика соединены с входами четвертого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ и счетным входом первого счетчика, выходы которого соединены с вторыми вхо5 дами элементов И второй группы, выходы элементов И первой и второй групп соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, выходы которых соединены с входами блока индика0 ции, выход первого триггера соединен с входом записи-чтения блока оперативной памяти, входом разрешения второго счетчика и является выходом прерывания устройства, выход второго элемента И соединен с вторым

5 входом второго элемента ИЛИ, выход регистра исполнительного адреса соединен с вторым входом второй схемы сравнения, выход которой соединен с вторым R-входом второго триггера и вторым входом третьего элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1982 |

|

SU1083194A1 |

| Устройство для отладки программ | 1985 |

|

SU1280636A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Устройство для отладки программ | 1988 |

|

SU1583744A1 |

| Устройство для отладки программ | 1986 |

|

SU1363221A1 |

| Устройство для отладки программ | 1982 |

|

SU1049914A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

Изобретение относится к вычислительной технике и может быть использовано при отладке рабочих программ в реальном масштабе времени СЦВМ. Недостатком аналогичных устройств является ограниченность возможности наглядного контроля за ходом 79 30 Я выполнений программ, вследствие чего в одних случаях контроль ведется только по конечному результату, в других запись состояния абонента в оперативную память СЦВМ сокращает ее рабочий объем. Кроме того, эти устройства не обеспечивают автоматический запуск программы после обработки очередного условия прерывания. Целью изобретения является повышение производительности при отладке программ. Устройство содержит регистр 1 исполнительного адрес, регистр 2 начального адреса, две схемы 3 и 4 сравнения, элемент 20 задержки, буферный регистр 22, два триггера 6 и 12, элементы И 5,7,8,15,18, элементы ИЛИ 9,10,17,21, два счетчика 14 и 16, блок 19 индикации и блок 13 оперативной памяти. 1 ил. « Ё О 00 ю о ел (Л 11 о о i ff Я 34 35 3S

| Устройство для контроля выполненияпРОгРАММы | 1979 |

|

SU842823A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1982 |

|

SU1083194A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-07—Публикация

1989-05-10—Подача