Изобретение относится к вычислительной технике и может быть использовано в устройствах управления СЦВМ для обеспечения отладки и проверки работы программ в реальном масштабе времени.

Цель изобретения - расширение функциональных возможностей устройства обеспечения фиксации момента выхода программы останова на незапланированную область.

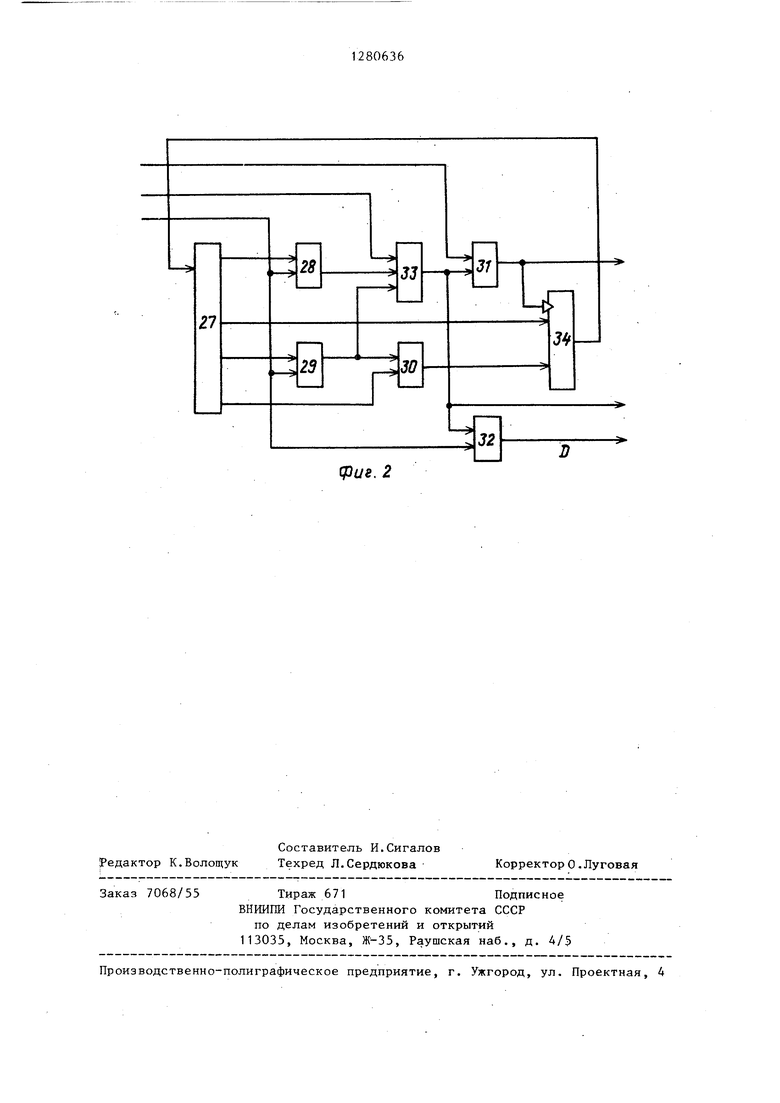

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - функциональная схема блока обработки адресов переходов.

Устройство содержит регистр 1 начального адреса, блок 2 буферных регистров, схему 3 сравнения, первьй элемент И 4, второй элемент И 5, третий элемент И 6, четвертый элемент И 7,- первый триггер 8, первый элемент ИЛИ 9, второй элемент ИЛИ 10 счетчик 11, элемент 12 задержки, распределитель 13 импульсов, блок 14 обработки адресов переходов, второй триггер 15, информационный вход 16, вход 17 адреса команд, первый 18.1 и второй 18.2 входы трассировки программы, первый 19, второй 20 входы режима работы устройства, входы 21 и 22 признаков команд условных и безусловного переходов, информационные выходы устройства 23, выход 24 неисправной работы устройства, первый 25, второй 26 выходы прерывания устройства.

Блок обработки адресов переходов (фиг. 2) содержит блок 27 памяти, первую 28, вторую 29 схемы сравнения первый 30, второй 31 элементы И,. группу 32 элементов И, элемент ИЛИ 33, регистр 34. В блок 27 записываются адреса следующих точек переходов. При этом по первым выходам записывается адрес первого следующего, перехода, по третьим выходам - адрес второго следующего перехода, по вторым выходам - следующий адрес оперативного запоминающего устройства.

Устройство работает следующим о&разом.

Режим работы устройства определяется подачей управляющего сигнала на вход 20 (режим I) или вход 19 (режим П).

В режиме I устройство обеспечивает формирование сигнала прерывания в любой заданной точке программы.

5

Для этого адрес команды, после выполнения которой необходимо произвести прерывания, записывается по входу 16 в регистр начального адреса. Адрес выполняемой команды поступает по входу 17 адреса команд СЦВМ на второй вход схемы 3 сравнения, на первый вход которой подается содержимое регистра 1 начального адреса. При равенстве содержимого регистра 1 с со- держимым входа 17 адреса команд схемой 3 сравнения вырабатывается сигнал, который через элемент И 7 поступает на выход 26 устройства и далее

0

5

0

на схему прерывания СЦВМ. Вызванная программа производит фиксирование состояния процессора в оперативной памяти СЦВМ, что позволяет программисту контролировать и анализировать ход вычислений.

В режиме 11 устройство обеспечивает формирование сигнала прерывания при выполнении заданного количества условных и безусловных переходов или проверки работы программы по всем адресам переходов. В этом случае при выполнении команды условного или безусловного перехода на вход 21 или 22 устройства поступает сигнал перехода, который проходит через элемент ИЛИ 9 и поступает на входы элемента 12 задержки и элемента И 4, на второй вход которого подается единичный сигнал с выхода 5 триггера 8, установка в единичное состояние которого производится двумя способами в зависимости от режима трассировки.

0 При трассировке заданного участка программы начальньй адрес этого участка записывается в регистр 1 начального адреса и аналогично режиму 1 сравнивается с адресом выполняемой

5 команды. Сигнал сравнения через элемент И 6 и элемент ИЛИ 10 устанйвли- вает триггер 8 в единичное состояние. При трассировке программы сигнал с входа 18( устройства через элемент ИЛИ 10 поступает на вход триггера 8. Количество команд переходов, после которых необходимо произвести прерывания, записывается в дополнительном коде в счетчик 11

г по шине 16. На входе IS - единичный уровень. .При наличии единичного сигнала на первом входе элемента И 4 сигнал перехода с выхода этого элемента производит запуск распре0

делителя 13 и переписывает содержимое входа 17 черрз открытые элементы И группы 32 элементов И (на выходе элемента ИЛИ 33 - единичный сигнал) на первый регистр блока 2. Распределитель 13 формирует по второму выходу сигнал, которьп через открытый элемент И 31 поступает на синхро- вход счетчика 11 и прибавляет к нему единицу. Содержимое регистра 2 выводится для перезаписи в основную оперативную память по выходной шине 23. Счетчик 11 считает количество выполненных команд переходов и вьщает сигнал переполнения при выполнении заданного количества прерываний. Сигнал переполнения через элекент И 5 поступает на вход триггера 8 и устанавливает его в нулевое состояние. Этот же сигнал с ройства подается на СЦВМ,

Нулевой сигнал с выхода триггера 8 поступает на вход элемента И 4 и блокирует поступление сигнала перехода на входы регистра блока 2, распределителя 13. После перезаписи содержимого регистров блока 2 в память устройство подготавливается к следующему циклу (установка в единичное состояние триггера 10) аналогично указанному.

выхода 25 уст- схему прерывания

12806364

,, четвертому выходу - 1 т.е. по адресу 10 записаны адреса переходов Пр4 и Пр5, а по адресу И - Прб, Пр7. При выполнении программы вход 17 5 адреса команд СЦВМ сравнивается с одним из двух адресов следующих переходов на схемах 28 и 29 сравнения. Сигнал сравнения поступает через элемент ИЛИ 33 на вход И 31, на вто10 рой вход которого поступает сигнал с распределителя 13, по объединению которых осуществляется запись следующего адреса блока 27 в регистр 34. Одновременно с выхода 1 блока 14

15 обработки адресов переходов (с группы 32 элементов И) поступает информация в блок 2 буферных регистров и сигнал (с выхода элемента И 31) для переключения счетчика 11. При сравнении по третьим входам единич- ньш уровень через элемент И 30 поступает на младший информационный вход регистра 34.;

При поступлении команд переходов и несравнении с заданными адресами на выходе элемента ИЛИ 33 - нулевой уровень, который с задержкой на элементе 12 задержки записывается в триггер 15, указывающий на наличие

30 неисправности в СЦВМ или в программе.

Не записывая некоторые адреса переходов в блок 27, возможно проверить отдельные ветви программы.

20

25

Режим проверки работы программы по всем адресам переходов задается сигналами единичного и нулевого уровня соответственно по входам 18, и 18.

При работе устройства в режиме II

35

Формула изоб ретения

Устройство для отладки программ, содержащее регистр начального адре- регистр 34 предварительно обнуляется, 40 са, блок буферных регистров, распреа триггер 15 устанавливается в еди- ничное состояние (сигналы установки на фиг. 1 и 2 не приведены). В блоке 27 предварительно записываются адреса переходов: при обработке первого перехода (Пр1) программа мо- ясет продолжать работу по двум разным ветвям программы к точкам следующих переходов (Пр2, ПрЗ). Из точек переходов Пр2 и ПрЗ программа может продо.гокать работу соответственно к точкам переходов Пр4, Пр5 и Прб, Пр7 и т.д.

Тогда по нулевому адресу блока 27 записывается следующая информация: по первым выходам - адрес Пр2, по третьим выходам - ПрЗ, по вторым выходам - адрес, где записаны адреса переходов Пр4 и Пр5, например Т по

делитель .импульсов, счетчик, первый триггер, четыре элемента И, два элемента ИЛИ, схему сравнения, элемент задержки, причем входы признаков команд условных и безусловных переходов устройства соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И и входом элемента задержки, выход первого элемента И соединен с входом синхронизации распре- |Делителя импульсов и с входом записи блока буферных регистров, выходы которого являются информа1щонныь И выходами устройства, первый выход распределителя импульсов соединен с адресным входом блока буферных регистров, выход переполнения счетчика соединен с первым входом второго элемента И, выход - с первым входом второго элемента И, выход которого является первым выходом прерывания устройства и соединен с входом установки нуля первого триггера, первый вход задания режима работы устройства соединен с вторым входом второго элемента И и первым входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЖ, первый вход задания трассировки программы устройства соединен с вторым входом второго элемента ИЛИ, выход которого соединен с единичным входом первого триггера, прямой выход которого соединен с вторым входом первого элемента И, адресный вход устройства соединен с первым входом схемы сравнения, выход равенства которой соединен с вторым входо третьего элемента И и первым входом четвертого элемента И, второй вход задания режима работы устройства соединен с вторым входом четвертого элемента И, выход которого является вторым выходом прерывания устройства информационный вход устройства соединен с информационными входами счетчика и регистра начального адреса, выход которого соединен с вторым входом схемы сравнения, отличающееся тем, что, с целью расширения функциональных возможностей, за счет обеспечения фиксации момента входа программы на незапланированную область, в устройство введены второй триггер и блок обработки адресов переходов, содержащий блок памяти, первую и вторую схемы сравнения, регистр, два элемента И, блок элементов И и элемент ИЛИ, причем выход элемента задержки соединен с тактовым входом второго триггера, выход которого является выходом нем,

2806366

исправной работы устройства, первый, второй, третий и четвертый в информационные выходы блока памяти соединены соответственно с первым входом

5 первой схемы сравнения, с информационным входом регистра, с первым входом второй схемы сравнения, с первым входом первого элемента И и блока обработки адресов переходов,

10 второй вход задания трассировки про- граммы устройства соединен с первым входом элемента ИЛИ блока обработки адресов переходов, выход элемента ИЛИ соединен с первым входом второго

15 элемента И, первым входом блока элементов И блока обработки адресов перехода и с информационным входом второго триггера, адресньй вход устройства соединен с вторыми входами

20 первой и второй схем сравнения и с вторым входом блока элементов И блока обработки адресов переходов, второй выход распределителя импульсов соединен с вторым входом второго эле25 мента И блока обработки адресов переходов, выходы равенства первой и второй схем сравнения соединены соответственно с вторыми и третьими входами элемента ИЛИ, блоки обработ30 ки адресов переходов, выход равенства второй схемы сравнения соединен с вторым входом первого элемента И, выход которого соединен с входом младшего разряда регистра, выход

35 которого соединен с адресным входом блока памяти, блока обработки адресов перехода, выход второго элемента и блока обработки адресов переходов соединен с входом записи регистра

40 блока обработки адресов переходов и со счетным входом счетчика, выходы блока элементов И блока обработки адресов переходов соединены с информационным входом блока буферных ре- 45 гистров.

28

27

фиг. 2

редактор К.Волощук

Составитель И.Сигалов Техред Л.Сердюкова

Заказ 7068/55

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. Д/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

33

ЗГ

1

3

Корректор О .Луговая

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1982 |

|

SU1083194A1 |

| Устройство для отладки программ | 1989 |

|

SU1689955A1 |

| Устройство для отладки программ | 1986 |

|

SU1363221A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки программ | 1982 |

|

SU1030805A1 |

| Устройство для формирования сигнала прерывания при отладке программ | 1985 |

|

SU1339569A1 |

| Устройство для отладки программ | 1988 |

|

SU1583744A1 |

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

) Изобретение относится к вычислительной технике и может быть использовано В устройствах управления ЭВМ для отладки программ в режиме реального времени. Устройство содержит регистр 1, блок 2 буферных регистров, схему 3 сравнения, первый 4, второй 5, третий 6 и четвертый 7- элементы И, первый триггер 8, элементы ИЛИ 9 и 10, счетчик 11, элемент 12 задержки, распределитель 13 импульсов, блок 14 обработки адресов переходов и второй триггер 15. Изобретение обеспечивает отладку и контроль программ по точкам перехода в режиме реального времени. 2 ил. го г (Л Г9

| Авторское сбидетельство СССР № 754419, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1982 |

|

SU1083194A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-01-14—Подача