с регистра 12 управления и четвертого 30 го такта низким уровнем с элемента НЕ

выхода выдается сигнал запрета на второй вход элемента И 14 и на единичный вход триггера 28, который постоянно его удерживает во взведенном состоянии. С первого и пятого выходов регистра 12 управления выдается разрешение |(Лог. О) на адресные входы коммутаторов 25 и 26-27 соответственно. С второго выхода регист- 1ра 12 управления выдается разрешение на триггер записи переходов работы по второму входу (вход 23 устройства) , с третьего выхода - логический О (разрешение) на первый вход элемента ИЛИ 13, ас шестого выхода регистра 12 управления выдается логическая 1 на вход 23 устройства (сигнал Перепись СК). Триггер 11 записи переходов устанавливается в 1, а через вход 19 устройства и коммутатор 25 в регистр 1 поступает адрес команды перехода. По сигналу СИ, поступающему из СЦВМ, после прихода адреса перехода через вход 22 устройства и элемент ИЛИ 21 на элемент 10 задержки вырабатывается последовательность тактов и производится по ним последовательная перезапись информации из регистра 3 в регистр 4,

5

0

32 на выходе элемента ИЛИ-НЕ 31 формируется высокий уровень сигнала Останов, что означает переход программы на циклический участок. После разгрузки буферной оперативной памяти процедура повторяется вновь до следующего циклического участка.

Работа устройства во втором режиме заключается в фиксации времени исполнения команд переходов. Сигналами меток времени являются синхроимпульсы, количество которых равно количеству циклов (СИ), пройденных СЦВМ с момента включения данного режима. С четвер- с того выхода регистра 12 управления выдается разрешение на второй вход элемента И 14, сигнал со второго вхо- |да триггера 28, удерживающий его во взведенном состоянии, снимается, а с пятого выхода регистра 12 управления на управляющие входы выдается разрешение на передачу информации со счетчика 5 времени. Остальные сигналы с выхода регистра 12 управления остаются неизменными по сравнению с предыдущим режимом. Таким образом, в этом режим по каждому СИ (после каждого цикла работы СЦВМ) содержимое счетчика 5 времени вторым тактом

0

5

элемента 10 задержки увеличивается на единицу через элемент И 14.

После прихода из СЦВМ адреса команды перехода, записанного в регист- ре 1, взводится триггер 28 и на буферном регистре 6 выдается разрешение записи информации из счетчика 5 времени через коммутаторы 26 и 27. В регистр 6 записывается (фиксируется) время поступления из СЦВМ адреса команды перехода. По первому такту следующего цикла триггер 28 сбрасы- в&ется и выдает запрет на запись в регистр 6. При поступлении нового сигнала Перепись СК вторым тактом схем задержки через регистр 3 и регистр 7 адреса записывается адрес команды перехода,время выборки которог и$ памяти СЦВМ записано уже в регистр 6 по предыдущему сигналу Перепись СК Четвертым тактом информация с регистра 6 записывается в блок 8 оперативной памяти по адресу, записанному в регистре 7, и выдается разре- шение записи информации в регистр 6 до первого такта следующего цикла. Если программа переходит на цикличес кий участок программы, то по четвертому такту с выхода формируется сиг- нал Отстанов.

Работа устройства в третьем режиме заключается в фиксации времени выборки команд из памяти СЦВМ. В этом режиме с второго выхода регистра 12 управления на первый вход триггера 1 записи перехода выдается сигнал, который удерживает его постоянно во взведенном состоянии и на регистр 1 адреса через элемент ИЛИ 13 выдается сигнал разрешения на запись постоянно. Остальные сигналы регистра 12 управления такие же, как в предыдуще режиме. При этом все адреса команд, поступающие на вход 19 устройства, записываются в регистр 1 и при поступлении СИ (в каждом цикле работы СЦВМ) переписываются из регистра 3 в регистр 7, определяя номер ячейки блока 8 оперативной памяти, в кото- рой из счетчика 5 времени через регистр 6 записывается время (т.е., номер цикла) выборки этой команды. Если программа переходит на циклический участок программы, то по че- твертому такту с выхода формируется сигнал Останов.

Работа устройства в четвертом режиме заключается в фиксации адресов - откуда и куда произведен переход, при этом с третьего выхода регистра 12 управления выдается, сигнал разрешения на элемент ИЛИ 13, благода ря которому на элементах И 15,17,18 и регистре 1 выдается разрешение независимо от состояния триггера 11 записи переходов. С пятого выхода регистра 12 управлений выдается сигнал на управляющий вход коммутаторов 26 и 27, который подключает регистры 2-4. С четвертого выхода регистра 12 управления выдается запрет на элемент И 14 и постоянное разрешение записи в буферный регистр 6 через триггер 28. Как и в предыдущем режиме , в регистрах 2-4 записываются адреса подряд идущих команд, однако триггер 11 записи перехода выдает разрешение на элемент И 16 для прохождения четвертого такта для записи в блок 8 оперативной памяти информации только после прихода сигнала Перепис СК. Поэтому в момент записи информации в блок 8 оперативной памяти из регистра 6 через коммутатор 27 имеется адрес команды, откуда производится переход (с регистра 4), и через коммутатор 26 с регистра 2 адрес команды, на который производится переход. Остальные сигналы аналогичны первому режиму.

В режиме считывания информации из блока 8 оперативной памяти с шестого выход регистра 12 управления выдается сигнал Считывание оперативной памяти (логический О) , а с первого выхода сигнал на третий вход коммутатора 25, к которому через вход 24 устройства подключается сигнал на первый вход триггера 11 записи перехода, который удерживает его во взведенном состоянии, с выхода триггера 11 записи пе- .рехода. Таким образом, выдается постоянное разрешение на Запись регистра 1 адреса и на элементах И 15-18. При этом на наборном поле набирается код, соответствующий исходному адресу ячейки памяти блока 8 оперативной памяти.

При подаче сигнала на генератор 20 одиночных импульсов запускается вре;- менная диаграмма аналогично режиму обнуления памяти с разницей в том, что в этом режиме производится считывание информации блока 8 оперативной памяти через регистр 9 считанной информации. Таким образом, можно просмотреть всю информацию с блока 8 оперативной памяти на световом табло или вывести на цифропечать.

Формула изобретения

Устройство для отладки программ, содержащее генератор одиночных импульсов, триггер, три коммутатора и гистр управления, первый и второй регистры адреса, пять элементов И, блок оперативной памяти, элемент задержки, регистр считанной информации, триггер записи переходов и буферный регистр, первый, второй и третий регистры, счетчик времени, два элемента ИЛИ, причем выход буферного регистра соединен с информационным входом блока оперативной памяти, выход которого .соединен с входом регистра считанной (информации, выход которого является Выходом устройства, выход первого (регистра адреса соединен с адресным входом блока оперативной памяти, вхо записи команды перехода устройства соединен с первым установочным входом триггера записи переходов,первый и второй выходы регистра управления соединены соответственно с вторым устано- вочным входом триггера записи переходов и первым входом первого элемента ИЛИ, выход которого соединен с первыми входами первого, второго и третьего элементов И, вторые входы которых соединены соответственно с первым, вторым и третьим выходами элемента задержки, выходы первого, второго и третьего элементов И соединены соот- ветственно с входами записи соответст- венно первого, второго и третьего регистров, выход первого элемента ИЛИ соединен с входом записи первого регистра адреса, информационный выход которого подключен к информационному входу тре- тьего регистра, информационный выход которого подключен к информационному входу второго регистрачи информационному входу второго регистра адреса, инфор- мационный выход которого подключен к иформациоиному входу первого регистра, первый вход четвертого элемента И соединен с входом сброса триггера записи переходов и с четвертым выходом элемента задержки, первый выход ко торого соединен с первым входом пятого элемента И,выход которого соединен с входом счетчика времени, третий выход регистра управления соединен с

входами управления первого и второго коммутаторов, четвертый выход регистра управления подключен к второму входу пятого элемента И и первому входу триггера, первый выход элемент задержки соединен с вторым входом триггера, выход четвертого элемента И соединен с третьим входом триггера, выход триггера записи переходов соединен с вторым входом первого элемен-j та И и вторым входом четвертого элемента И, выход триггера подключен к входу записи буферного регистра, информационные входы которого соединены с выходами первого и второго коммутаторов, к первым информационным входам которых подключены выходы первого и третьего регистров, выход счетчика времени соединен с вторыми информационными входами первого и вто рого коммутаторов, выход третьего коммутатора подключен к информационному входу первого регистра адреса, первый и второй информационные входы устройства соединены с первым и вторым информационными входами третьего коммутатора, второй информационный вход устройства соединен с информационным входом регистра управления, пятый выход которого соединен с управляющим входом третьего коммутатора, выход генератора одиночных сигналов соединен с первым входом второго элемента ИЛИ,счетным входом регистра адреса, тактовый вход устройства является вторым входом второго элемента ИЛИ, выход которого соединен с входом элемента задержки, отличающееся тем, что, с целью .повышения достоверности отладки, в устройство введены первый и второй элементы ИЛИ-НЕ, элемент НЕ, четвертый коммутатор и элемент И-НЕ, причем шестой и седьмой выходы регистра управления соединены соответственно с первым входом элемента И-НЕ и с управляющим входом четвертого коммутатора, выход которого соединен с вто-- рым входом элемента И-НЕ, информационные выходы блока оперативной памяти cqeflHHeHbr с входами первого элемента ИЛИ-НЕ, выход которого соединен с первым входом второго элемента ИЛИ-НЕ и с первым информационным входом четвертого коммутатора, выход четвертого элемента И соединен с третьим входом { элемента И-НЕ и через элемент НЕ с вто-- рым входом второго элемента ИЛИ-НЕ, выИ158374412

ход которого является выходом останова ной памяти, второй информационный устройства, выход элемента И-НЕ сое- вход коммутатора соединен с единичным динен с входом записи блока оператив- потенциалом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Устройство для отладки программ | 1989 |

|

SU1689955A1 |

| Устройство для контроля вычислительных программ | 1985 |

|

SU1278856A1 |

| Устройство для отладки программ | 1986 |

|

SU1363221A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для отладки программ | 1982 |

|

SU1083194A1 |

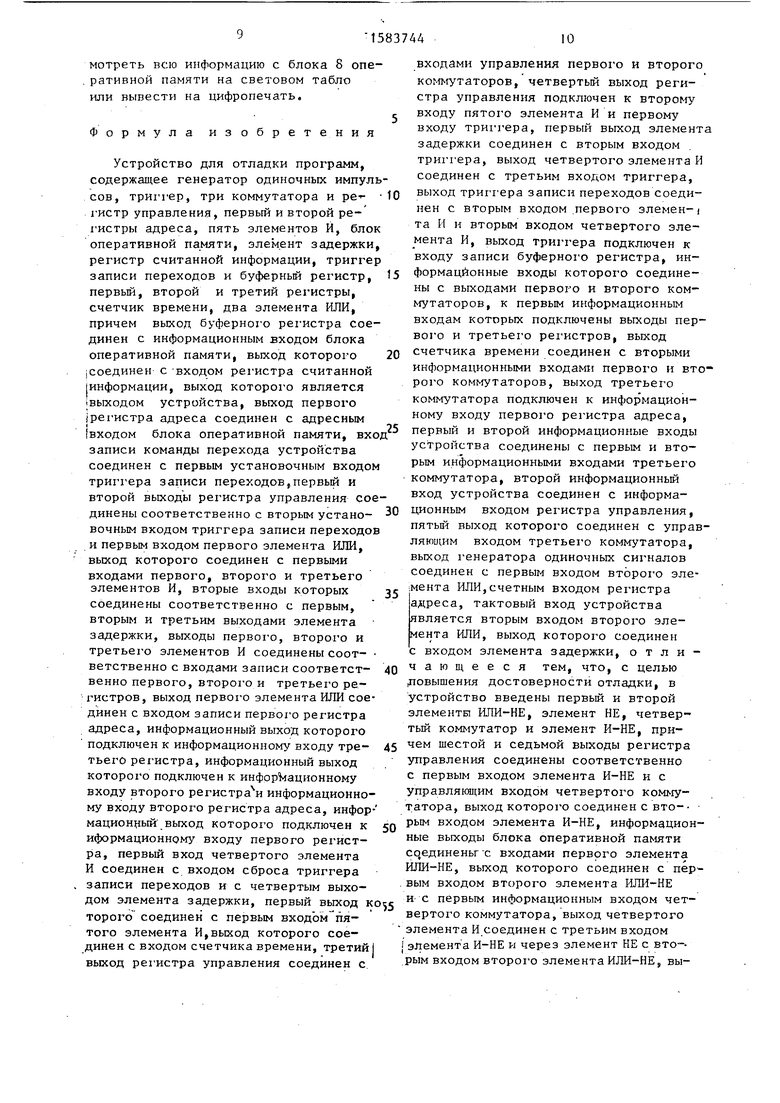

Изобретение относится к вычислительной технике и может быть использовано для отладки программ специализированных вычислительных машин в реальном масштабе времени. Целью изобретения является повышение достоверности отладки программ. Устройство содержит регистр 9 считанной информации, блок 8 оперативной памяти, регистры 1-4,7 адреса, буферный регистр 6, коммутаторы 25, 26, 27, 33, триггер 28, счетчик 5 времени, элементы И 14-18, элементы ИЛИ 13,21, элемент задержки 10, триггер 11 записи переходов, регистр 12 управления, генератор 20 одиночных импульсов, элементы ИЛИ-НЕ 30-31, элемент И-НЕ 34, входы 19, 22-24 устройства, вход 35 единичного потенциала устройства, выход 29 устройства и выход 36 устройства "Останов" с соответствующими связями. Вновь ввденные элементы обеспечивают анализ записываемой информации и в случае повторной записи происходит вывод накопленной информации, тем самым сохраняется вся информация о всех переходах. 1 ил.

| Устройство для отладки программ | 1974 |

|

SU598077A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-08-07—Публикация

1988-04-05—Подача