о

00

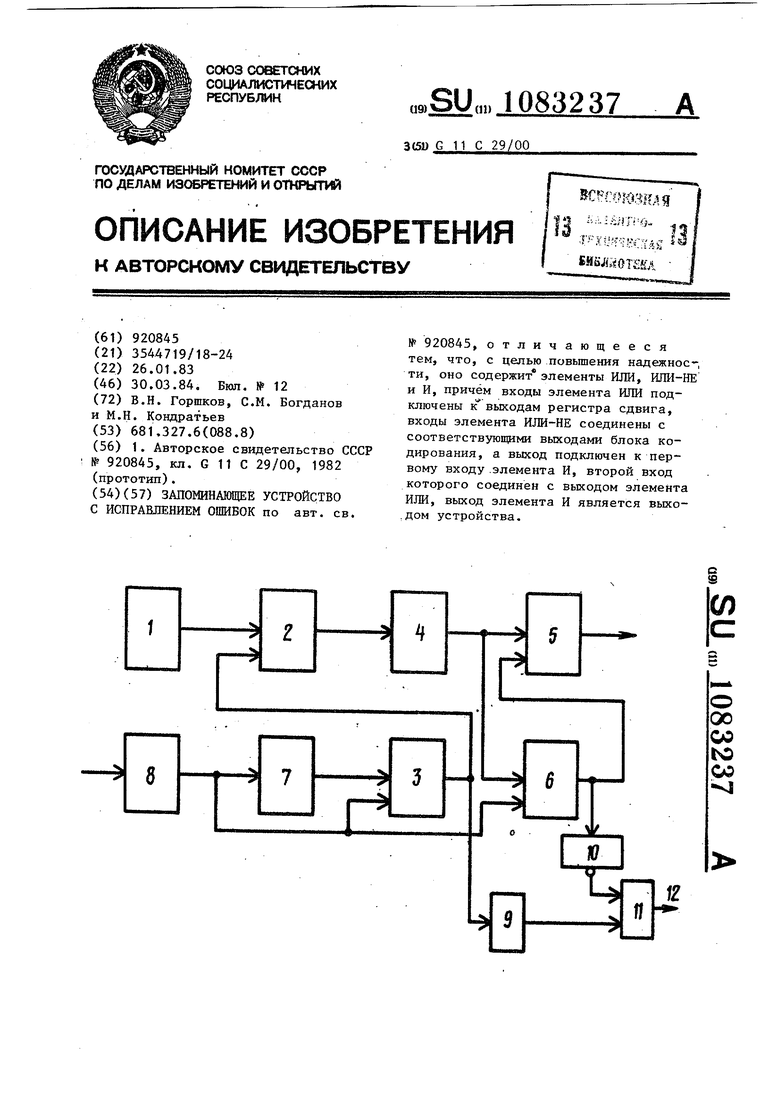

со ю со f . 1 Предлагаемое изобретение относится к запоминающим устройствам, в которых производится контроль работоспособности накопителя и аппаратур для коррекции ошибок. По основному авт.св. № 920845 известно запоминающее устройство с . исправлением ошибок, содержащее нако питель, сумматоры по модулю два, генератор импульсов, регистр сдвига, блок местного управления, блок корре ции, блок кодирования-декодирования и регистр числа, выход которого подключен к первым входам блока коррекции и блока ко;у1рования-декодирования, выход которого соединен с вторым входом блока коррекции, выход которого является выходом устройства входы сумматоров по модулю два подключены соответственно к выходам накопителя и регистра сдвига, а выходы - к входам регистра числа, выход блока местного управления соединен с вторым входом блока кодирования-декодирования, первьм входом регистра сдвига и входом генератора импульсов выход которого подключен к второму входу регистра сдвига, вход блока местного управления является управля ющим входом устройства. ClJ. В таком устройстве при контроле аппаратуры для коррекции ошибок в регистре сдвига имитируется ошибка, которая с помощью сумматоров по моду лю два вносится в считьшаемое из накопителя слово. При этом, если в сум маторах по модулю два в одном или нескольких разрядах имеются отказы, которые равносильны наличию кода О на соответствующих входах сумматоров соединенных с выходами регистра сдви га, то при этом контроль аппаратуры для коррекции ошибок либо Совсем не производится (при отказах в О всех входов сумматоров по модулю два, соединенных с выходами регистра сдвига), либо производится не в полной мере (при отказах рассмотренного типа на одном или нескольких входах сумматоров по модулю два). Следовательно, недостатком этого устройства является неполнота контроля его узлов, что обуславливает низкую достоверность контроля устройства. Цель предлагаемого изобретения повьш1ение достоверности контроля устройства. Поставленная цель достигается тем что в запоминающее устройство с 72 исправлением ошибок введены элементы ИЛИ, Ш1И-НЕ и И, причем входы элемента ИЛИ подключены к выходам регистра сдвига, входы элемента ИЛИ-НЕ оединены с соответствующими вьпсодами лока кодирования, а выход подключен к rfepBOMy входу элемента И, второй вход которого соединен с выходом элемента ИЛИ, выход элемента И является дополнительным выходом устройства. На чертеже изображена структурная схема предлагаемого изобретения. Устройство содержит накопитель 1, группу сумматоров 2 по модулю два, регистр 3 сдвига с числом разрядов на единицу больше числа разрядов считанного слова, регистр 4 числа, блок 5 коррекции, блок 6 кодирования-декодирования, генератор 7 импульсов, служаш;ий для генерации начальной единицы, блок 8 местного управления, состоящий, например, из последовательного соединенных двухразрядного регистра и дешифратора режима диагностики (на чертеже не показаны), элемент ИЛИ 9, элемент ИЛИ-НЕ 10, элемент И 11 и дополнительный выход 12. Выход регистра 4 подключен к первым входам блока 5 и блока 6, выход . которого соединен с вторым входом блока 5. Входы сумматоров 2 подключены Соответственно к выходам накопителя 1 и регистра 3, а выходы - к входам регистра 4. Выход блока 9 соединен с вторым входом блока 6, первым входом регистра 3 и входом генератора 7, выход которого подключен к второму входу регистра 3. Выходы регистра 3 сдвига соединены с входами э/гемента ИЛИ 9. Выходы блока 6 подключены к входам элемента ИЛИ-НЕ 10, выход которого соединен с первым входом элемента И 11, второй вход которого подключен к выходу элемента ИЛИ 9. Вход блока 8 является управляющим входом устройства, на которьй подаются сигналы процессора (на чертеже не показан). Выход 12 элемента И 11 является дополнительным выходом устройства. Работу устройства рассмотрим при функционировании в трех основных релСИМЗлОсновной рабочий режим. Слово, считанное из накопителя 1,через сумматоры 2 поступает на регистр 4. Поскольку в этом режиме регистр 3 пос

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок | 1979 |

|

SU920845A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU964737A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU736177A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU960958A1 |

| Устройство для коррекции ошибок в блоках памяти | 1982 |

|

SU1086460A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМ ОШИБОК по авт. св. № 920845, отличающееся тем, что, с целью повьппения надежное, ти, оно содержит элементы ИЛИ, ИЛИ-НЕ и И, причём входы элемента ШШ подключены к выходам регистра сдвига, входы элемента ИЛИ-НЕ соединены с соответствующими выходами блока кодирования, а выход подключен к первому входу .элемента И, второй вход которого соединен с выходом элемента ИЛИ, выход элемента И является выхо,дом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с исправлением ошибок | 1979 |

|

SU920845A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-03-30—Публикация

1983-01-26—Подача