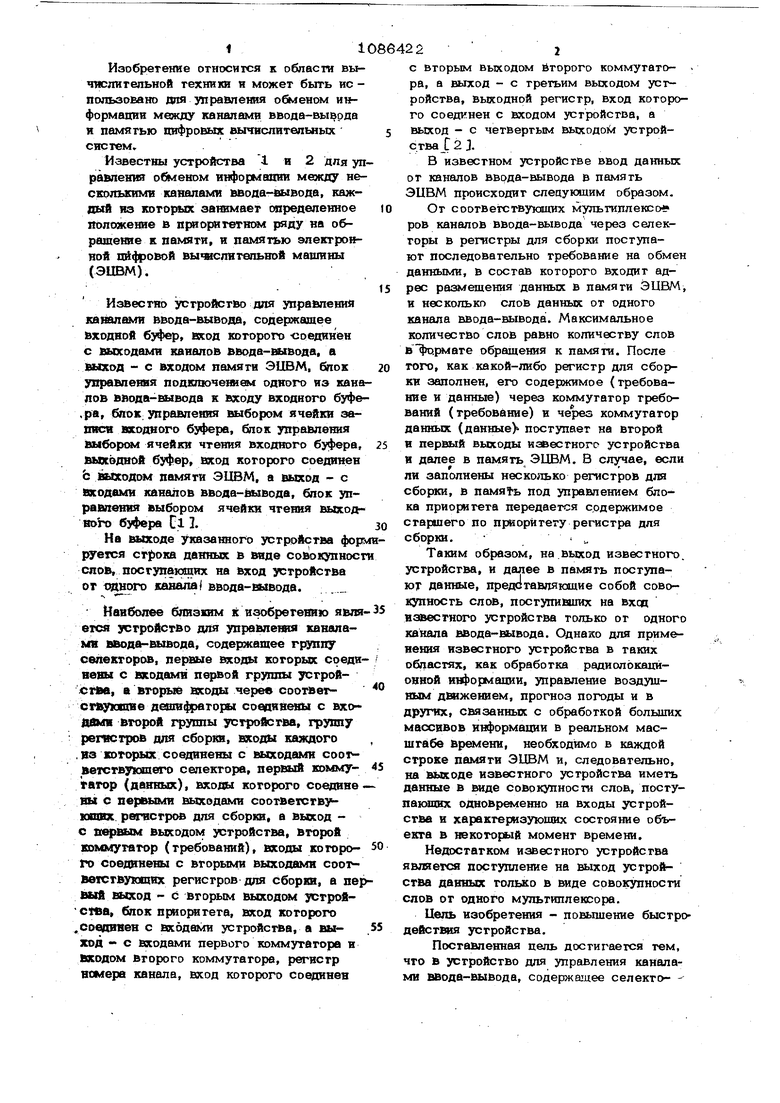

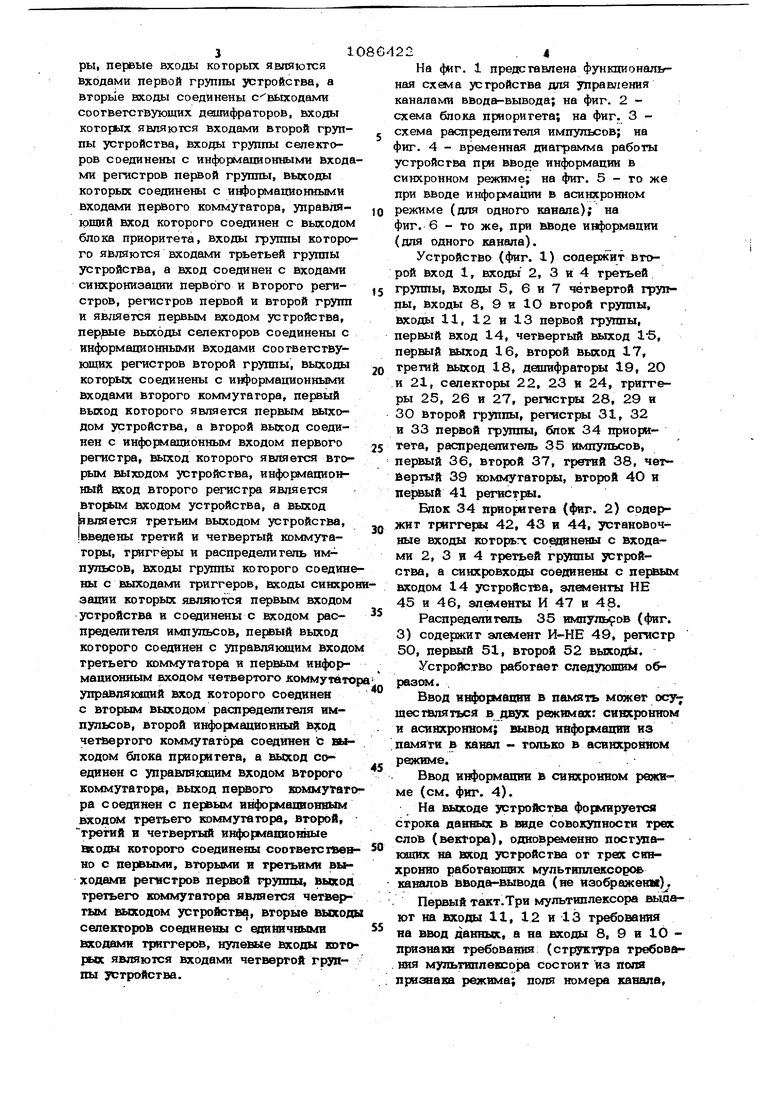

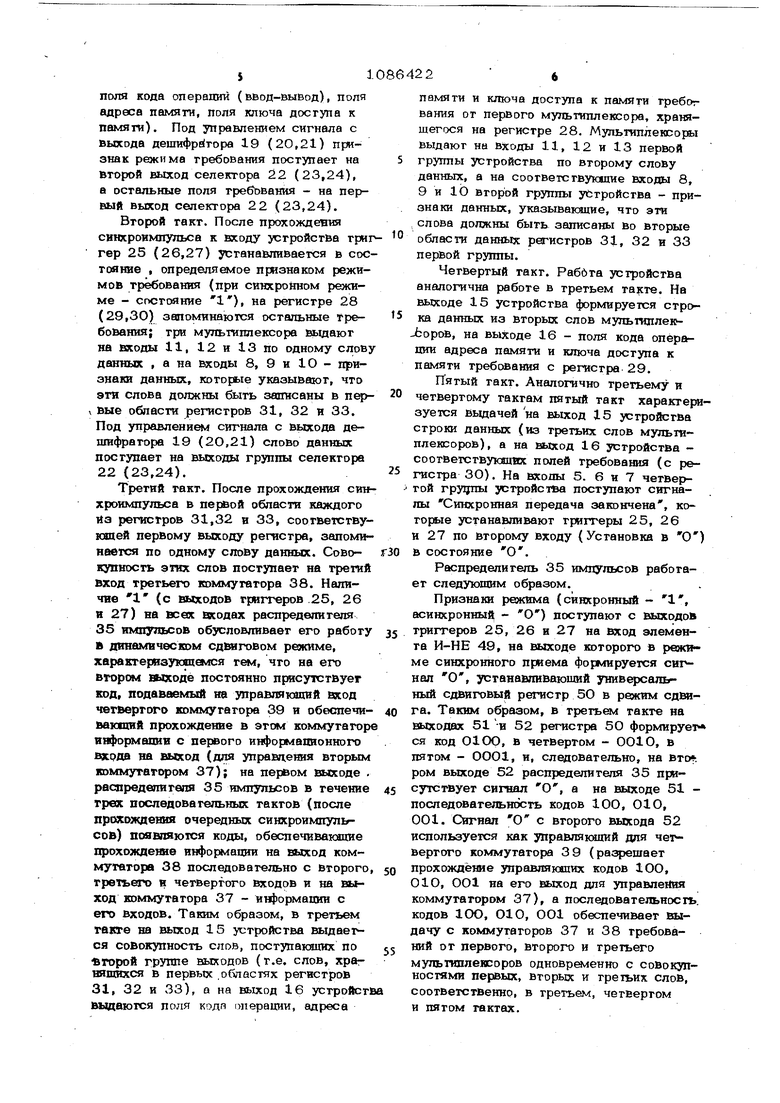

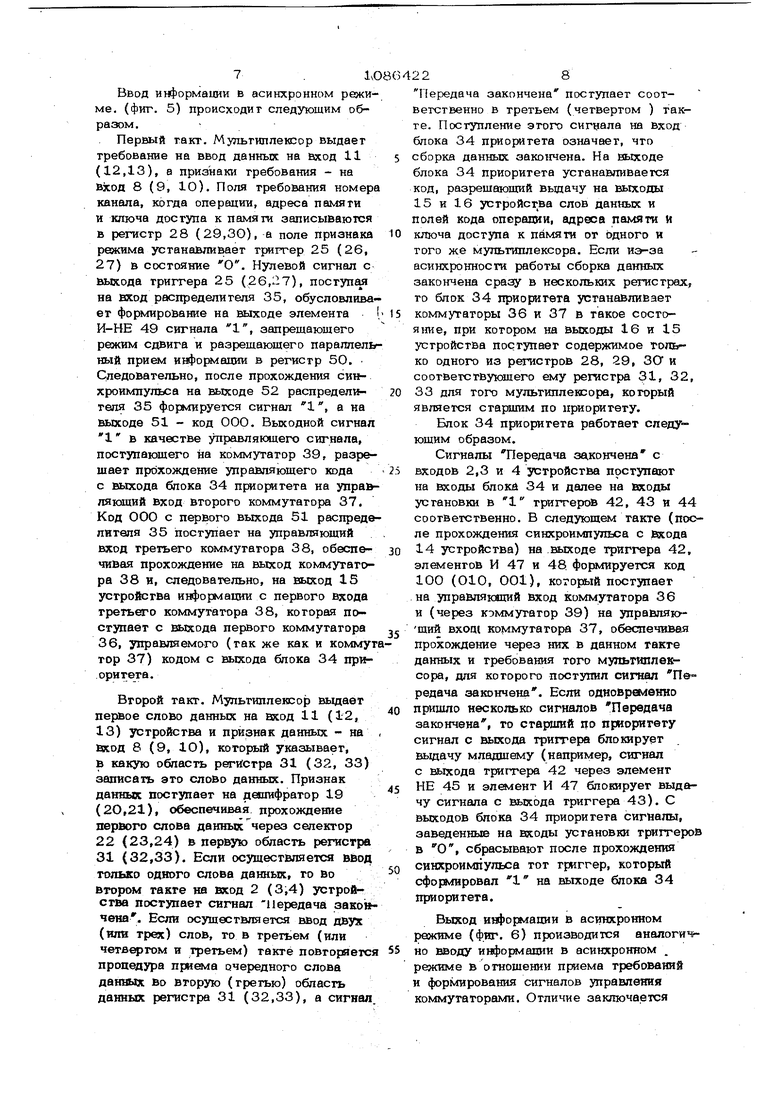

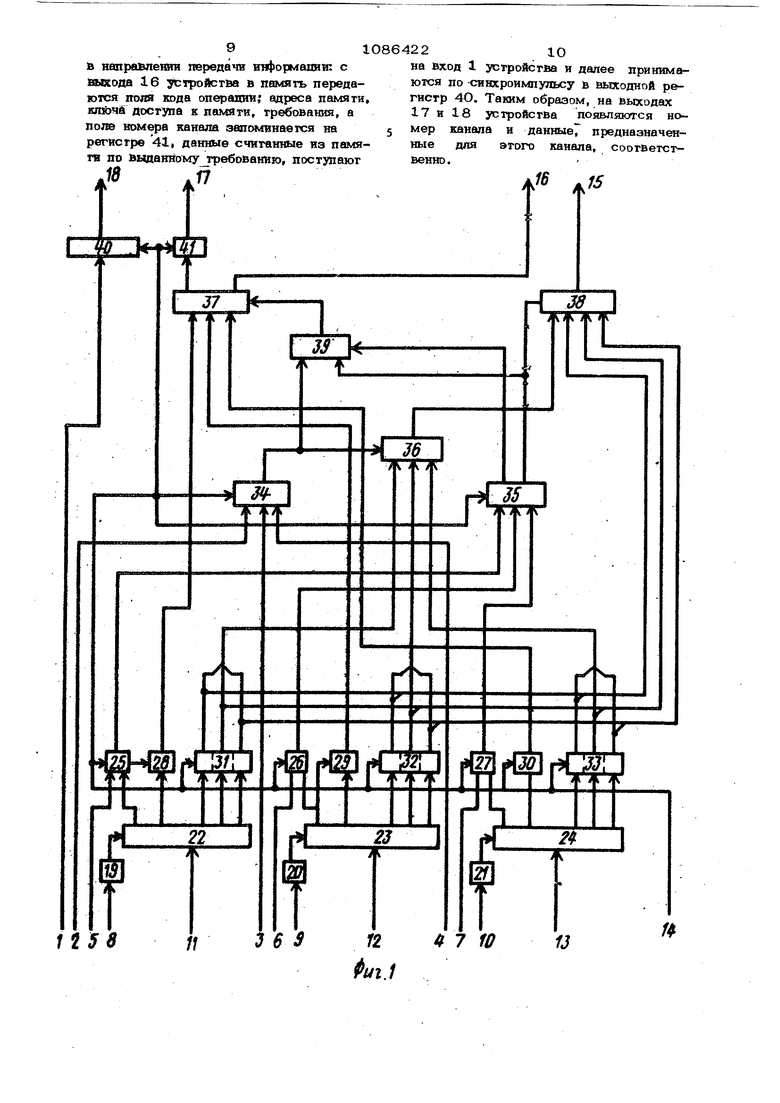

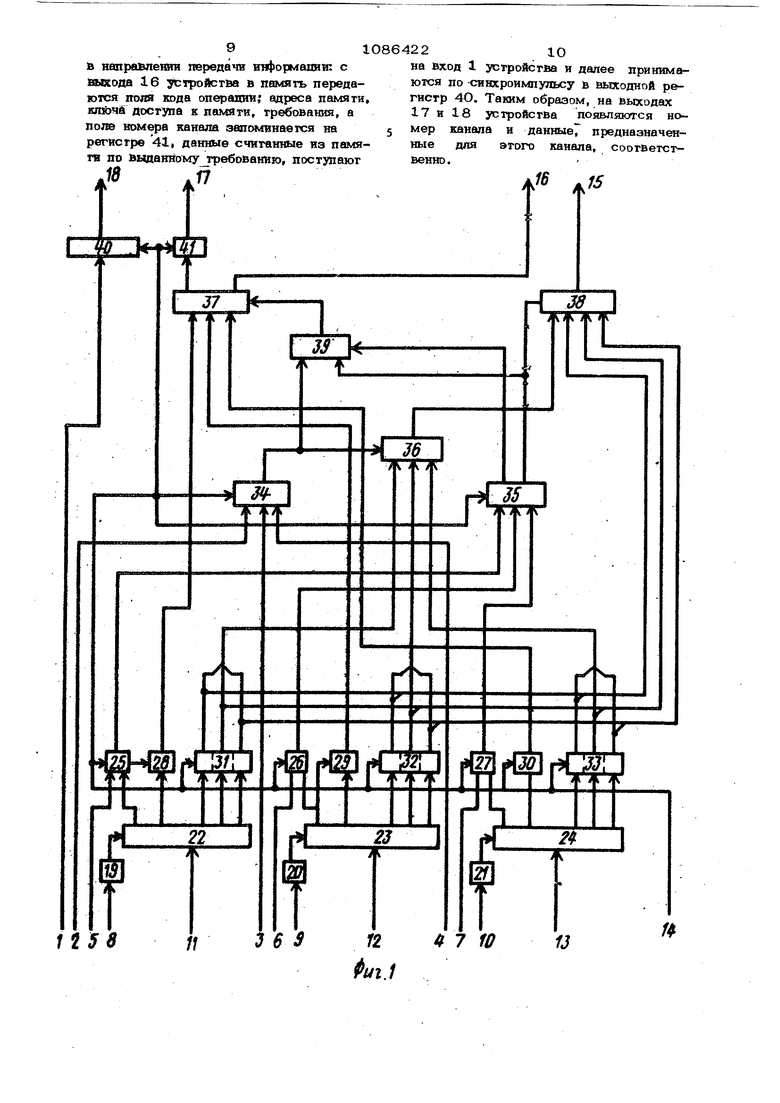

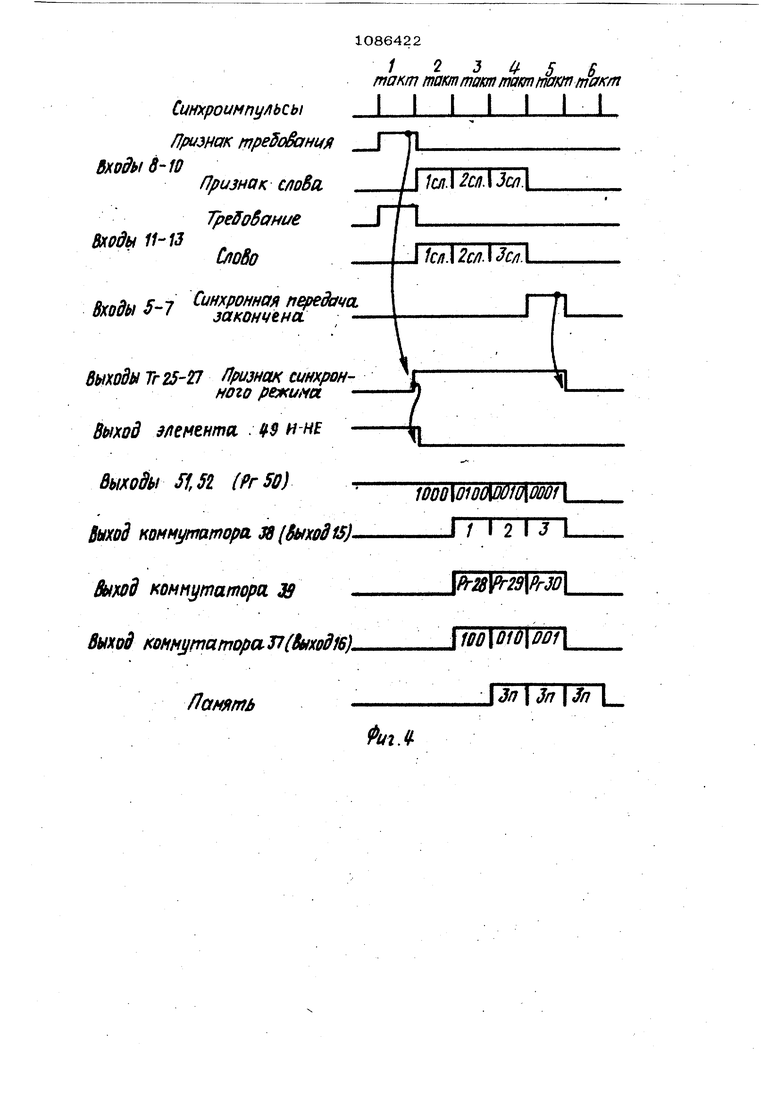

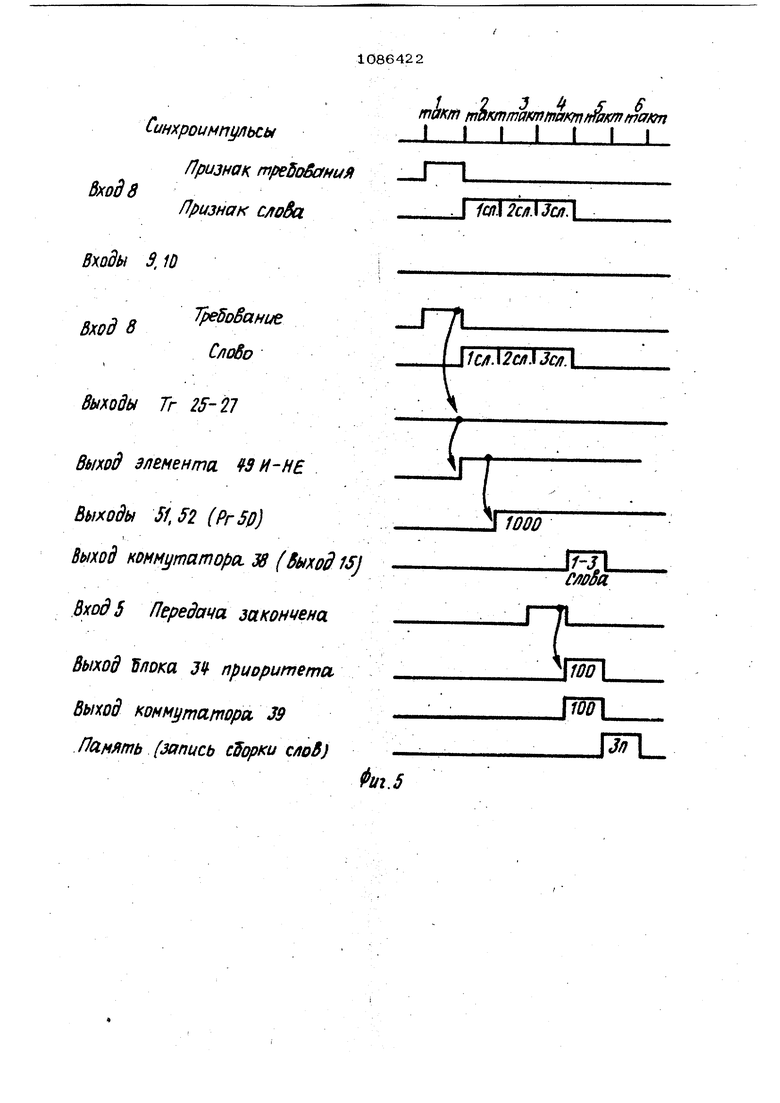

Изобретение относигея к обпасги вычтюлигепьной техники и может быть ис пользовано дпя правления обменом информации между каналами ввода-вывода и памятью цифровых вычислительиых систем. Известны устройства 1 и 2 для уп раьпения обменом информации между не сколькими каналами ввода-вывода, каждый из которых занимает определенное положедае в приоритетном ряду на обращение к памяти, и памятью электронной цифровой вычислительной машины (ЭЦВМ). Известно устройство для управления ка11алами ввода-вывода, содержащее входной буфер, вкод которого -соединен с выходами каиалов ввода-вывода, а выход - с входом памяти ЭЦВМ, блок управления подключением одного из кана лов ввода-вывода к входу входного буфе ,ра, блок управления выбором ячейки запясн йкодного буфера, блок управления Ьыборсм ячейки чтения входного буфера, выходной буфер, вход которого соединен fc выходом памяти ЭЦВМ, а выход - с входами каналов ввода-ёывода, блок управпешш выбором ячейки чтения ВЫХОА ного буфера Cl L На шлходе указанного устройства фор руегся данных в веде совокупнос слов, посгупаюших на вход устройства от одного кйяапа ввода-вывода. Наиболее близким к изобретению явля ется устройство для управлетя каналамн ввода-вывода, содержащее группу селекторов, первые %оды которых соеди вевы с входами первой группы устройстве, а вторые входы черев соответС11 уххШ1е дешифраторы соодивены с Bxt яамя второй группы устройства, группу регистров для сборки, входа каждого ,нзког(фых соединены с выходами соотватствумпего селектора, первый коммуipBTOp (данных), входы которого соеддане вы с перВ1лмп1 выходами соответствующих регистров для сборки, а выход с выходом устройства, второй коммутатор (требований), вкоды которого соединены с вторыми выходами соответствукхцих регистров для сборки, а пе вый выход - с вторым выходе устройctt a, блок приоритета, вход которого .соедввен с входакга устройства, а выход - с входами первого коммутатора и взсодом Второго коммутатора, регистр вомера канала, вход которого сое|динев с Вторым выходом йгорого коммутатора, а выход - с третьим выходом устройства, выходной регистр, вход которого соединен с входом устройства, а выход - с четвертым вькодой ус тройства С 2 J. В известном устройстве ввод данных от каналов ввода-вывода в память ЭЦВМ происходит слеауюшим образом. От соответствующих мультиплексор роВ каналов ввода-вывода через селекторы в регистры для сборки поступают последовательно требование на обмен данными, в состав которого входит адрес размещения данных в памяти ЭЦВМ, и несколько слов данных от одного канала ввода-вывода. Максимальное количество слов равно количеству слов в формате обращения к памяти. После того, как какой-либо регистр для сборки заполнен, его содержимое (требование и данные) через коммутатор требований (требование) и через коммутатор данных (данные поступает на второй и первый выходы и естногр устройства И далее в память ЭЦВМ. В случае, если ли заполнены несколько регистров для сборки, в память под управлением блока приоритета передается с.одержимое старшего по приоритету регистра для сборки. . Таким образом, на выход известного, устройства, и далее в память поступают данные, представляющие собой совокупность слов, поступивших на вход известного устройства только от одного канала ввода-вывода. Однако для применения известного устройства в таких областях, как обработка радиолокационной информации, управление воздушным движением, прогноз погоды и в других, связанных с обработкой больших массивов информации в реальном масштабе Времени, необходимо в каждой строке памяти ЭЦВМ и, следовательно, на выходе известного устройства иметь данные в виде совокупности слов, поступающих одновременно на входы устройства и характеризующих состояние объекта в некоторый момент времени. Недостатком известного устройства является поступление на выход устройства данных только в виде совокупности слов от одного мультиплексора. Цель изобретения - повьпиение быстродействия устройства. Поставленная сель достигается тем, что в устройство для управления каналами ввода-вывода, содержащее селекто- 3l ры, первые входы которых являются Входами первой группы устройства, а вторые входы соединены о выходамн соответствующих деигафраторов, входы которых являются входами второй группы устройства, Входы группы селекторов соединены с информационными входа ми регистров первой группы, выходы которых соединены с информационными входами первого коммутатора, управпяюший вход которого соединен с выходом блока приоритета, входы группы которого являются входами трьетьей группы устройства, а вход соединен с входами синхронизации первого и второго регистров, регистров первой и второй групп и является первым входом устройства, выходы селекторов соединены с информационными входами соответствующих регистров второй группы, выходы которых соединены с информационными входами второго коммутатора, первый вькод которого является первым выходом устройства, а второй выход соединен с информахдаонным входом первого регистра, выход которого является вторым вытсодом устройства, инфо ялационный вход второго регистра является вторым входом устройства, а выход является третьим выходом устройства, введены третий и четвертый коммутаторы, триггеры и распределитель импульсов, входы группы которого соедин ны с выходами триггеров, входы синхро зации которых явп$потся первьп входом устройства и соединены с входом распределителя импульсов, первый выход которого соединен с управлякяцим входо третьего коммутатора и первым информационным входом четвертого коммутато управляющий вход которого соединен с вторым выходом распределителя импульсов, второй информационный Вход четвертого коммутатора соединен с выходом блока приоритета, а выход Со единен с управляющим входом второго коммутатора, выход первого коммугаг ра с оединен с первым ввформационвым входом третьего коммутатора, второй, третий в четвертый информаднонные вкоды которого соединены соответствее но с первыми, вторыми в третьими выходамв регистров первой группы, выход третьего коммутатора является четвертым выходом устройства, вторые выход селекторов соединены с едишчвымв входами триггеров, нулевые входы кото рых являются входами четвертой груяпы устройства. 22, 4 На фиг. 1 представлена функциональная схема устройства для управления каналами ввода-вывода; на фиг. 2 схема блока приоритета; на фиг, 3 схема распределителя импутшсов; на фиг. 4 - временная диаграмма работы устройства при вводе информации в синхронном режиме; на фиг. 5 - то же при вводе информации в асинхронном режиме (для одного канала); на фиг. 6 - то же, при ыгоде информации (для одного канала). Устройство (фиг. 1) соаержвт второй вход 1, входы 2, 3 и 4 третьей группы, входы 5, 6 и 7 четвертой группы, входы 8, 9 и 1О второй группы, входы 11, 12 в 13 первой группы, первый вход 14, четвертый выход 15, первый выход 16, второй выход 17, третий выход 18, дешифраторы 19, 2О и 21, селекторы 22, 23 в 24, триггеры 25, 26 и 27, регистры 28, 29 и 30 второй группы, регистры 31, 32 в 33 первой группы, блок 34 приоритета, распределитель 35 импульсов, первый 36, второй 37, третий 38, четвертый 39 коммутаторы, второй 40 и первый 41 регистры. Блок 34 приоритета (фиг. 2) содержит триггеры 42, 43 в 44, установочные входы которые соединены с входами 2, 3 в 4 третьей группы устройства, а сишсровходы соединены с первым входом 14 устройства, элементы НЕ 45 и 46, Элементы И 47 в 48. Распределитель 35 вмпуль ов (фиг. 3) содержит элемент И-НЕ 49, регистр 50, первый 51, второй 52 выходУ. Устройство работает спедукшшм образом. Ввод ввформадвв в память может осу-; шествляться в двух режвмах: синхронном в асвнхронвом; вывод ввформашга вз памяти в канал - только в асвнхронном режвме. Ввод внформацви в свнхровяом (см. фвг. 4). На выходе устройства форкшруется строка даввых в ввде совокупносгв трех слов (вектора), одновременно поступающих ва вкод устройства от трех синхронно работающих мультвплексодое каналов ввода-вывода (не изображены). Первый такт.Трв мультиплексора вьшают на входы 11, 12 в 13 требованвя ва ввод даввых, а ва входы 8, 9 в 1О признакв требованвя (структура требова. ВИЯ мультиплексора состоит из поля признака режвма; поля номера кавала. 51 поля кода операшга (ввод-вывод), поля адресе памяти, поля ключа доступа к памяти). Под управлением сигнала с выхода дешифратора 19 (20,21) признак режима требования поступает на второй выход селектора 22 (23,24), а остальные поля требьвания - на первый выход селектора 22 (23,24). Второй такт. После прохождения синхроимпульса к входу устройства три гер 25 (26,27) устанавливается в сос тоннве , определяалое признаком режимов требования (при синхронном режиме - состояние ), на регистре 28 (29,30) запоминаются остальные Требования; три мутшгиплексора вьадают на Бходы 11, 12 и 13 по одному слов данных , а на входы 8, 9 и 1О - признаки данных, которые указывают, что эги слова должны быть записаны в п I вые области регистров 31, 32 и 33. Под управлением сигнала с выхода дешифратора 19 (2О,21) слово данных поступает на выходы группы селекторе 22 (23,24). Третий такт. После прохождения син хроимпульса в перЁой области каждого из регистров 31,32 и 33, соогветству юшей первому выходу регистра, запоми нается по одному слову данных. Совокупность этих слов поступает на третий вход третьего коммутатора 38. Наличие (с выходов триггеров .25, 26 и 27) на всеос Екодах распределителя 35 импульсов обусловливает его работу в динамическом сдвиговом режиме, характеризукяцемся тем, что на его втор( выходе постоянно присутствует код, подаваемый ие управляющий вход четвертого коммутатора 39 и обеспечи ваюций прохождение в этом коммутатор информапив с первого информапионнотч) вхрда на вьосод (для управления вторым коммутатором 37); на первом вьхходе распределителя 35 импульсов в течение трек последовательных тактов (после прохождения очередных синхроимпульсов) появляются коды, обеспечивающие прохождение информации на выход коммутатора 38 последовательно с второго третьего и четвертого входов и на выход коммутатора 37 - информашга с его входов. Таким образом, в третьем такте на выход 15 устройства выдает ся совокупность слов, поступающих по «торой группе выходов (т.е. слов, храг няпшхся в первых .областях регистров 31, 32 и 33), Q на выход 16 устройс выдаются поля кодя (шерации, адреса 22 памяти и ключа доступа к памяти требог ваггия от первого мультиплексора, хранящегося на регистре 28, Мультиплексоры выдают на входы 11, 12 и 13 первой группы устройства по второму слову данных, а на соответствующие входы 8, 9 и ib второй группы устройства - признаки данных, указываквдие, что эти слова должны быть записаны во вторые области данных регистров 31, 32 и 33 первой группы. Четвертый такт. Раббта устройства аналогична работе в третьем такте. На выходе 15 устройства формируется строка данных из вторых слов мульпшлекуfcopoB, на выходе 16 - поля кода опёраШ1И адреса памяти и ключа доступа к памяти требования с регистра 29. Пятый такт. Аналогично третьему и четвертому тактам пятый такт характеризуется Ёьвдачей на выход 15 устройства строки данных (из третьих слов мультиплексоров), а на выход 16 устройства соответствующих полей требования (с регистра 30). На вхолы 5. 6 и 7 четвертой гру11пы устройства поступают сигналы Синхронная передача закончена, которые устанавливают триггеры 25, 26 и 27 по второму ВХОДУ (Установка в О) в состояние О. Распределитель 35 импульсов работает следующим образом. Признаки режима (синхронный - , асинхронны - О) поступают с выходов триггеров 25, 26 и 27 на вход элемента И-НЕ 49, на выходе юторого в синхронного приема формируется сигнал О, устанавливающий универсальный сдвиговый регистр 50 в режим сдвига. Таким образом, в третьем такте на выходах 51 -и 52 регистра 50 формирует ся код 01ОО, в четвертом - ОО10, в пятом - ООО1, и, следовательно, на . ром выходе 52 распределителя 35 присутствует сигнал О, а на выходе 51 последовательность кодов 100, 010, 001. Сигнал О с второго выхода 52 используется как управлякший для четвертого коммутатора 39 (разрешает прохождение управлякших кодов 10О, 010, ОО1 на его выход для управления коммутатором 37), а последовательность, кодов 1ОО, О10, ОО1 обеспечивает выдачу с коммутаторов 37 и 38 требований от первого, второго и третьего мультиплексоров одноврйиенно с совокупностями первых, вторьк и третьих слов, соответственно, в третьем, четвертом и пятом тактах. Ввод информации в асинхронном режи ме, (фиг. 5) происходит следующим образом. Первый такт. Мультиплексор выдает требование на ввод данных на вход 11 (12,13), а признаки требования - на Вход 8 (9, 10). Поля требования номер канала, когда операции, адреса памяти и ключа доступа к памяти записываются в регистр 28 (29,30), а поле признака режима устанавливает триггер 25 (26, 27) в состояние О. Нулевой сигнал с выхода триггера 25 (26,27), поступм на вход распределителя 35, обусловлива ет формирование на выходе элемента И-НЕ 49 сигнала 1, запрещающего режим сдвига и разрешающего параллель ный прием информации в регистр 50. Следовательно, после прохождения синхроимпульса на выходе 52 распределителя 35 формируется сигнал 1, а на выходе 51 - код ООО. Выходной сигнал I в качестве управляющего сигнала, поступающего на коммутатор 39, разрешает прохождение управляющего кода с выхода блока 34 приоритета на управ ляющий вход второго коммутатора 37. Код ООО с первого выхода 51 распреде лителя 35 поступает на управляющий вход третьего коммутатора 38, обеспечивая прохождение на выход коммутатора 38 и, следовательно, на выход 15 устройства информации с первого входа третьего коммутатора 38, которая поступает с выхода первого коммутатора 36, управляемого (так же как и комму тор 37) кодом с выхода блока 34 хф оритрета. Второй такт. Мультиплексор вьщает первое слово данных на вкод 11 (12, 13) устройства и признак данных - на ЕКОД 8 (9, 10), который указывает, в какую область регистра 31 (32, 33) записать это слово данных. Признак данных поступает на дешифратор 19 (2О,21), обеспечивая прохождение первого слова данных через селектор 22 (23,24) в первую область регистра 31 (32,33). Если осуществляется ввод только одного слова данных, то во втором такте на вход 2 (3,4) устройства поступает сигнал Передача закон чена. Если осуществляется ввод двух (или трех) слов, то в третьем (или четвертом и третьем) такте повторяетс процедура приема очередного слова данных Во вторую (третью) область данных регистра 31 (32,33), а сигнал Передача закончена поступает соответственно в третьем (четвертом ) такте. Поступление этого сигнала на вход блока 34 приоритета означает, что сборка данные закончена. На выходе блока 34 приоритета устанавливается код, разрещающий вьздачу на выходы 15 и 16 устройст ва слов данных и полей кода операции, адреса памяги и ключа доступа к памяти от одного и того же мультиплексора. Если иэ-за асинхронности работы сборка данных закончена сразу в нескольких регистрах, то блок 34 приоритета устанавливает коммутаторы 36 и 37 в такое состояние, при котором на выходы 16 и 15 устройства поступает содержимое только одного из регистров 28, 29, 30 и соответствукяыего ему регистра 31 32, 33 для того мультиплексора, который является старшим по приоритету. Блок 34 приоритета работает следующим образом. Сигналы Передача за кончена с входов 2,3 и 4 устройства поступают на входы блоки 34 и далее на входы установки в 1 триггеров 42, 43 и 44 соответственно. В следующем такте (после прохождения синхроимпульса с входа 14 устройства) на выходе триггера 42, эле гентов И 47 и 48 формируется код 100 (010, 001), который поступает на управляющий вход коммутатора 36 и (через кэммутатор 39) на управляющий вхощ коммутатора 37, обеспечивая прохождение через них в данном такте данных и требования того мультиплексора, для которого поступил сигнал Пв редача закончена. Если одновременно пришло несколько сигналов Передача закончена, то старший по приоритету сигнал с выхода триггера блокирует вьщачу младшему (например, сигнал с выхода триггера 42 через элемент НЕ 45 и элемент И 47 блокирует выдачу сигнала с выхода триггера 43). С выходов блока 34 приоритета сигналы, заведенные на установки триггеров в О, сбрасывают после прохождения синхроимпульса тот триггер, который сформировал 1 на выходе блока 34 приоритета. Выход информации в асинхронном режиме (фиг. 6) производится аналогично оду в асинхронном . режиме в отношении приема требований и формирования сигналов управления коммутаторами. Отличие заключается ь направлении передачи m«t opMaioiB: с аькода 16 Зстройства в память передаются поля кода опералив; адреса памяти, кпбзчй доступа к памяти, требования, а поле номера канала запоминается на регистре 41, данные считанные из памяти по выданному требованию, поступают 18Г7 1 22 на вход 1 устройства и далее принимаются по синхроимпульсу в выходной регистр 40. Таким образом, на выходах 17 и 18 устройства появл51ются номер канала и данныеГ предназначенные для этого канала, соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Мультиплексный канал | 1980 |

|

SU868744A1 |

| Устройство для сопряжения каналовВВОдА-ВыВОдА C уСТРОйСТВОМ упРАВлЕНияОпЕРАТиВНОй пАМяТью МНОгОпРОцЕССОР-НОй ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU822168A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1462341A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ КАНАЛАМИ ВВОДА-ВЫВОДА, соаержашее- селекгоры, первые входы Koropjx являюгся входами первой группы усгройсгва, а вгорые входы соединены с выходами соогвегсгвуюших дешифраторов, входы которых являются входами ,В ГОрОЙ группы ус рОЙСТ,;: ВЫХОДЫ группы сепекгоров соединены с информационными входами регистров первой группы, выходы когорых соединены с информационными входами первого коммутатора, управляющий вход которого соединен с выходом блока приоритета, входы группы которого являются входами третьей группы устройства, вход со единен с входами синхронизащга первого и второго регистров, регистров первой и второй групп и является первым входом устройства, первые выходы селекторов соединены с информационными входами соответствуюшгос регистров второй группы, выходы которых средянешл с ивфоръ апионными входами второго коммутатора, первый выход которого является первым выходом устройства, а второй выход соединен с информационным входом регистра, выход которого является вторым выходом устройства, информационный вход второго регистра является вторым входом устройства, а выход является третьим выходом устройства, отличающееся тем, что, с целью увеличения быстродействия, в неЬо введены третий и четвертый коммутаторы, триггеры и распределитель импульсов, входы группы которого соединены с выходами триггеров входы синхронизации которых являются лвр&ым входом устройства и соединены с входом распределителя импульсов, выход которого соединен с уп(Л равляющим входом третьего коммутатора и первым информационным входом четвертого коммут1атора, управляющий вход которого соединен с вторым выходом распределителя импульсов, второй информационный вход четвертого коммутатора соединен с выходом блока приоритета, а выход соединен с управлякядим входом второго коммутатора, выход первого коммутатора соединен с информационным входом третьего коммутатора, второй, третий и четвертый информационные входы которого соединены соответственно с первыми, вторыми и третьими выходами регистров первой группы, выход третьего коммутатора является четвертым выходом устройства, вторью выходы селекторов соединены с единичными юсодами триггеров, нулевые входы которых являются входами четвертой группы устройства.

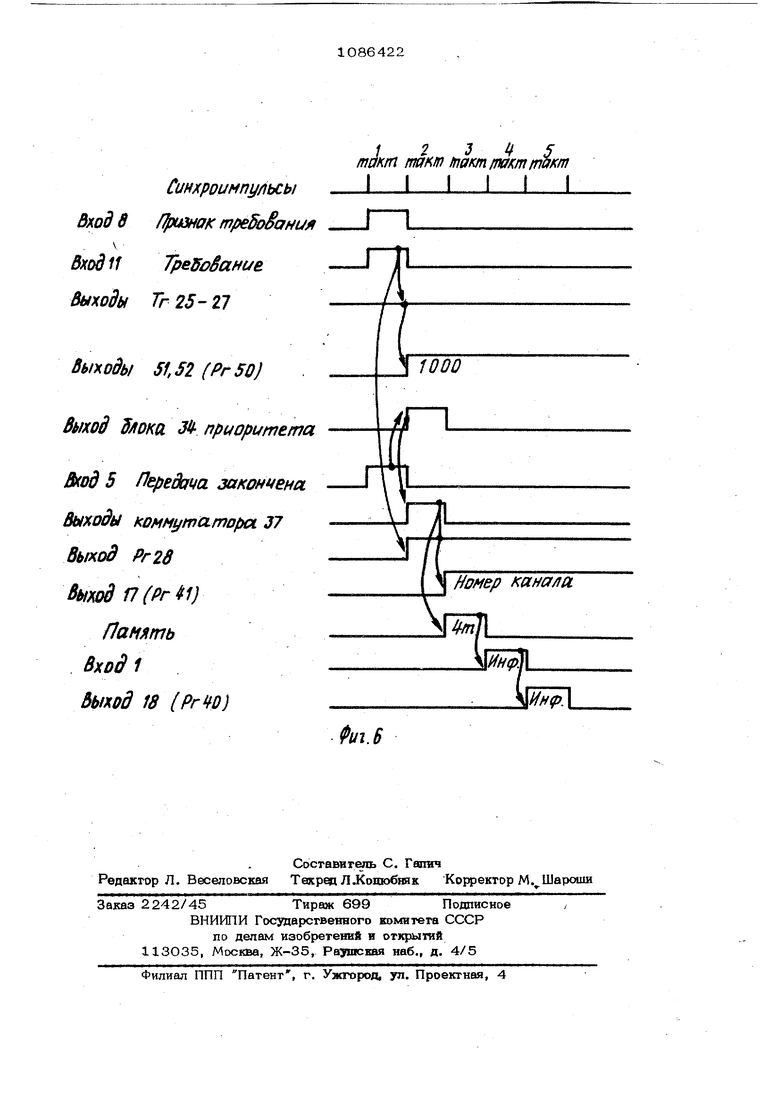

Фиг.З Синхроимпульсы тредоВания Ь)(оды B-W Признак cfloBa, TpcSoBoHue Входы 11-13 CfloBo Купйи f-7 (ин)(ронная передача, бхооы у / jaKOHveHoL ВшоЬы Tr25-Z7 признак синхронного режина Вшод /1емента -Jj/iSH-HE BbiJ(oSbi SUi (PrSO) ВыхоЗ коммутатора (выход ts).

Вылод KOMhi mamopfi 3S

ВыхоЗ коннлтатораУ7{$ыход№)

Память 1О864 / так

i m 23 prjoi

m Dio ffoii

JJ/7|J/7l//7 L 2 5 S такт такт такт пизкт такт II II II /с/7.12сШсл1 1c/i.2c/f.Jc/.l WDB 010WJO 0001 J / I 2 IJL

Синхроимпульсы

признак треЬобания

дхоЗз П/ изнак САоВа

Вкоды 3.1й ТреЬоВание Вход 8 C/ioBo Выводы Тг 25-27 Выход элвмента. 3 И-не (odbf 51,52 (Рг50) . , Выход коммутатора, 38 (Bbixod Вход 5 Передача uKOHt BHCL Выход Ъпйки Зl приоритета Bbiwd коммутаторл 39 Память (запись сЪорки c/ioB)

1 2 J S ff такт такттактгпактти п/псгш

ЛI I I I II

J , C/r.2cfl.lJc/f.l ПШ J74l ста 1 1ш1 Ш jiTL

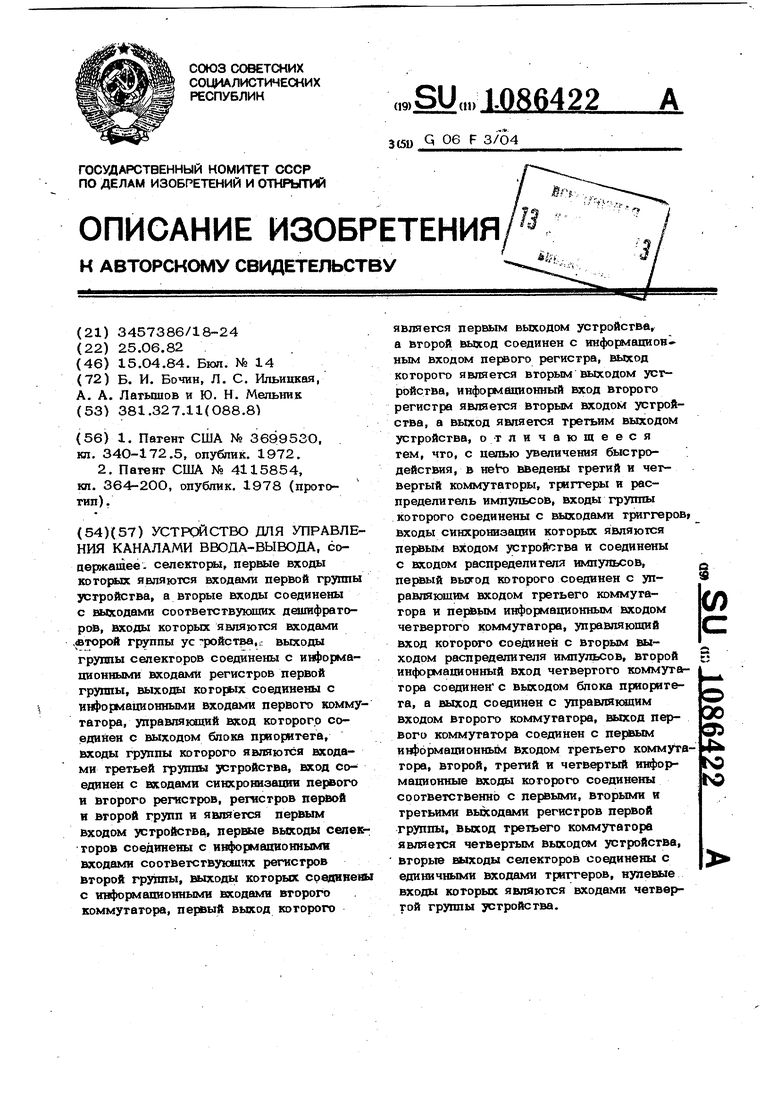

CuHxpouMny/ibCbi

Вмд 8 f)U3HaK m/jeSoSanuA

Вход If Требование

Выходы Tr25-27

дшодь/ 51.52 (Рг50) Выход лока J приоритета

Вход 5 Передаца закончена. Выходы коммутатора 37 ВшоВ Рг28 Bbij(od Л {Рг 1}

Нанять Bxodi

Выход 18 PrtfOj

Фиг. 6

J 2 3 S такт такт цнгкт такт

I I I I t 1

1000

Номер кана/}л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ВСЕСОЮЗН.А^Я | 0 |

|

SU369953A1 |

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Пагенг США № 4115854, кп | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1984-04-15—Публикация

1982-06-25—Подача