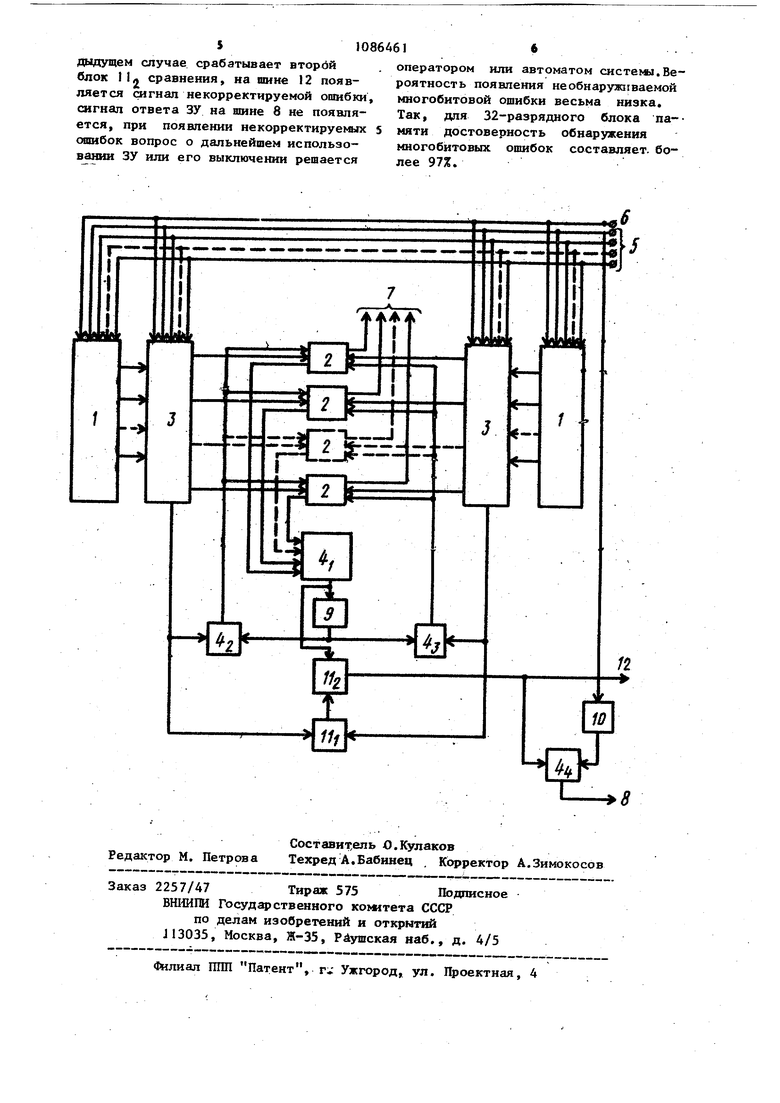

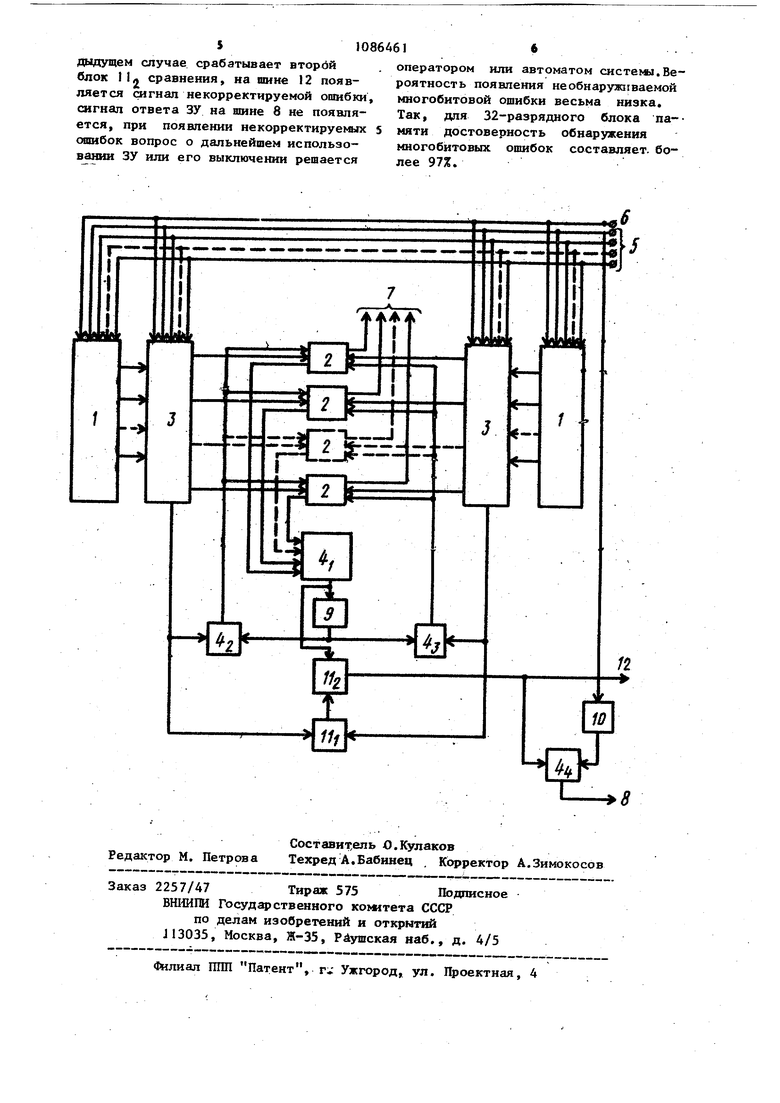

Изобретение относится к вычислительной технике, в частности к запокмнающим устройствам. Известно запоминающее устройство с самоконтролем, использующее избыточное кодирование по коду Хэмминга для обнаружения одно- и двухбитовых ошибок, исправления однобитовых ошибок LIJ . Недостатками этого устройства яв лямтся отсутствие возможности достоверного обнаружения многобитовых ошибок, исправления двух- и многобитовых ошибок, возможность постано вки ложного диагноза в случае появ ления многобитовой сяпибки, восприни маемой устройством контроля во многих случаях как однобитовая ошибка или отсутствие ошибки. Наиболее близким по технической сущности к предлагаемому является зaпo в нa:oщee устройство с самоконтр лем, содержащее блоки памяти,выхо ды которых соединены с nepBUhW входа1«1 блоков поразрядного сравнения и первыми входами блоков контроля выходы блоков контроля я блоков поразрядного сравнения подключены к входам блока формирования сигнала отказа, выходные и управляющие шины, блок задержки строба считывания . Однако это устройство не исправляет двухбитовые и другие кратные двум ошибки. Следует отметить,что по мере развития технологии БИС и связанного с этим повьш1ения степени интеграции происходит переход к изготовлению все в больших количествах Вис ЗУ с многоразрядной орган зацией (4.8.16 разрядов). В растоящее время все или почти все БИС ГОУ, ППЗУ, ЭгаВУ выпускаются с разрядностью 8 или 16, появляется все большее количество ВИС ОЗУ с разрядностью 4 или 8 (например, статические ОЗУ 1Кх4, 1Кх8, динамические ОЗУ 1бКх4 и т.д.).. Дпя таких ВИС резко повышается вероятность от каза целого многоразрядного слова, а следовательно, и появления многобитовой ошибки. Целью изобретения является повышение надежности запоминающего устройства за счет исправления двух битовых ошибок и ошибок кратных дву Поставленная цель достигается тем,что в запоминающее устройство с самоконтролем,содержащее блоки памяти и блоки контроля, одни входа которых являются входом устройства, выходы блоков памяти соединены с другими входами блоков контроля, одни выходы которых соединены с входами блоков поразрядного сравнения, первые выходы которых являются выходом устройства,введены первый, второй, третий и четвертый элементы И элемент задержки, первый и второй блоки сравнения, инвертор,причем другие выходы блоков контроля подключены к входам первого блока сравнения и первым входам второго и третьего элементов И, выходы которых соединены с соответствующими входами блоков поразрядного сравнения, вторые выходы которых соединены с входаьв первого элемента И, выход которого подключен к первому входу второго блока сравнения и к входу инвертора, выход которого соединен с вторыми входа ш второго и третьего элементов И, выход первого блока сравнения подключен к второму входу второго блокасравнения, выход которого связан с первым входом четвертого элемента И,второй вход которого подключен к выходу элемента эадержгки, вход которого является управляющим входом устройства, выходы второго блока сравнения и четвертого элемента И являются кoнтpoльны « выходами устройства. На чертеже изображена принципиальная схема предпагаемого устройства. Устройство содержит два блока 1 памяти, блоки 2 поразрядного сравнения, блоки 3 контроля, четыре элемента И 4, 42.42,4 ,входные шины 5, управляющую шину 6, выходные шины 7, первую контрольную шину В, инвертор 9, элемент 10 задержки,два блока 1Ц и 112 (Р внения, вторую контрольную шину 12. Устройство работает следующим образом. На входы двух блоков 1 памяти и двух блоков 3 контроля по коду Хэмминга поступают коды адреса, числа команд по входным шинам 5 и аапрос по шине 6 от арифметического устройства (на чертеже не показано) . Считанная из блоков памяти информация контролируется блоками 3 контроля по коду Хэмминга. В случае отсутствия ошибок в информации, считанной из обоих блоков 1 памяти, или наличия в ней однобитовой ошибки, кректируемой блоками 3 контроля по кду Хэмминга, на входах блоков 2 поразрядного сравнения устанавливается истинная информация, а на каждом из их выходов устанавливается сигнал сравнения (логическая 1). При этом на выходе первого элемента И 4 устанавливается также сигнал логической 1, соответствующий исправной работе запоминающего устройсва. На шине 8 по истечении времени необходимого на считавание информации, ее контроль и, если нужно, кор .ректировку,установится сигнал Ответ ЗУ. По этому сигналу арифметическое устройство может принять и использовать достоверную информацию, установившуюся н.а выходных шинах 7.

В процессе работу ЗУ возможно появление двух- или многобитовых ошибок:

отказ отдельных двух и более ячеек памяти в одном адресе;

отказ целого слова или групп слов в многоразрядной БИС;

отказ целой БИС с многоразрядной организацией;

Отказ дешифратора многораэряд,ной БИС, приводящий к считы-ванию информации из другого адреса или одновременно из двух адресов;

отказ схем управления одного из блоков памяти (адресные схемы, схеM t выбора кристалла, схемы регенерации и другие) и т.п.

В любом из этих случаев считанная из двух блоков памяти информация оказывается неидентич|{ой и rte может быть скорректирована блоком контроля по коду Хэмминга. Поэте-. У на одном .двух и более выходах блока 2 поразрядного сравнения устанавливается сигнал несравнения (логический О), вследствие чего на выходе первого элемента И 4( установится сигнал ошибки, .соответствующий также логическому О. Одновременно сигнал ошибки устанавливается на выходе одного или двух (если ошибка в обоих блоках памяти) блоков 3 контроля по коду Хэммкига.

Дальнейшая работа устройства определяется характером обнаруживве мой при контроле ошибки.

1. Двух- или многобитовая ошибка имеется в одном из блоков 1 памяти . При этом на первый вход второго и третьего элементов И 4я и 4 подается сигнал ошибки от первого элемента И 4f через инвертор 9, а на второй вход одного из элементов И 4л,4а- сигнал ошибки от соответствующего блока 3 контроля.по коду Хэмминга, элемент И срабатывает и запрещает считывание информации в данном такте от неисправного блока. На выходных шинах 7 устанавливается информация, считанная из другого исправного блока. Сигнал запроса,задержанный на элементе 10 задержки, через четвертый элемент И 4 поступает на шину 8.

t 2, Неисправность обнаруживается в обоих блоках 1 памяти. Сигнал ошибки устанавливается на выходе первого элемента И 4 и на выходах обоих блоков 3 контроля по коду Хзмминга. В этом случае срабатывают второй и третий элементы И 4 и 4, запрещая выдачу информации от обоих блоков I памяти на выходные шины 7. Одновременно с выходо1з сигналов ошибок блоков 3 контроля по коду Хэмминга поступает одинаковая информация на оба входа первого блока 1Ь сравнения j на выходе которой устанавливается лошческая 1, поступающая на первый вход второго блока 11 сравнения,на другой вход которого подан сигнал ошибки от элемента И 4f (сигнал логического О). На выходе второго блока I1я сравнения,соединенного с шиной 12 сигнала некорректируемой ошибки, устанавливается логический О, свидетельствукщий об отказе ЗУ. Сигнал некорректируемой ошибки поступает на четв ертый элемент И 4 и запрещает вьщачу сигнала на шину 8.

3. Одной из возможных реакций блока контроля по коду Хэмминга на многобитовую ощибку является ее необнаружение. Тогда при появлении необнаруткиваемой многобитовой ошибки в одном из блоков 1 памяти сигнал ошибки на выходе соответствующего блока 3 контроля по коду Хэмминга отсутствует так же, как и на другом блоке контроля, подключенном к исправному блоку памяти, однако на выходе первого элемента И 4 при этом сигнал ошибки вырабатывается. Как и в пре

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Запоминающее устройство с исправлением дефектов и ошибок | 1987 |

|

SU1536445A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1985 |

|

SU1274006A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1501171A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1251188A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1368923A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ОТКАЗОУСТОЙЧИВОСТИ | 2005 |

|

RU2327236C2 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU888203A1 |

| Динамическое запоминающее устройство | 1977 |

|

SU701354A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

ЗАЛОЬМНАИЩЕ УСТРОЙСГЮ С САМОКОНТРОЛЕМ, содержащее блоки памяти и блоки коитроля, одни входы которых являются входом устройства, выходы блоков памяти соединены с другими входами блоков контроля,.одни выходы которых соединены с входамиблоков поразрядного сравнения,первые выходы которых являются выходом устройства, отличающее с я , тем, что, с целью повышения надежности устройства за счет исправле- , ния двухбитовых и других ошибок, пфатных двум, в него введены первый,, второй,третий и четвертый элеменп / ..v,,: Ii3 И, элемент задержки, первый и второй блоки сравнения, инвертор, причем доурие выходы блоков контроля подключены к входам первого блока сравнения и первым входам второго и третьего элементов И, выходы которых соединешл с соответствующикм входами блоков поразрядного сравнения, вторые выходы которых соединены с входами первого элемента И, выход которого подключен к первому входу второго блока сравнения и к входу инвертора, выход которого соеданен с вторыми входами второго и третьего элементов И, выход первого блока сравнения подключен к второму входу второго блока сравнения, вы(Л ход которого связан с первым входом , с четвертого элемента И, второй вход которого подключен к выходу элемента задержки, вход которого является управлякщим входом устройства, выходы .:второго блока сравнения и четвертого элемента И являются контрольными выходами устройства. 0005 4ib О5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электроника, 1980, 9 , с | |||

| Цилиндрический сушильный шкаф с двойными стенками | 0 |

|

SU79A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU696545A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1984-04-15—Публикация

1982-09-06—Подача