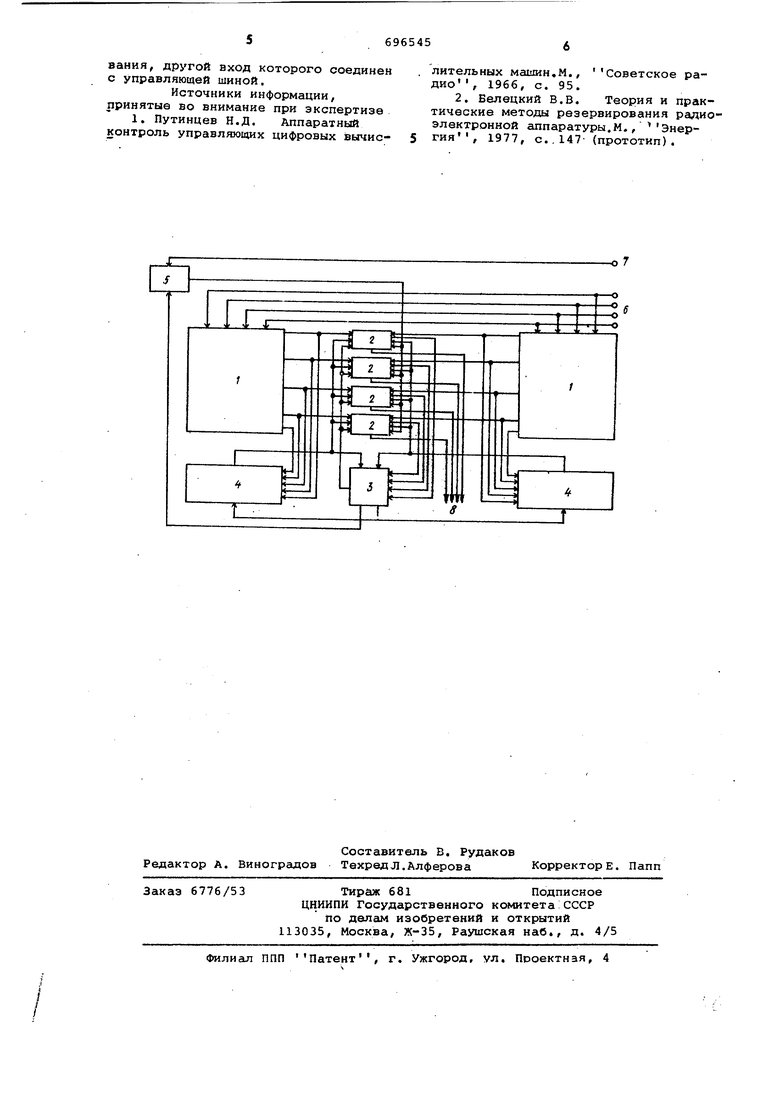

Изобретение относится к области запоминающих устройств. Известно запоминающее устройство с само онт 5олем, в котором контроль функционирования устройства осуцест ляется путем образования свертки и сравнения ее с информацией в контрольном разряде 1. Однако, это устройство имеет невысокую скорость работы. Наиболее близким по технической сущности к предложенному является запоминающее устройство с самоконтролем, содержащее блоки памяти, выходы которых подключены к первым вводам соответствующих блоков контроля, блок формирования сигнала отказа, выходные и управляющую шины 2 Однако это устройство теряет быстродействие при контроле исправ ности и локализации неисправности узлов устройства, основанного Тс1кже на образовании свертки. Цель изобретения - повышение быс родействия устройства. Это достигается тем, что устройство содержит блок задержки строба считывания и блоки поразрядного сра нения, входы которых подключены соответственно к выходам блоков п мяги, блоков контроля и блока згщержки строба считывания, а выходы - к выходным шинам и одним из входов блока формирования сигнала отказа, другие входы которого соединены с выходами блоков контроля. Выходы блока формирования сигнала отказа подключены соответственно ко вторым входам блоков контроля и одному из входов блока задержки строба считывания, другой вход которого соединен с управляющей шиной. На черте: е изображена блок-схема предложенного устройства. Устройство содержит блоки памяти 1, блоки-поразрядного сравнения 2, блок формирования сигнала отказа 3, блоки контроля 4, блок задержки строба считывания 5, входные шины б, управляющую шину 7, выходные шины В. Выходы блоков 1 подключены к первым входам соответствующих блоков 4. Входы блоков 2 подключены соответственно к выходам блоков 1, 4 и 5, а выходы - к шинам 8 и одним из входов блока 3, другие входы которого соединены с выходами блоков 4, Выходы блока 3 подключены соответственно ко вторьам входам блоков 4 и одному из входов блока 5, другой вход которого соединен с шиной 7, служащей для подачи строба считывания. Устройство работает следующим образом. На входы двух блоков памяти 1 поступают сигналы кода адресов, числа. Команд и запроса от арифметического устройства (на чертеже не показано), в том числе сформированный в арифметическом устройстве код контрольного разряда. В случае исправной работы обоих блоков 1 на выходе каждого бло ка поразрядного сравнения 2 устанавл вается сигнал логическая 1. и счи танная с каждого разряда обоих блоков 1 информация поступает одновременно, через блоки поразрядного сравнения 2 на вход арифметического устройства. В случае же неисправности одного из блоков 1 произойдет несовпадение информации хотя бы в одном и разрядов, и сигнал несовпадения с од ного или нескольких блоков 2 поступит на вход блока 3, который вырабатывает сигнал запуска блоков контроля 4, на входы которых также подана информация, считанная из соответствующих блоков 1. По окончании операции свертки ее результат сравнивается с кодом, записанным в контрольном разряде блока 1. На выходе блока контроля 4 в случае несовпс дения результата операции свертки с контроль ным кодом установится сигнал неисправности блока 1. Этот сигнал поступает на блок индикации отказа {на чертеже не показан) на пульте оператора, на входы блоков поразрядного сравнения 2 и блока 3, При этом происходит блокирование схем поразрядно го сравнения во всех блоках 2, блокирование выходов неисправного блока 1 и сброс в исходное состояние блока 3i В результате на выходе каждого блока 2 устанавливается информация, соответствующая считанной только из исправного блока, и отключаются блоки поразрядного сравнения 2. Информа ция с выходов блоков 2 подается на .шины 8. Для исключения возможности считывания неправильной информации в момент выполнения операции свертки предусматривается блок задержки стро ба считывания 5, который обеспечивае задержку формирования строба на время выполнения операции свертки по команде от блока 3, В случае возникновения неисправности блока 1 возмож ны следующие варианты дальнейшего ис пользования устройства: а) ремонт, возвращающий устройств в исходное состояние (в этом случае из устройства могут быть исключены блок 5, а также схемы блокирования выходов неисправного блока и схемы блокирования поразрядного сравнения в блоках 2) ; б) дальнейшая работа с контролей в каждом такте с соответствующим снижением быстродействия (для этогО варианта не требуются цепи, обеспечивающие блокирование блоков 2, но необходимо ввести сброс блоков 4 в каждом такте, например, от последующего запроса); в) дальнейшая работа, в течении некоторого времени, например, до окончания решения задачи, с максимальным быстродействием, но без контроля оставшегося исправного блока 1 модуля (в этом случае используются все блоки, но исключается сброс блоков 4). 35ЛОК поразрядного сравнения строится на относительно простых элемен.тах, содержащих 6-7 вентилей, поэтому может быть реализован в виде одной микросхемы. В эту же микросхему могут быть включены также блок 5 и шины 6 и 7. При этом количество выводов микросхемы не. превысит 48 для организации контроля запоминсцощаго устройства с длиной слова в один байт. Таким образом, предпоженное устройство позволяет обеспечить контроль, локализсщию неисправности и отключение отказавшего блока памяти ценой сравнительно небольших затрат оборудования (от единиц до долей процента от общего количества образования системы памяти в зависимости от информационной емкости устройства) при практически полном отсутствии потери быстродейст-« Формула изобретения Запоминающее устройство с самоконтролем, содержащее блоки памяти, выходы которых подключены к первым входам соответствующих блоков контроля, блок формирования сигнала отказа, выходные и управляющую шины, тличающееся тем, что, с целью повышения быстродействия стройства, оно содержит блок задержки строба считывания и блоки поразядного сравнения, входы которых подключены соответственно к выходам блоков памяти, блоков контроля и блока задержки строба считывания, а выоды - к выходным шинам и одним из входов блока формирования сигнала отказа, другие входы которого соединены с выходами блоков контроля, выхоы блока формирования сигнала отказа подключены соответственно ко вторым входам блоков контроля и одному из вxJDдoв блока задержки строба счнтывания, другой вход которого соединен с управляющей шиной. Источники информации, принятые во внимание при экспертизе I. Путинцев Н.Д. Аппаратный контроль управляющих цифровых вычислительных машин.М., Советское радио , 1966, с. 95. 2. Белецкий В.В. Теория и практические методы резервирования радиоэлектронной аппаратуры.М., Энергия, 1977, с.,147 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1980 |

|

SU879655A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1001174A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1086461A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1368923A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1164790A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1251188A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU951406A1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1417041A1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1089627A1 |

Авторы

Даты

1979-11-05—Публикация

1977-08-16—Подача