112

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам.

Цель изобретения - упрощение устройства.

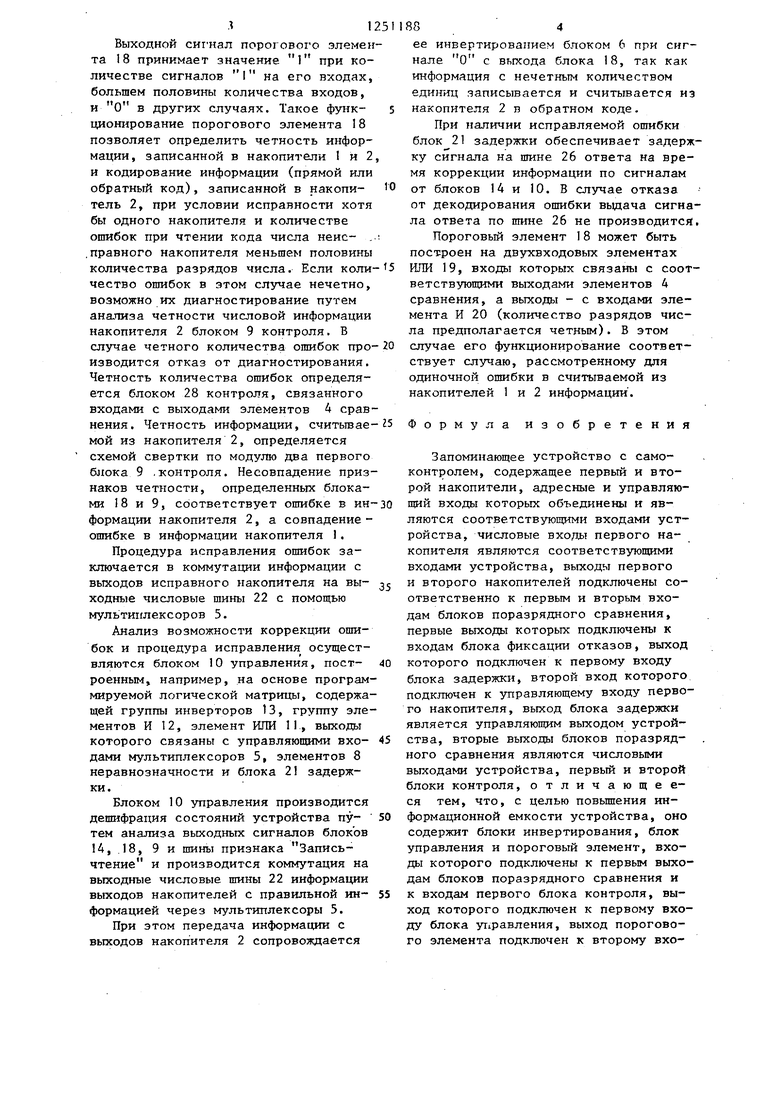

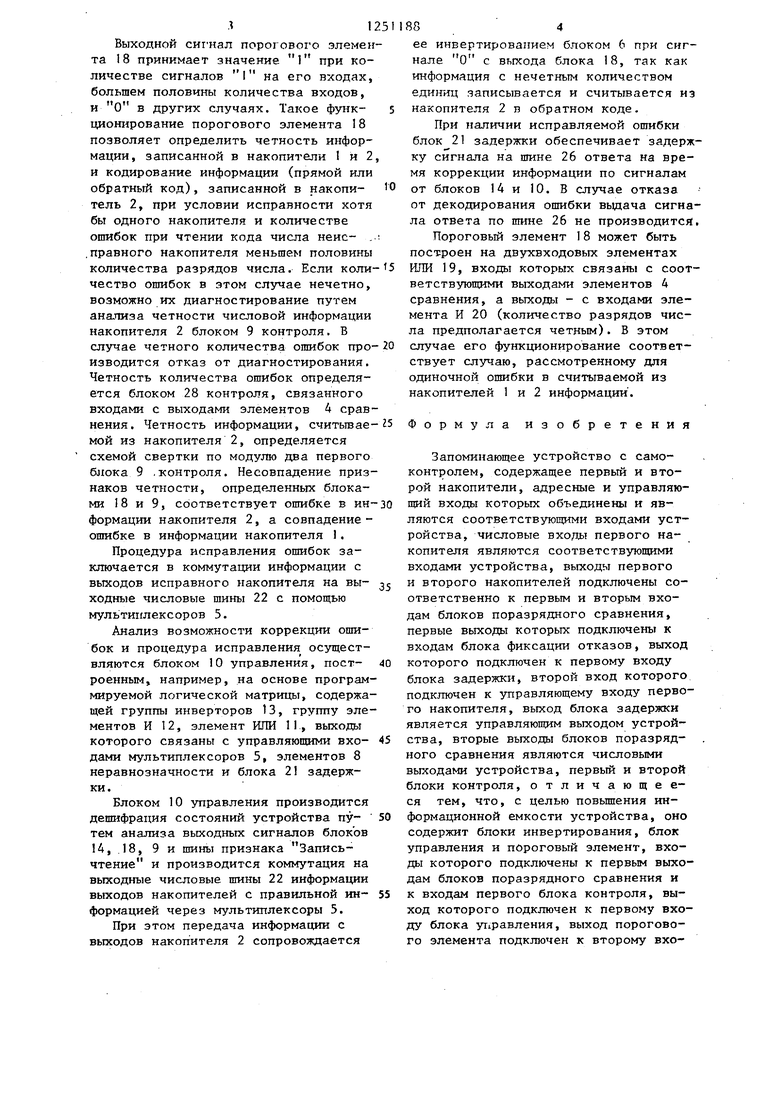

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит накопители 1 и 2, блоки 3 поразрядного сравнения, каждый из которых состоит из элемента 4 сравнения и мультиплексора 5, блоки 6 инвертирования, каждый из которых вьтолнен в виде элемента ИЛИ 7 и элемента 8 неравнозначности, первый блок 9 контроля (схема свертки по модулю два), блок 10 управления, содержащий группу элементов ИЛИ 1I, группу элементов И 12 и группу элементов НЕ 13, блок 14 фиксации отказов, содержащий первый и второй элементы ИЛИ-НЕ 15 и 16 и элемент И 17, пороговый элемент 18, содержащий группу элементов ИЛИ 19 и элемент И 20, блок 21 задержки, числовые выходы 22, числовые входы 23, управляющий вход 24 записи-чтения, адресные входы 25, управляющий выход 26 ответа, управляющий вход 27 обращения, второй блок 28 контроля (схема сверки по модулю два).

Устройство работает следующим образом.

На адресные, числовые, признака операции и обращения входы 23, 24, 25, 27 соответственно внешними устройствами задаются коды адреса, числа, сигнал обращения и признака Запись-чтение.

Предполагается, что при операции Запись состояние числовых выходов

22соответствует сигналам О, а при операции Чтение сигналы О установлены на числовых входных пшнах

23- количество числовых выходов каждому из накопителей 1 и 2 больше двух.

В режиме Запись s накопитель 1, числовые входы которого связаны непосредственно с числовыми входами 23 записьгаается прямой код поступающей на входы 23 информации. Код числа, записываемый в накопитель 2, числовые входы которого связаны с пганой 25 через блок 6 инвертирования, зависит от значения суммы по модулю два (четности) информации числовых шин 23. При четности количества единиц в коде числа шины 23 на числовые входы

8I

накопителя 2 от блока 6 подается пря-- мой код числа, при нечетности - обратный код.

Сумма по модулю два (признак четности) вьфабатывабтся блоком 9 контроля (схемой свертки по модулю два), выходной сигнал которого используется блоком 10 управления для образования сигнала инвертирования на управляющих входах элементов 8 неравнозначности, на информах ионные входы которых поступает код записываемого числа с шин 23 через элементы ИЛИ 7. В режиме Чтение коды чисел,

считьшаемых из накопителей 1 и 2, сравниваются поразрядно элементами 4 сравнения блоков 3, а результаты сравнения анализируются блоком 14 фиксации отказов, пороговым элементом 18 и вторым блоком 28 контроля, связанных входами с выходами элементов 4 сравнения,

При правильном считывании информации из накопителей 1 и 2 все элементы 4 одновр-еменно формируют сигналы 1 или О, что обеспечивает образование сигнала 1 на выходе элемента ИЛИ-НЕ 15 либо элемента И 17 и, следовательно, сигнала О на выходе

элемента ИЛИ-НЕ 16 блока 14 фиксации отказа, являющегося признаком правильного считьшания информации.

В этом случае блок 10 управления обеспечивает формирование сигнала на

управляющих входах мультиплексоров 5 блоков 3, пропускающих на выходные числовые шины 22 устройства информацию с выходов накопителя 1, а блок 21 - формирование сигнала ответа устройства на шине 26 ответа, соответствующего достоверной информации на выходных числовых шинах 22.

При неисправностях устройства, приводящих к ошибкам в считьгеаемой из накопителей 1 и 2 информации, на выходах элементов 4 сравнения образуются одновременно сигналы О и I, а на выходе блока 14 (выходе элемента ИЛИ-НЕ 16) - сигнал 1,

соответствующий неисправности устройства.

Выходные сигналы элементов 4 срав- нения анализируются пороговым элементом 18 и схемами сверки по модулю два второго блока 28 контроля следующим образом.

1

Выходной сиг иал порогового элемента 18 принимает значение 1 при количестве сигналов 1 на его входах, большем половины количества входов, и О в других случаях. Такое функ- ционирование порогового элемента I8 позволяет определить четность информации, записанной в накопители 1 и 2 и кодирование информации (прямой или обратный код), записанной в накопи- тель 2, при условии исправности хотя бы одного накопителя и количестве ошибок при чтении кода числа неис- . .правного накопителя меньшем половины количества разрядов числа. Если коли чество ошибок в этом случае нечетно, возможно их диагностирование путем анализа четности числовой информации накопителя 2 блоком 9 контроля. В случае четного количества ошибок проИзводится отказ от диагностирования. Четность количества ошибок определяется блоком 28 контроля, связанного входами с выходами элементов 4 сравнения. Четность информации, считьшаемой из накопителя 2, определяется схемой свертки по модулю два первого блока 9 .контроля. Несовпадение признаков четности, определенных блоками 18 и 9, соответствует ошибке в информации накопителя 2, а совпадение - ошибке в информации накопителя 1.

Процедура исправления ошибок заключается в коммутации информации с выходов исправного накопителя на вы- ходные числовые шины 22 с помощью мультиплексоров 5.

Анализ возможности коррекции ошибок и процедура исправления осуществляются блоком 10 управления, пост- роенным, например, на основе программируемой логической матрицы, содержащей группы инверторов 13, группу элементов И 12, элемент ИЛИ 11, выходы которого связаны с управляющими вхо- дами мультиплексоров 5, элементов 8 неравнозначности и блока 21 задержки.

Блоком 10 управления производится дешифрация состояний устройства пу- тем анализа выходных сигналов блоков 14, .18, 9 и шины признака Запись- чтение и производится коммутация на выходные числовые шины 22 информации выходов накопителей с правильной ин- формацией через мультиплексоры 5.

При этом передача информации с выходов накопителя 2 сопровождается

84

ее инвертированием блоком 6 при сигнале О с вьгхода блока 18, так как информация с нечетным количеством единиц записывается и считывается из накопителя 2 в обратном коде.

При наличии исправляемой ошибки блок 21 задержки обеспечивает задержку сигнала на шине 26 ответа на время коррекции информации по сигналам от блоков 14 и 10. В случае отказа от декодирования ошибки вьщача сигнала ответа по шине 26 не производится.

Пороговый элемент I8 может быть построен на двухвходовых элементах ИЛИ 19, входы которых связаны с соот- ветствуюшз€ми выходами элементов 4 сравнения, а выходы - с входами элемента И 20 (количество разрядов числа предполагается четным). В этом случае его функционирование соответствует случаю, рассмотренному для одиночной ошибки в считываемой из накопителей 1 и 2 информации .

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее первый и второй накопители, адресные и управляющий входы которых объединены и являются соответствующими входами устройства, числовые входы первого накопителя являются соответствующими входами устройства, выходы первого и второго накопителей подключены соответственно к первым и вторым входам блоков поразрядного сравнения, первые выходы которых подключены к входам блока фиксации отказов, выход которого подключен к первому входу блока задержки, второй вход которого подключен к управляющему входу первого накопителя, выход блока задержки является управляющим выходом устройства, вторые выходы блоков поразрядного сравнения являются числовыми выходами устройства, первый и второй блоки контроля, отличающее- ся тем, что, с целью повьш1ения информационной емкости устройства, оно содержит блоки инвертирования, блок управления и пороговый элемент, входы которого подключены к первым выходам блоков поразрядного сравнения и к входам первого блока контроля, выход которого подключен к первому входу блока утфавления, выход порогового элемента подключен к второму входу блока управления, третий вход которого подключен к выходу блока фиксации отказов, четвертый вход блока контроля подключен к выходу второго блока контроля, входы которого подключены к первым выходам блоков инвертирования, вторые выходы блоков инвертирования подключены к числовым входам второго накопителя и к третьим входам блоков поразрядного сравнения, первые входы блоков инверти

рования подключены к числовым входам первого накопителя, вторые входы блоков инвертирования подключены к выходам второго накопителя, третьи входы.блоков инвертирования подключены к первому выходу блока управления, второй выход которого подключен к четвертым входам блоков поразрядного сравнения, третий выход блока управ - ления подключен к третьему вхбду блока задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1368923A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1501171A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1185400A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1100638A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1164790A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1094071A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении высоконадежных запоминающих устройств. Целью изобретения является упрощение известного запоминающего устройства с самоконтролем. Устройство содержит накопители , блоки поразрядного сравнения, блоки инвертирования, блок управления, блок фиксации.отказов, элемент И, пороговый элемент. Каждь1Й блок поразрядн ого сравнения содер кит элемент сравнения, мультиплексор. Каждый блок инвертирования содержит элемент ИЛИ, элемент иеравноэначнос- тн, блок контроля. Блок управления содержит группу элементов ИЛИ, группу элементов И, группу элементов НЕ, Пороговый элемент содержит группу элементов ИЛИ, элемент И, блок задержки. 1 ил. (О ел С

Редактор А.Огар

Составитепь С.Шустенко

Техред И.Гайдош Корректор М.Демчик

Заказ 4419/51 Тираж 543 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Путинцев Н.Д | |||

| Аппаратный контроль управляющих цифровых вычислительных машин | |||

| М.; Сов | |||

| радио, 1966, с | |||

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU696545A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-08—Подача