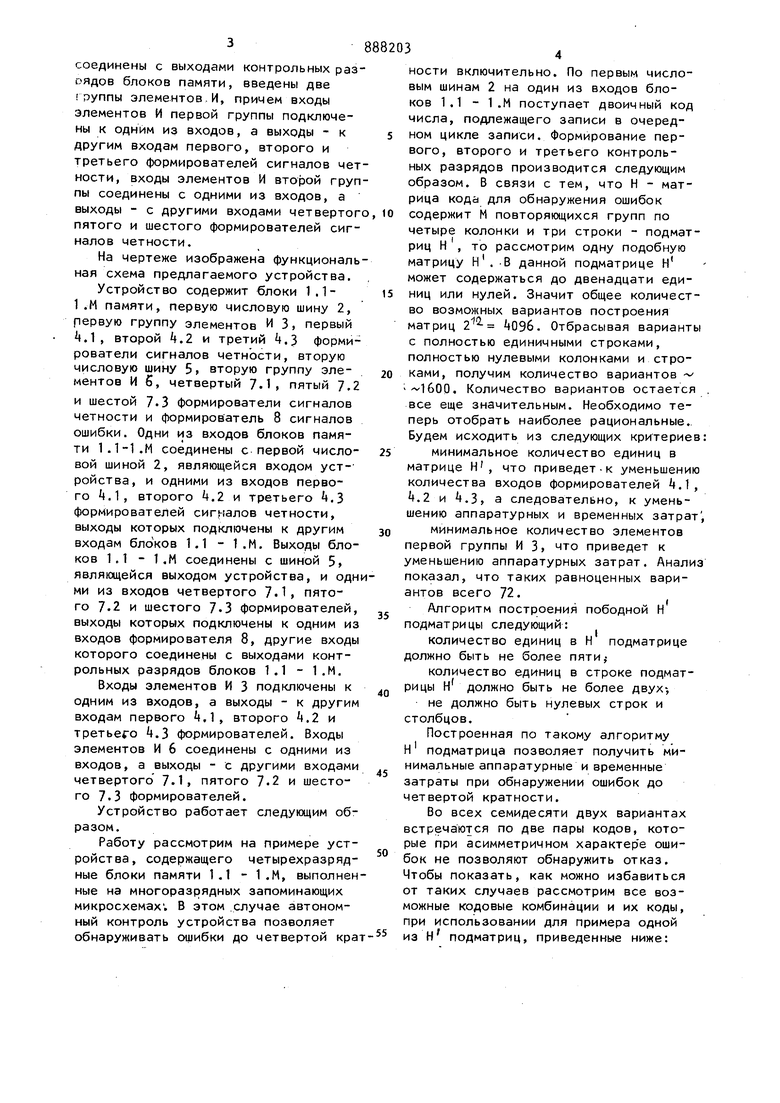

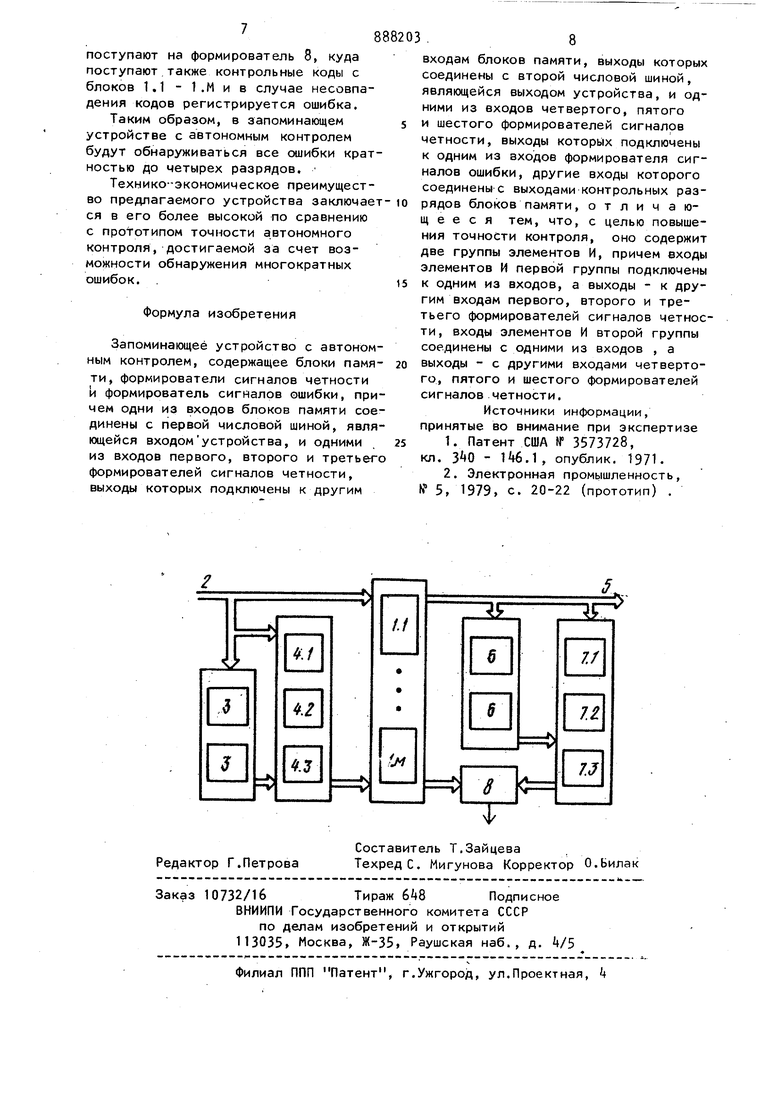

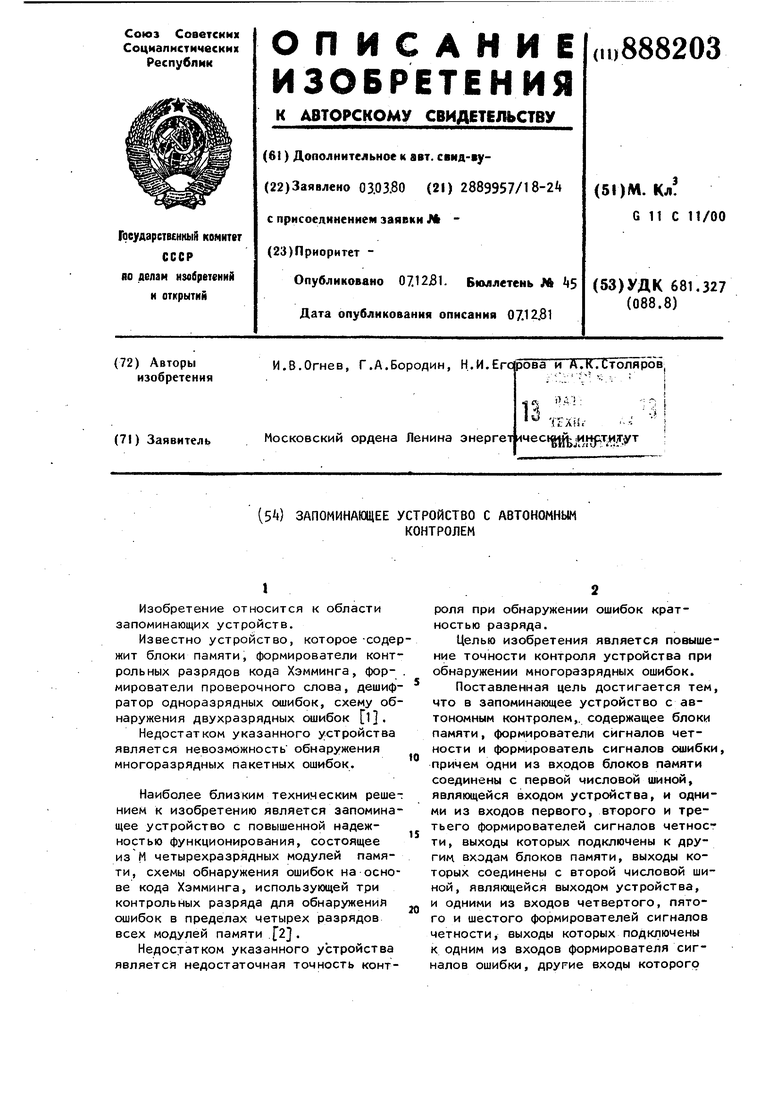

Изобретение относится к области запоминающих устройств. Известно устройство, которое-содер жит блоки памяти, формирователи контрольных разрядов кода Хэмминга, формирователи проверочного слова, дешифратор одноразрядных ошибок, схему обнаружения двухразрядных ошибок l. Недостатком указанного устройства является невозможность обнаружения многоразрядных пакетных ошибок. Наиболее близким технинеским решег нием к изобретению является запоминащее устройство с повышенной надежностью функционирования, состоящее из М четырехразрядных модулей памяти, схемы обнаружения ошибок на основе кода Хэмминга, использующей три контрольных разряда для обнаружения ошибок в пределах четырех разрядов всех модулей памяти .2. Недостатком указанного устройства являетcifl недостаточная точность коитроля при обнаружении ошибок кратностью разряда. Целью изобретения является повышение точности контроля устройства при обнаружении многоразрядных ошибок. Поставленная цель достигается тем, что в запоминающее устройство с автономным контролем,, содержащее блоки памяти, формирователи сигналов четности и формирователь сигналов ошибки, причем одни из входов блоков памяти соединены с первой числовой шиной, являющейся входом устройства, и одними из входов первого, второго и третьего формирователей сигналов четности , выходы которых подключены к другин входам блоков памяти, выходы которых соединены с второй числовой шиной, являющейся выходом устройства, и одними из входов четвертого, пятого и шестого формирователей сигналов четности, выходы которых подключены к одним из входов формирователя сигналов ошибки, другие входы которого соединены с выходами контрольных разоядов блоков памяти, введены две группы элементов,И, причем входы элементов И первой группы подключены к одним из входов, а выходы - к другим входам первого, второго и третьего формирователей сигналов чет ности, входы элементов И второй груп пы соединены с одними из входов, а выходы - с другими входами четвертог пятого и шестого формирователей си|- налов четности. На чертеже изображена функциональ ная схема предлагаемого устройства. Устройство содержит блоки 1.11.М памяти, первую числовую шину 2, первую группу элементов И 3, первый .1, второй k.2 и третий 4.3 формирователи сигналов четности, вторую числовую шину 5 вторую группу элементов И 6, четвертый 7.1, пятый 7.2 и шестой 7.3 формирователи сигналов четности и формирователь 8 сигналов ошибки. Одни из входов блоков памяти 1.1-1.М соединены с первой числовой шиной 2, являющейся входом устройства, и одними из входов первого 4.1, второго 4.2 и третьего 4.3 формирователей сигналов четности, выходы которых подключены к другим входам блочков 1.1 - 1 .М. Выходы блоков 1,1 - 1.М соединены с шиной 5 являющейся выходом устройства, и одн ми из входов четвертого 7.1, пятого 7.2 и шестого 7.3 формирователей, выходы которых подключены к одним из входов формирователя 8, другие входы которого соединены с выходами контрольных разрядов блоков 1.1 - 1.М. Входы элементов И 3 подключены к одним из входов, а выходы - к другим входам первого 4,1, второго 4.2 и третьего 4.3 формирователей. Входы элементов И 6 соединены с одними из ВХОДОВ, а выходы - с другими входами четвертого 7.1, пятого 7.2 и шестого 7.3 формирователей. Устройство работает следующим образом. Работу рассмотрим на примере устройства, содержащего четырехразрядные блоки памяти 1.1 - 1 .М, выполнен ные на многоразрядных запоминающих микросхемах; В этом случае автономный контроль устройства позволяет обнаруживать ошибки до четвертой кра ности включительно. По первым числовым шинам 2 на один из входов блоков 1.1 - 1.М поступает двоичный код числа, подлежащего записи в очередном цикле записи. Формирование первого, второго и третьего контрольных разрядов производится следующим образом. В связи с тем, что Н - матрица кода для обнаружения ошибок содержит М повторяющихся групп по четыре колонки и три строки - подматриц Н , то рассмотрим одну подобную матрицу Н, -В данной подматрице Н может содержаться до двенадцати единиц или нулей. Значит общее количество возможных вариантов построения матриц 409б. Отбрасывая варианты с полностью единичными строками, полностью нулевыми колонками и строками, получим количество вариантов . Количество вариантов остается . все еще значительным. Необходимо теперь отобрать наиболее рациональные.. Будем исходить из следующих критериев: минимальное количество единиц в матрице Н, что приведет-к уменьшению количества входов формирователей 4.1, 4.2 и 4.3, а следовательно, к уменьшению аппаратурных и временных затрат , минимальное количество элементов первой группы И 3, что приведет к уменьшению аппаратурных затрат. Анализ показал, что таких равноценных вариантов всего 72. Алгоритм построения пободной Н подматрицы следующий: количество единиц в Н подматрице должно быть не более пяти,количество единиц в строке подматрицы Н должно быть не более двух-, не должно быть нулевых строк и столбцов. Построенная по такому алгоритму и подматрица позволяет получить минимальные аппаратурные и временные затраты при обнаружении ошибок до четвертой кратности. Во всех семидесяти двух вариантах встречаются по две пары кодов, которые при асимметричном характере ошибок не позволяют обнаружить отказ. Чтобы показать, как можно избавиться от таких случаев рассмотрим все возможные кодовые комбинации и их коды, при использовании для примера одной из Н подматриц, приведенные ниже:

H № 20 - 1000

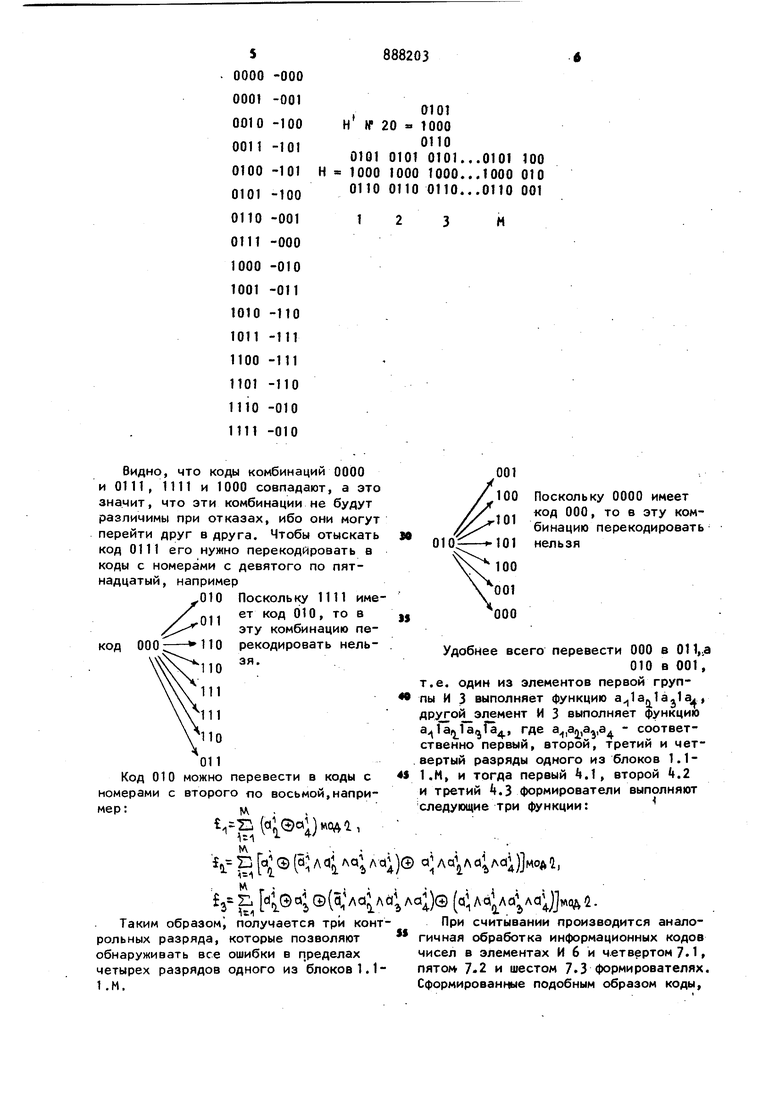

1000 1000 1000...1000 010 Видно, что коды комбинаций OOOO и 0111, 1111 и 1000 совпадают, а это значит, что эти комбинации не будут различимы при отказах, ибо они могут перейти друг в друга. Чтобы отыскать код 0111 его нужно перекодировать в коды с номерами с девятого по пятнадцатый, например ,010 Поскольку 1111 имеет код 010, то в эту комбинацию пекод 000-- 110 рекодировать нельзя. Код 010 можно перевести в коды с номерами с второго по восьмой,например:| Л . . VZl()MOAa, ,;Ac ki К®а;©( Таким образом получается три конт рольных разряда, которые позволяют обнаруживать все ошибки в п,ределах четырех разрядов одного из блоков 1.11.М.

.0101

0110

0101 0101 0101...0101 100

Ono 0110 0110...0110 001

H Поскольку 0000 имеет код 000, то в эту комбинацию перекодировать нельзя Удобнее всего перевести 000 в ОП,.а 010 в 001, т.е. один из элементов первой группы И 3 выполняет функцию ,. , другой элемент И 3 выполняет функцию ,jfa. где а,а,,а,а - соответственно первый, второй, третий и четвертый разряды одного из блоков 1.11.И, и тогда первый 4.1, второй k.2 и третий 4.3 формирователи выпрлняют следующие три функции: )моА1, . ;)® (,,1. При считывании производится аналогичная обработка информационных кодов чисел в элементах И 6 и четвертом 7.1, пятом 7-2 и шестом 7.3 формирователях. Сформированное подобным образом коды, поступают на формирователь 8, куда поступают,также контрольные коды с блоков 1.1 - 1.М и в случае несовпадения кодов регистрируется ошибка. Таким образом, в запоминающем устройстве с автономным контролем будут обнаруживаться все ошибки крат ностью до четырех разрядов. Технико-экономическое преимущество предлагаемого устройства заключае ся в его более высокой по сравнению с прототипом точности автономного контроля, достигаемой за счет возможности обнаружения многократных ошибок. , Формула изобретения Запоминающее устройство с автоно ным контролем, содержащее блоки пам ти, формирователи сигналов четности и формирователь сигналов ошибки, пр чем одни из входов блоков памяти со динены с первой числовой шиной, явл ющейся входомустройства, и одними из входов первого, второго и третье формирователей сигналов четности, выходы которых подключены к другим входам блоков памяти, выходы которых соединены с второй числовой шиной, являющейся выходом устройства, и одними из входов четвертого, пятого и шестого формирователей сигналов четности, выходы которых подключены к одним из входов формирователя сигналов ошибки, другие входы которого соединены с выходами контрольных разрядов блоков памяти, отличающееся тем, что, с целью повышения точности контроля, оно содержит две группы элементов И, причем входы элементов И первой группы подключены к одним из входов, а выходы - к другим входам первого, второго и третьего формирователей сигналов четности, входы элементов И второй группы соединены с одними из входов , а выходы - с другими входами четвертого, пятого и шестого формирователей сигналов четности. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3573728, кл. - 146.1, опублик. 1971. 2.Электронная промышленность, N 5, 1979, с. 20-22 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU832604A1 |

| Модульное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1320848A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149315A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149314A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство | 1983 |

|

SU1149316A1 |

| Запоминающее устройство с обнаружением наиболее вероятных ошибок | 1983 |

|

SU1149313A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1274004A1 |

| Устройство для сдвига информации | 1983 |

|

SU1188783A2 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

Авторы

Даты

1981-12-07—Публикация

1980-03-03—Подача