ходом второго тригЬера блокировки, i-ые выходы первого и второго дешифраторов (., где N - максимальная значность входного и выходного кодов) соединены с входами с первого по i-й элементов ИЛИ.соответственно первой , и второй групп,первые входы N-x элементов И первой и второй групп соеди иены соответственно с последними выходами первого и второго дешифраторов, ,отличающийся тем, что, с целью повышений быстродействия, в него введены пятый и шестой элементы И, пятый элемент ИЛИ и треть группа элементов ИЛИ, первый входы которых соединены с выходами соответствующих элементов И первой группы, второй вход (i+l)-ro элемента ИЛИ третьей группы соединен с i-M . выходом первого дешифратора, N-й выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с входом разрешени записи преобразователя, а выход пятого элемента И соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом N-ro разряда сдвигающего регистра, а выход пятого элемента ИЛИ соединен с вторым входом третьего элемента И и единичным входом триггера подготовки,первый вход шестого элемента И соединен с выходом второго элемента И и счетным входом первого счетчика, разрядные входы которого соединены с выходами регистра значности выходного кода, второй вход шестого элемента И соединен с выходом первой схемы сравнения, а выход шестогр элемента И соединен с третьим, входом первого элемента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь @ -значного двоичного кода в @ -значный | 1983 |

|

SU1156057A1 |

| Преобразователь @ -значного двоичного кода в @ -значный | 1985 |

|

SU1256210A1 |

| Устройство для преобразования кодов в системе передачи данных | 1982 |

|

SU1086449A1 |

| Преобразователь кода Грея в параллельный двоичный код | 1982 |

|

SU1070541A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Устройство для сравнения кодов | 1985 |

|

SU1548782A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ /г-3,НАЧНОГО ДВОИЧНОГО КОДА В р-ЗНАЧНЫЙ ДВОИЧНЫЙ КОД | 1968 |

|

SU220630A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Устройство для преобразования кодов с одного языка на другой | 1981 |

|

SU985793A1 |

ПРЕОБРАЗОВАТЕЛЬ П-ЗНАЧНОГО ДВОИЧНОГО КОДА В, Р-ЗНАЧНЫЙ КОД, СОдержасдай первый, и второй дешифраторы, первый и второй счетчики, первую и вторую схегФьсравнения, регистры значности входного и выходного кодов , выходы которых соединены соответственно с входами первого и второго дешифраторов и первыми группами входов первой и второй схем сравнения, вторые группы входов которых соединены соответственно с выходалш первого и второго счетчиков, первую и вторую группы элементов И, первую и вторую группы элементов ИЛИ, выходы которых соответственно соединены с первыми входами элементов И первой и второй групп, сдвигающий регистр, выходы которого соединены с вторыми входами соответствующих элементов И второй группы, выходы которых являются информационными выходами преобразователя, входы значности входного и выходного кодов которогр соединены«соответственно с входами регистров значности входного и выходного кодов,первый и второй.триггеры блокировки, четыре элемента И, триггер подготовки, четыре элемента ИЛИ и генератор импульсов, выход которО , го соединен с первым входом даервого элемента И, второй и третий входы которого соединены соответственно с единичными выходагии первого и второго триггеров блокировки, нулевые выходы которых являются соответственно вы ходами запроса и готовности преобразователя, вход установки нуля которого соединен с входами первого, второго и третьего элементов ИЛИ, нулевым входом триггера подго.тонки и входом сброса сдвигающего, рег гистра, вход сдвига которого соединен с выходом первого элемента И и , с первым входом второго элемента И, второй вход которого соединен с единичным выходом триггера пoдгoтoвки нулевой выход которого соединен с первым входом третьего элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, третий вход которого соединен с выхо дом второй схемы сравнения и с вто- рым входом второго элемента ИЛИ, выход которого соединен с входом сброса второго счетчика, а выход третьего элемента ИЛИ соединен с нулевым входом второго триггера блокировки, единичный вход которого соединен с выходом четвертого элемента ИЛИ, -первый вход которого соединен с выходом четвертого элемента И и с третьими входами элементов И второй группы, 00 выходы которых являются информацион ными выходами преобразователя, вход подготовки которого соединен с вхо- со дом установки сдвигающего регистра, 00 rsD вторыми .входаиии первого i четвертого элементов ИЛИ и входом сброса первого счетчика, счетный вход второго счетчика соединенс выходом второго элемента И, второй вход которого сое-динен с единичным выходом триггера подготовки, выход первого элемента ИЛИ соединен с нулевым входом первого триггера блокировки, единичный .вход которого / соединен с входом разрешения записи преобразователя, вход . разрешения считывания которого соединен с пёрвыг/ входом четвертого элемента И, второй вход которого соединен с нулевым вы

Изобретение относится к автоматике и вычисли-тельной технике и может быть использовано при построении стройств согласования приборов с различными разрядными сетками.

Известен преобразователь кодов, содержащий блок управления, регистр

информации, кодирующие блоки и суматоры- С1).

Недостатком известного преобразователя является большая сложность относительно низкая скорость пребразования.

Наиболее близким к предлагаемому по технической сущности и схемному

остроению является преобразователь п-значного двоичного кода в р-значный, содержащий регистры значности входного и выходного кодов, каждый , из которых соединен с входами соответствующего дешифратора и схемами сравнения, причем другие входы к ждой схел1Ы сравнения соединены с выг ходами соответствующего счетчика, выходы первого дешифратора через, первую группу элементов ИЛИ соединены

с входами соответствующих входных элементов И, выходы второго дешифратора через вторую группу элементов ИЛИ соединены с входами выходных элементов И, выход первого входного элемента И через первый элемент ИЛИ соединен с входом младшего разряда сдвигающего регистра, выходы остальных входных элементов И непосредственно соединены с входами соответствующих разрядов сдвигающего регистра , выхо/цд которого соединены с входами соответствующих выходных элементов И, выход первой схемы сравнения через первый элемент ИЛИ соединен с нулевыми входами первого счетчика и первого триггера блокировки, выход второй схемы сравнения через третий и четвертый элементы ИЛИ соединены с кулевыми входами второго счетчика и второго триггера блокировки соответственно, ну0 левой выход первого триггера блокировки является выходом запроса преобра:зователя, нулевой выход второго триггера блокировки соединен с вхо- , дом первого элемента И разрешения

с считывания, выход которого соединен с входами входных элементов И и пятого элемента ИЛИ, выход которого соединен с единичным входом второго триггера блокировки, выход генератора импульсов соединен с входом второго элемента И, с входами которого соединены единичные выходы триггеров блокировки, выход второго элемента И соединен с входом сдвига сдвигаю-щего регистра, со счетным входом первого счетчика и через третий элемент И - со счетным входом второго счетчика, выход старшего разряда сдвигающего регистра соединен с единичным входб триггера подготовки

0 и с входом четвертого элемента И, с вторым входом которого соединен нулевой выход триггер1а подготовки,выход четвертого-элемента И соединен с входом четвертого элемента ИЛИ единич5 вый выход триггера подготовки соединен с входом третьего элемента И С2 .

Недостаток известного преобразова теля состоит в значительном времени

преобразования, которое обусловлено наличием длительного этапа подготовки преобразователя к приему входного кода.

Целью изобретения является повышение быстродействия преобразователя.

Поставленная цель достигается тем, что в преобразователь п-знач- ногодвоичного кода в р-значный код, содержащ} й первый и второй дешифраторы, первый и второй счетчики, первую и вторую схемы сравнения, регистры значности входного и выходного кодов, выходы которых соединены соответственно с входами первого и второго дешифраторов и первыми группами входов первой и второй схем сравнения, вторые группы входов которых соединены соответственно с выходами первого и второго счетчиков, первую и вторую группы элементов И, первую и вторую группы элементов ИЛИ выходы которых соответственно соединены с первыми входами элементов И первой и второй групп, сдвигающий регистр, выходы которого соединены с вторыми входами соответствующих элементов И второй группы, вьаходы которых являются информационными выходами преобразователя, входы значности входного и выходного кодов которого соединены соответственно с входами регистров значности входного и выходного кодов, первый и второй триггеры блокировки, четыре эле,м,еата И, триггер подготовки, че- . тыре элемента ИЛИ и генератор импульсов, выход которого соединен с первыг/ входом первого элемента И, второй и третий входы которого соединены соответственно с единичны.ми выходами первого и второго триггеров блокировки, нулевые выходы которых являются соответственно выхода ми запроса и готовности преобразователя, вход, установки нуля которюго соединен с первыми входами первого второго и третьего элементов ИЛИ, нулевым входом триггера подготовки и входом сброса сдвигающего регистра, вход сдвига которого соединен с выходом первого элемента И и с первым входом второго элемента И, втоЕЮй вход которого соединен с единичным выходом триггера подготовки, нулевой выход которого соединен с первым входом третьего элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, третий вход которого соединен с выходом второй схемы сравнения и с вторым входом второго элемента ИЛИ,.выход которого соединен с входом сброса второго счетчика, а выход третьего элемента ИЛИ соединен с нулевым входом второго триггера блокировки, единичный вход которого соединен с выходом

.четвертого элемента ИЛИ, первый вход которого соединен с выходом четвертого элемента И и с третьими входами элементов И второй группы, выходы которых являются информационными выходами преобразователя, вход подготовки которого соединен с входом установки сдвигающего регистра, вторыми входами первого и четвертого элементов ИЛИ и входом сброса первого счетчика, счетный вход второго счетчика соединен с выходом второго элемента И, второй вход которого соединен с единичным выходом триггера подготовки, выход первого элемента ИЛИ соединен с нулевым входом первого триггера блокировки, единичный вход которого соединен с входом разрешения записи преобразователя., вход разрешения считывания которого соединен с первым входом четвертого элемента И, второй вход которого соединен с нулевым выходом второго триггера блокировки, i-ые выходы первого и в.торрго дешифраторов , где N - максимальная значность входного и выходного кодов) соединены с входами с первого noi-й элементов ИЛИ соответственно первой и второй групп, первые входы N-X элементов И первой и второй групп соединены соответственно с последними выходами первого и второго дешифраторов, дополнительно введены пятый и шестой элементы И, пятый элемент ИЛИ и третья группа элементов ИЛИ, первые входы которых соединены с выходами соответствующих, элементов И первой группы, второй вход (i+lT-ro элемента ИЛИ третьей группы соединен с-i-м входом первого дешифратора, N-й йыход которого соединен с первым входом пятого элемента И, второй вход которого соединен с входом разрешения записи преобразователя, а выход пятого элемента И соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом N-ro разряда сдвигающего регистра/ а выход пятого элемента ИЛИ соединен с вторым входом третьего элемента И и единичным входом триггера подготовки, первый вход шестого элемента И соединен с выходом второго элемента И и счетным входом первого счетчика разрядные входы которого соединены с выходами регистра значнрсти выходного кода, второй вход шестого элемента И соединен с выходом первой схемы сравнения, а выход шестого элемента И соединен с третьим входом первого элемента ИЛИ.

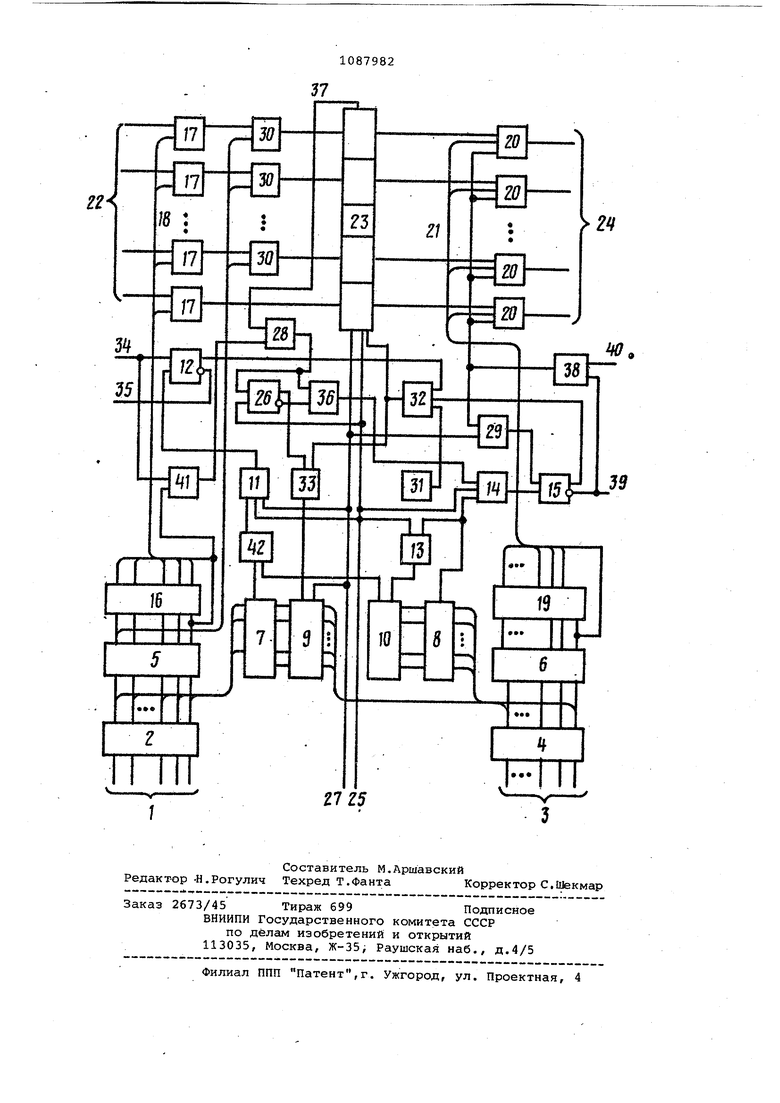

На чертеже приведена структурная схема предлагаемого преобразователя

Входы 1 значностивходного кода соединены с входами регистра 2 знач кости входного кода, а входы 3 значности выходного кода - с входами ре Рнстра 4 значности выходного кода. Выходы регистров 2 и 4 соединены с первым и вторы 5 дешифраторами 5 и б и первой и второй схемами 7 и 8 срав нения, к которым подсоединены также выходы первого и второго счетчиков 9 и 10, кроме того, выход. регистра 4 соединен с входами соответствую щих разрядов счетчика 9. Выход элемента ИЛИ 11 подсоединен к нулевому входу первого триггера 12 блокировки. Выход схемы 8 сравнения соединен с входом элемента ИЛИ 13 и через элемент ИЛИ 14 - с нулевым входом второго триггера 15 блокировки. Выходы дешифратора 5 соединены через элементы ИЛИ 16 первой группы с элементами И 17 первой группы по следую щему правилу: вход 18 i-ro элемента И 17 первой группы соединен через iэлемент ИЛИ 16 первой группы со всеми выходами дешифратора 5, кроме первых (1-1) выходов. Вход 18 послед него элемента И 17 первой группы (верхнего по чертежу) соединен непос ,редственно с последним выходом дешифратора 5.. , выходы дешифратора 6 соединены через элементы ИЛИ 19 второй группы с входами элементов И- 20 второй груп пы по следующему правилу: вход 21 i-ro элемента И 20 второй группы сое динен, через i-й элемент ИЛИ 19 второй группы со всеми выходами дешифратора 6, кроме первых (i-1) выходрв, а вход 21 последнего элемента И 20{нижней по чертежу) второй пы - непосредственно с последним выходом дешифратора 6. Информационные входы 22 преобразователя соединены с элементами И 17. Выходы сдвигающего регистра 23 через элементы И 20 .второй группы соединены с информационными выходами 24 преобразователя. Вход 25 установки нуля преобразователя соединен с нулевым входом триггера 26 подготовки и через элементы ИЛИ 11, 14 и 13 с нулевым входом триггеров 12 и 15 блокировки и счетчика 10. ВКрд 27 подготовки соединенчерез элемент ИЛИ 11 с нуле вым входом триггера 12 блокировки. Выходы элементов ИЛИ 28-29 соединены с единичными входами триггера 26 под готовки и второго триггера 15 блокировки. Выходы . дешифратора 5 сое;динен с входами элементов ИЛИ 30 третьей группы со сдвигом на один разряд (i-й выход дешифратора соединен с вх дом того элемента ИЛИ, выход которог соединен с входом (i-(-i)-ro разряда сдвигающего регистра), Единичные выходы триггеров 15 и 12 блокировки и выход генератора .31 импульсод соединены с входами элемен та И 32, выход.которого соединен с входом сдвига сдвигающего регистра 23 и через элемент И 33 - с счетным входом счетчиков 9 и 10. Вход 34 разрешения записи соединен с единичным входом триггера 12 блокировки, нулевой выход которого соединен с входом 35 запроса (т.е. с датчиком входного кода). Через элемент ИЛИ 28 с единичным входом триггера 26 подготовки и входом элемента И 36 соединен выход 37 старшего разряда сдвигающего регистра 23. Входы элемента И 38 соединены с нyлeвы выходом триггера 15 блокировки, являющегося выходом 39 готовности преобразователя и с входом 40 разрешения считывания выходного кода (т.е. с приемником выходно го кода-). Выход последнего разряда дешифратора 5 соединен через элемент И 41 и элемент ИЛИ 28 с.единичным входом триггера 26 подготовки, Выход первой схемы 7 сравнения через элемент И 42 (другой вход которого подключен к выходу элемента И 33) и элемент ИЛИ 11 соединен с нулевьтм входом триггера 12 блокировки. Преобразователь работает следующим образом. Перед началом работы преобразовйтель обнуляется. Для этого по входу 25 подается одиночный импульс, обнуляющий сдвигающий регистр 23, триггер 26 подготовки, триггеры 12 и 15 блокировки и счетчик 10. Затем по . входам 1 на регистр 2 записывается значность п-входного кода. Одновременно по входам 3 в регистр 4 записывается значность р-выходного ко- да. , Число разрядов с регистров 2 и 4 определяется выражением , где N - максимально-возможная значность входного и выходного кодов .Регистры 2 и 4через дешифраторы .5 и 6 и элементы ИЛИ 16 и 19 первой и второй групп выдают .раэрешение элементам И 17 и20 первой И второй групп на прием и выдачу соответственно входных и выходных кодов. Затем на вход 27 подается сигнал подготовки устройства к работе, по которому записывается единица в (n+l) разряд сдвигающего регистра 23 при п-значности входного кода и в счетчик 9 - значность р-выходного кода, триггер 15 блокировки устанавливается в единичное состояние, а триггер 12 - в нулевое. С нулевого выхода триггера 12 блокировки на выход 35 посылается сигнал готовности преобразователя к приему входного кода, а на выходе 39 отсутствует сигнал готовности преобразователя выдать выходной код, так как триггер 15 находится в единичном состоянии. Входной код,по входам 22 через элементы И 17 первой группы и ИЛИ 3 третьей группы поступает в п младши разрядов сдвигающего регистра 23. Одновременно с этим по входу 34 поступает сигнал сопровождения вход ного кода, который устанавливает триггер 12 блокировки в единичное с стояние, элемент И 32 деблокируется тактовые импульсы начинают поступат на вход сдвига сдвигающего регистра 23 и сдвигать входной код разрядностью п и единицу, находящуюся в (п+1) разряде. Процесс подготовки продолжается до тех пор, пока едашица подготовки движется по сдвигающему регистру 23. При выходе с последнего разр да единица подготовки через выход 3 и элемент ИЛИ 28 поступает на единичный вход триггера 26 подготовки, и через открытый элемент И 36 и элемент ИЛИ 14 - на нулевой вход триггера 15. При этом с единичного выхода триггера 15 подается запрещающий сигнал на элемент И 32, прерывающий подачу тактовых импульсов, а с нулевого - по выходу 39 приемника информации сигнал готовности преобразователя к выдаче выходного кода. При этом выдается разрешение элементу И 38 на передачу, поступающему по входу 40 сигналу считывания выходного кода. Кроме этого после перекода триггера 26 подготовки в единичное состояние выдается разрешение элементу И 33 на пропускание тактовых импульсов на счетный вход счетчиков 9 и 10, На этом этап подготовки закан чивается. В случае, если эначность входног .кода л равна разрядности сдвигающего регистра 23, то сигнал разрешени записи с входа 34 через элемент И 4 открытый сигналом с п-го выхода дешифратора 5, и через элемент ИЛИ 28 поступает на единичный вход триггера 26 подготовки и через открытый элемент И 36 и элемент ИЛИ 14 - на нулевой вход триггера 15 блокировки И .с его нулевого выхода посылается сигнал о готовности выдачи, кода. В дальнейшем при поступлении по входу 40 сигнала считывания выходно го кода открываются элементы И 20 второй группы и считывается выходной код. Одновременно с этим триггер 15-устанавливается в единичное состояние и выдает разрешение элементу И 32 на пропускание тактовых импульсов на счетный вход счетчикор 9 и 10, вход сдвига сдвигающего регистра 23. Как только в счетчике 10 записано число р за 2/ тактов или в счетчике 9 число п за ( 2) тактов, то сигнал со схемы 8 сравнения через элементы ИЛИ 13 и 14 обнуляет счетчик 10 и триггер 15 блокировки, с нулевого выхода .которого выдается сигнал готовнЬсти выдать код, или тактовый импуЛьс через открытый элемент И 42 и элемент ИЛИ 11 обнуляет триггер 12 блокировки, с нулевого выхода которого выдаётся запрос на прием очередного входного кода. В предлагаемом преобразователе по сравнению с известным время преобразования уменьшается на величину 1( 2 Р) (в случае кратностивходного и выходного кодов)i где f- тактовая частота генератора; г - значность входного кода; р -значность выходного кода, так как единица подготовки в предлагаемом преобразователе записывается в п+1 разряд сдви гающего регистра по получении сигнала подготовки к работе, а не перемещается, как в известном преобразователе, из младшего разряда сдвигающего регистра в ri-f 1 за С-2 тактов. Кроме того, предлагаемый преобразователь готов к приему очередного входного кода после считывания последних разрядов р-значного кода, потому что первый счетчик производит подсчет тактов в р-значно,сти выходного кода, которая записывается в счетчик по сигналу подготовки к .работе, а в известном преобразователе первый счетчик производит подсчет тактов с О, поэтому после считывания последних разрядов р-значного кода для выработки сигнала готовности на прием очередного кода счетчик досчитывает Т 2 Р тактов.

Авторы

Даты

1984-04-23—Публикация

1983-01-14—Подача