элемента ИЛИ соединен с входом подготовки преобразователя, с входом установки сдвигового регистра, с вторым входом -первого элемента ИЛИ и входом установки первого счетчика, счетный вход первого и второго счетчиков и первый вход пятого элемента И соединены с выходом второго элемента И, выход пятого элемента ИЛИ соединен с диничнь1м входом второго триггера блокировки, нулевой выход которого соединен с первым входом второго элемента И, второй лход которого соединен с единичным зходом триггера подготовки, нулевой выход которого соединен с первым входом четвертого элемента И, второй вход которого является входом разрешения считывания преобразователя .; информационные входы которого соединены с первыми входами элементов И первой группы, вторые входы которых соединены с выходами элементов ИЛИ первой группы, выходы злементов ИЛИ второй группы соединены соответственно с третьими входами элементов И второй группы, i-й выход первого дешифратора

П- 1 ... N , где N - максимальная зкачность входного и- выходного кодов )э соединен с первым входом (i:-i)-ro элемента ИЛИ третьей групп г-е выходы первого и второго дешиф; аторов соединены с входами с первого по i-й элементов ИЛИ соответственно первой и второй групп, вторые входы N -к элементов И первой и второй групп соединены соответственно с последними выходами первого и второго дешифраторов, нулевой вход паввого триггера блокировки соеди

ьен с выходом первого элемента ИЛИ третий вход которого соединен с зыходом тятого элемента И, второй вход которого соодинен с выходом первой сравнения, единичный вход первого триггера блокировки соединен с входом разрешения запи56057

cif преобразователя и с первым входом шестого элемента И, второй вход которого -соединен с N -м выходом первого дешифратора, а выход с первым выходом четвертого элемента И.ПИ, второй вход которого соединен с выходом М -го разряда сдвигового регистра, которого соединены с соответствующими выходами элементов ИЛИ третьей группы, первые входы которых соединены с соответствующими выходами элементов И первой группы, отличающийс я тем, что, с целью расширения функциональных возможностей за счет обеспечения преобразования последовательных кодов, в него введены седьмой и восьмой элементы И N -и элемент ИЛИ, третья группа элементов ИЛИ, шестой элемент И.ПИ и триггер режима работы, нулевой выход которого соединен с третьим входом шестого элемента И, с третьими входами элементов И первой группы и управляющим входом первого дешифратора, единичный выход триггера режима соединен с первыми входами седьмого и восьмого элементов И, вторые входы которых язляютс-г соответственно последовательным информационным входом и входом синхронизации последовательного кода преобразователя, выход первого элемента И соединен с первым входом шестого элемента ИЛИ, второй вход которого соединен с выходом восьмого элемента И, выход шестого элемента ИЛИ соединен с входом сдвига сдвигового регистра, вход младшего разряда которого соединен с выходом N -го элемента ИЛИ третьей группы, первый вход которого соединен с единичным выходом триггера режима, а второй - с выходом N -го элемента И первой группы, выход седьмого элемента И соединен с входом последовательного кода сдвигового регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь @ -значного двоичного кода в @ -значный код | 1983 |

|

SU1087982A1 |

| Преобразователь @ -значного двоичного кода в @ -значный | 1985 |

|

SU1256210A1 |

| Устройство для преобразования кодов в системе передачи данных | 1982 |

|

SU1086449A1 |

| Устройство для сравнения кодов | 1985 |

|

SU1548782A1 |

| Устройство для декодирования двоичных кодов Хемминга | 1980 |

|

SU940299A1 |

| Устройство для преобразования кодов с одного языка на другой | 1981 |

|

SU985793A1 |

| Многоканальное устройство для функционального контроля интегральных схем | 1982 |

|

SU1180819A2 |

| Преобразователь параллельного кода в последовательный | 1982 |

|

SU1075253A1 |

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1229968A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

ПРЕОБРАЗОВАТЕЛЬ п-ЗНАЧНОГО ДВОИЧНОГО КОДА В р -ЗНАЧНЫЙ, содержащий первый и второй дешифраторы, первый и второй счетчики, первую и вторую схемы сравнения, регистр значности входного кода, регистр значности выходного кода, первую и вторую группь элементов И, сдвиговый регистр, первую, вторую и третью группы элементов ИЛИ, первый и второй триггеры блокировки, шесть элементов И, триггер подготовки, пять элементов ИЛИ, генератор импульсов, вход которого соединен с первым входом первого элемента И, второй и третий входы которого соединены соответственно с единичными выходами первого и второго тригге;ров блокировки, нулевые выходы которых являются соответственно выходами запроса и готовности преобразователя, вход установки нуля которого соединен с первыми входами первого, второго и третьего элементов ИЛИ, нулевым входом триггера подготовки и входом сброса сдвигового регистра, выходы которого соединены с первыми входами соответствующих элементов И второй группы, выходы которых являются информационными выходами преобразователя, входы значности входного и выходного кодов которого соединены соответственно с входами регистров значности входного и выходного кодов, вькоды которых соединены соответственно с входами первого и второго дешифраторов и первыми группами вхо-дов первой и второй схем сравнения, вторые группы входов которых соединены соответственно с выходами первого и второго счетчиков, разрядные входы первого счетчика соединены с выходом регистра значности выходного кода, выход первого элемента И соединен с первым входом второго сл элемента И, второй вход которого соединен с единичным выходом триггера подготовки, нулевой выход которого соединен с первым входом третьего элемента И. второй вход которого соединен с выходом четвертого элемента ИЛИ и с единичным входом триггера подготовки, а выход треел тьего элемента И соединен с вторым, О) входом третьего элемента ИЛИ, трео ел тий вход которого соединен с выходом второй схемы сравнения и с вторым входом второго элемента ИЛИ, выход которого соединен с входом сброса второго счетчика, а выход третьего элемента ИЛИ соединен с нулевым входом второго триггера блокировки, единичный вход которого соединен с выходом пятого элемента ИЛИ, первый вход которого соединен с выходом четвертого элемента И и с вторыми входами элементов И второй группы, второй вход пятого

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств согласования приборов

31

с различными разрядными сетками, а также приборов. работающих в последовательном и параллельном коде,

Целью изобретения является расширение функциональных возможностей за счет обеспечения преобразования последовательных кодов.

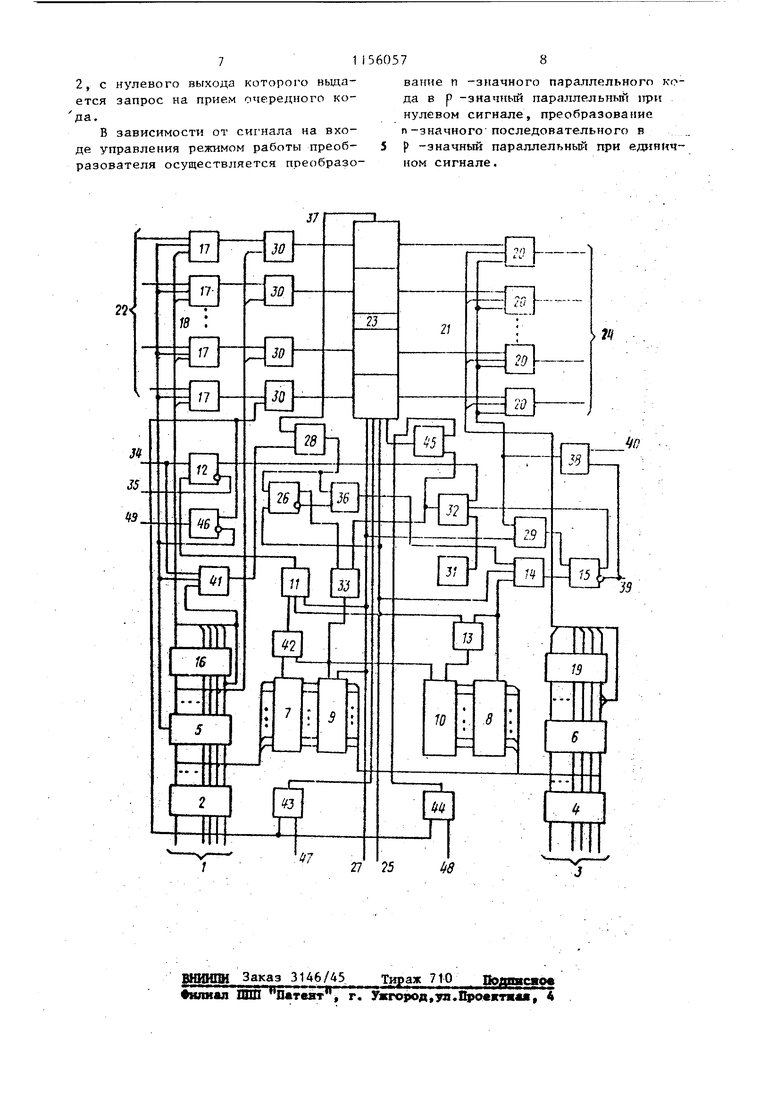

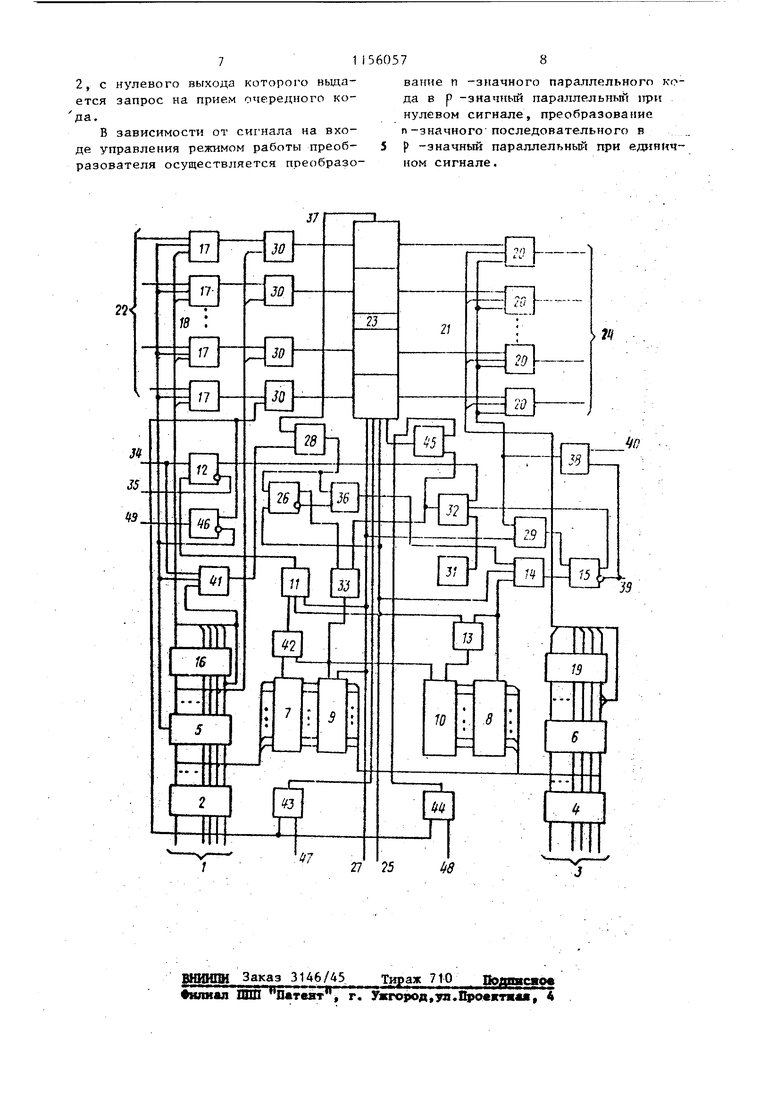

Структурная схема предлагаемого преобразователя приведена на чертеже .

Входы 1 значности входного кода соединены с входами регистра 2 значности входного кода, а входь 3 значности выходного кода соединены с входами регистра 4 значности выходного кода. Выходы регистров 2 и 4 соединены с дешифраторами 5 и 6 и со схемами сравнения 7 и 8, к которым подсоединены также выходы счетчиков 9 и 10. Выход элемента ИЛИ 11 подсоединен к нулевому входу триггера блокировки 12.

Выход схемы сравнения 8 соединен с входом элемента ИЛИ 13 и через элемент ИЛИ 14 - с нулевым входом триггера блокировки 15. Выходы деяшфратора 5 соединены через элементы ИЛИ 16 группы с элементами И 17 группы по следующему правилу: вход 18 -го элемента И 17 группы соединен через 1 -и элемент ИЛИ 16 группы со всеми выходами дешифратора 5, кроме первых (i-1) выходов. Вход 18 последнего элемента И 17 группы (верхнего по чертежу) соединен непосредственно с последним выходом дешифратора 5.

Выходы дешифратора 6 соединены через элементы ИЛИ 19 группы с входами элементов И 20 группы по следующему правилу: вход 21 элемента И 20 группы соединен через ч -и элемент ИЛИ 19 группы со всеми выходами дешифратора 6, кроме первых (ч-1) выходов 5 а вход 21 последнего элемента И 20 группы (нижний по чертежу) соединен непосредственно с последним выходом дешифратора 6.

Информационные входы 22 преобазователя соединены с элементами 17 группы. Выходы сдвигового реистра 23 через элементы И 20 групы соединены с информационными выодами 24 преобразователя. Вход 5 установки нуля преобразователя оединен с нулевым входом триггера одготовки 26 и через элементы 11, 14, 13 - с нулевыми входами тригге- ;

60574

ров блокировки 12, 15 и счетчика 10, Вход 27 подготовки соединен установочным входом сдвигового регистра, счетчика 9 и через элементы 5 ИЛИ 11 и 28 с нулевым входом триггера блокировки 12 и с единичным входом триггера блокировки 15 соответственно. Выходы элементов ИЛИ 29, 28 соединены соответственно с единичными входами триггера подготовки 26 и триггера блокировки 15. Выходы дешифратора 5 соединены с входами элементов ИЛИ 30 группы со сдвигом на один разряд (t й f5 выход дешифратора соединен с входом того элемента ИЛИ, выход которого соединен с входом ( +1)-го разряда сдвигового регистра 23).

Единичные выходы триггеров блокировки 15 и 12 и выход генератора импульсов 31 соединены с входами элемента И 32 и через элемент И 33 со счетным входом счетчиков 9 и 10. Вход разрешения записи 34 соединен 25 с единичным входом триггера блокировки 12, нулевой вход которого является выходом запроса 35 преобразователя. Нулевой выход триггера 26 соединен с входом элемента И 36. Вы ход 37 сдвигового регистра соединен с входом элемента ИЛИ 29. Вход элемента И 38 соединен с нулевым выходом триггера 15., который является выходом готовности 39 преобразова теля. Другой вход элемента И 38 яв ляется входом 40 разрешения считывания. Выходы элементов И 41 и 42 соединены с входами элементов ИЛИ 29 и 11 .

Элементы И 43 и 44 служат для подачи последовательного кода и синхросигналов , которые через элемент ИЛИ 45 поступают на вход сдвига регистра 23. Триггер режима 46 задает вид входной информации. Последовательный код поступает по входу 47, а синхросигнахсы - по входу 48 синхронизации. Вход 49 режима работы соединен с входом триггера 46,

0 Предлагаемый преобразователь работает следующим образом.

Перед началом работы преобразователь обнуляется. Дпя этого по входу 25 подается одиночный импульс,

5 обнуляющий сдвиговьп регистр 23,

триггер подготовки 26, триггеры блокировки 12 и 15 и счетчик 10. Затем по входам 1 и 3 записывается соответственно значность входного и выходного кодов в регистры 2 и 4 а по входу 49 в триггер режима работы 46 - ноль в случае преобразования параллельного кода в параллельньш и единица в случае преобразования последовательного кода в параллельный.

Число разрядов К регистров 2 и 4 определяется выражением К log N, где N - максимально возможная значtocTb входного и выходного кодов.

Если в триггер режима работы 46 записан ноль, то регистры 2 и 4 через дешифраторы 5 и 6 и элементы ИЛИ 16 и 19 выдают разрешение элементам И 17 и .20 на прием и выдачу соответственно входных и выходных кодов. Если в триггере 46 записана единица, то дешифратор 5, элементы И 17 и 41 заблокированы нулевым сигналом с нулевого выхода триггера 46 а регистр 4 через дешифратор 6 и элементы ИЛИ 19 вьщает разрешение элементам И 20 на выдачу выходного кода.

Затем на вход 27 подается сигнал подготовки, по которому в первом случае записывается единица в (h+1) разряд, а во втором - в младший разряд сдвигового регистра 23 при v -значности входного кода. В обоих случаях в счетчик 9 записывается значность р -выходного кода, триггер блокировки 15 устанавливается в единичное состояние, а триггер 12 - в нулевое. С нулевого выхода триггера блокировки 12 на вход 35. посылается сигнал готовности к приему входного кода, а на выходе 39 отсутствует сигнал готовности преобразователя вьщать выходной код, так как триггер 15 находится в единичном состоянии.

В первом случае входной код поступает по входам 22 через элементы групп и 17 и ИЛИ 30 в п младших разрядов регистра 23, во втором случае последовательный код через открытый элемент И 43 поступает на вход сдвигового регистра для последовательной информации, а на вход сдвига через элементы И 44 и ИЛИ 45 поступают импульсы синхронизации, которые продвигают по сдвиговому .регистру п -разрядный последовательньй код с единицей, записанной в процессе подготовки.

Последовательный код записывается в п младших разрядах сдвигового регистра, а в ()-M разряде - единица. После поступления входного кода в обоих случаях по входу 34 поступает сигнал сопровождения входного кода, который устанавливает триггер блокировки 12 в единичное состояние-, элемент И 32 деблокируется, тактовые импульсы начинают

поступать через элемент И 45 на вход сдвига сдвигового регистра 23 и сдвигать входной код разрядностью h и единицу, находящуюся в (П+1)

разряде.

Процесс подготовки продолжается до тех пор, пока единица подготовки движется по сдвиговому регистру 23. При выходе с последнего разряда единица подготовки через выход 37 и элемент ИЛИ 29 поступает на единичный вход триггера подготовки 26 и через открытый элемент И 36 н элемент ИЛИ 14 - на нулевой

вход триггера блокировки 15, При этом с единичного выхода триггера блокировки 15 подается запрещающий сигнал на элемент И 32, прерывающий подачу тактовых импульсов,. а

с нулевого по выходу 39 приемнику информации - сигнал готовности преобразователя к выдаче выходного кода. При этом выдается разрешение элементу И 38 на передачу поступакнцего по входу 40 сигнала считывания

выходного кода.

В дальнейшем при поступлении по входу 40 сигнала считывания выходного кода открываются элементы И 20

группы и считывается выходной код на выходы 24. Одновременно с этим триггер блокировки 15 устанавливается в единичное состояние и выдает разрешение элементу И 32 на пропускакие тактовых им1тульсов на счетньй вход счетчиков 9 и 10 и вход сдвига сдвигового регистра 23.

Как только на счетчике 10 будет записано число р за 2 тактов или

в счетчике 9 число п за (2 - 2) тактов, то сигнал со схемы сравнения 8 через элементы ИЛИ 13 и 14 обнуляет счетчик 10 и триггер блокировки 15, с нулевого выхода которого выдается сигнал готовности выдать код, или тактовый импульс через открытый элемент И 42 и элемент ИЛИ 11 обнуляет триггер блокировки 2 с нулевого выхода которого выдается запрос на прием очередного кода. В зависимости от сигнала на входе управления режимом работы преоб-5 разователя осуществляется преобразоIfSванне п -значного параллельного кода в р -значный параллельный 1фн нулевом сигнале, преобразование п-значного-последовательного в р -значньш параллельный при единичном сигнале.

| 1971 |

|

SU421989A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь @ -значного двоичного кода в @ -значный код | 1983 |

|

SU1087982A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-15—Публикация

1983-11-21—Подача