11

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении средств согласования устройств с различными разрядными сетками.

Целью изобретения является упрощение преобразователя.

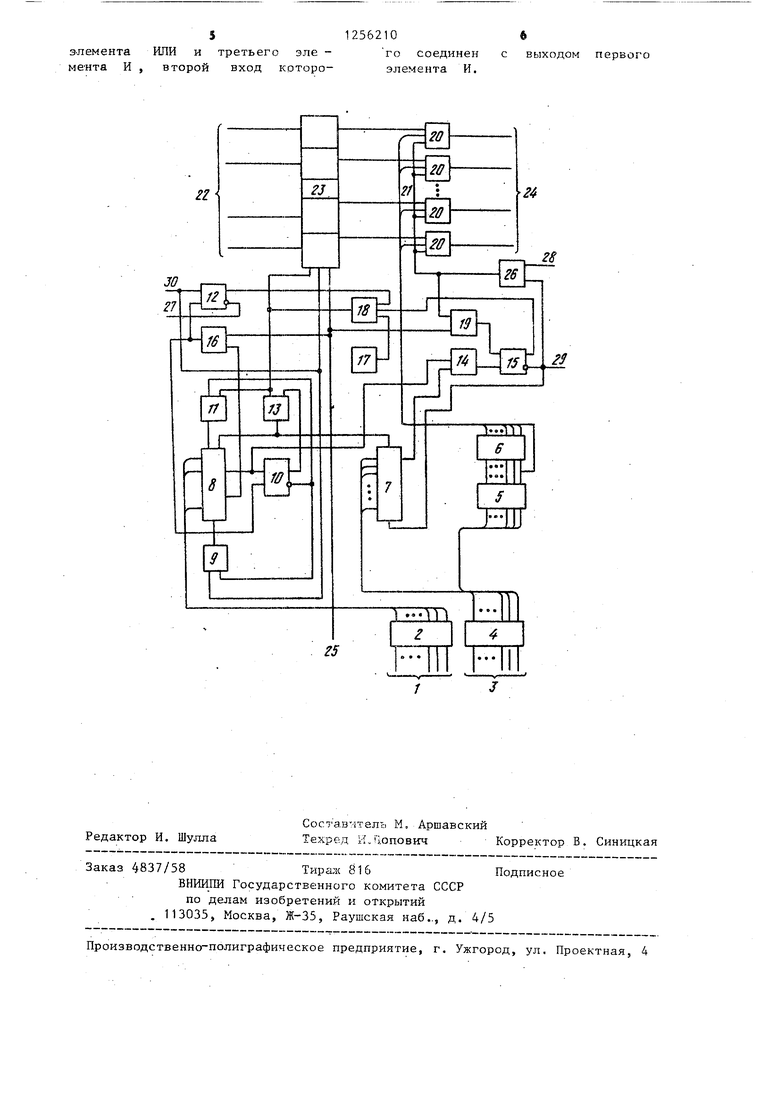

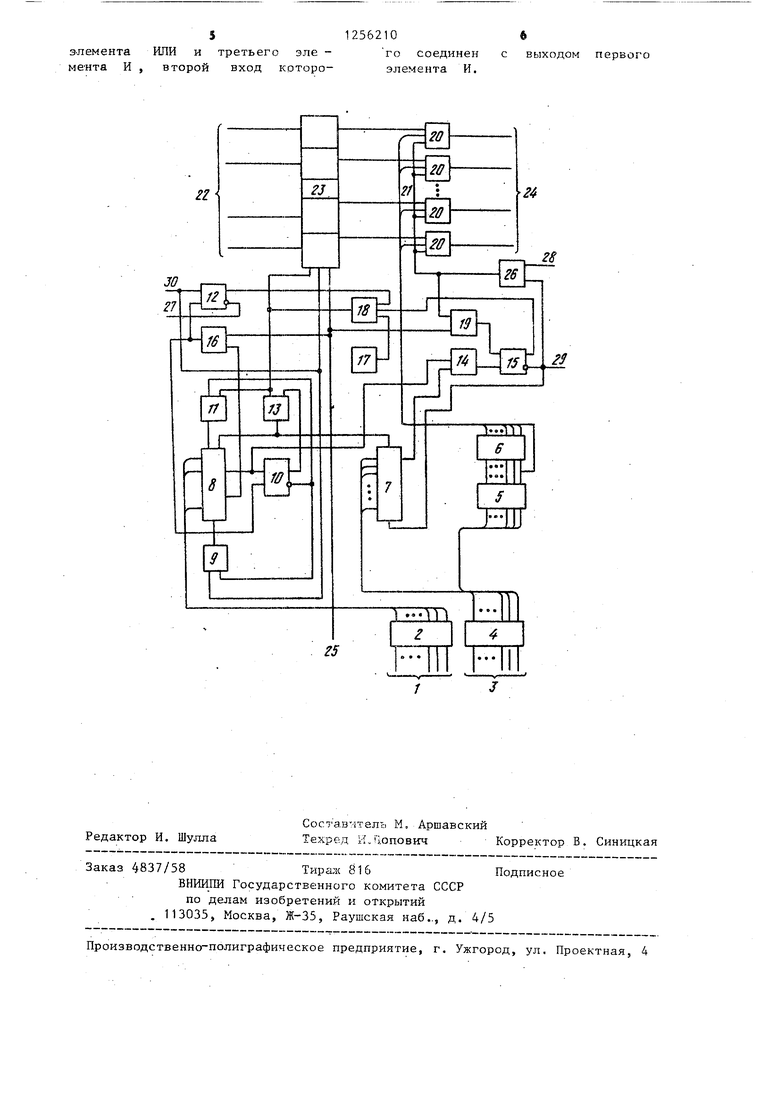

На чертеже приведена структурная схема преобразователя.

Преобразователь содержит- входы 1 значности входного кода, регистр 2 значности входного кода, входы 3 значности вьЕходного кода, регистр 4 значности выходного кода, дешифратор 5, группу элементов ШШ 6, счет чики 7 и 8, элемент ИЛИ 9, триггер 10 подготовки, элемент И 11, первьй триггер 12 блокировки,,элемент И 13, элемент ШШ 14, второй триггер 15 блокировки, элемент ИЛИ 16, генератор 17 импульсов, элемент И 18, элемент ИЛИ 19, группу элементов И 20, входы 21 элементов И группы, информационные входы 22 преобразователя, сдвигающий регистр 23, информационные выходы 24 преобразователя, вход 25 установки нуля преобразователя, элемент И 26, выход 27 запроса преобразователя, вход 28 разрешения считывания преобразователя, выход 29 готовности пре- образователя,вход 30 разрешения записи преобразователя.

Выходы дешифратора 5 соединены через элементы ИЛИ 6 группы с входами элементов И 20 группы по следующему правилу: вход 21 i -го элемента И 20 соединен через i -и элемент ИЛИ 6 со всеми выходами дешифратора 5, кроме перв-ых -1, а вход 21 последнего- элемента И 20 (нижнего по чертежу) - непосредственно с последним выходом дешифратора 5.

Предлагаемый преобразователь работает следующим образом.

Перед началом работы преобразова- тель обнуляется. Для этого по входу 25 подается одиночньш импульс, обнуляющий . сдвигающий регистр 23, триггер подготовки 10, триггер 12 блокировки и устанавливающий в единичное состоя ние триггер 15 блокировки. Затем по входам 1 на регистр 2 записывается значность п входного кода. Одновременно по входам 3 .и в регистр 4 записывается значность р выходного кода.

С нулевого выхода триггера 12 бло- .кировки на выход 27 подается сигнал готовности преобразователя к приему

10J

входного кода, а на выходе 29 отсутствует сигнал готовности преобразователя вьщать выходной код, так как триггер 15 находится в единичрго м состоянии.

Входной код поступает по входам 22. После установки входного кода по входу 30 поступает сигнал сопровождения входного кода,по которому происходят запись входного кода в сдвигающий регистр 23, запись значности h входного кода в счетчик 8, установка триггера 12 блокировки в единичное состояние, элемент И 18 деблокируется, тактовые импульсы начинают поступать на вход сдвига сдвигающего регистра и через открытый элемент И 11 на вход сложения счетчика 8. Счетчик 8 имеет разрядность X , где N - разрядность сдвигающего регистра.

Процесс подготовки продолжается до тех пор, пока счетчик 8 не выдает сигнал переноса. При заполнении счетчика 8 за (N-2) тактов, что соответствует сдвигу входного кода до старшего разряда сдвигающего регистра 23 .сигнал переноса поступает на единичный вход триггера 10 подготовки.и через элемент ИЛИ 14 на нулевой вход триггера 15 блокировки. При этом с единичного выхода триггера 15 подается запрещающий сигнал на элемент И 18, прерывающий подачу тактовых импульсов, а с нулевого - по выходу 29 приемника информации сигнал готовности преобразователя к вьщаче выходного кода. При этом вьщается разрешение элементу И 26 на передачу поступающему по входу 28 сигналу счи тьшания выходного кода.

Кроме того,, после перехода триггера 10 подготовки в единичное состояние выдается разрешение элементу И 13 на пропускание тактовых импульсов на входы счетчиков 8 и 7 на вычитание, происходит также запись значности и входного кода в счетчик 8

В дальнейшем при поступлении по входу 28 сигнала считывания выходного кода.открываются элементы И 20 группы и считывается выходной код.Одновременно, с этим триггер 5 блокировки переходит в единичное состояние происходит запись в счетчик 7 значности р выходного кода и выдает разрешение элементу И 18 на прохождение тактовых импульсов на вычитающие входы счетчиков 7 и 8, вход сдвига сдвигающего регистра 23.

Как только счетчик 7 выдает сигнал заема через 2 тактов или счетчик 8 за 2 тактов, то через элемент ИЛИ lAj обнуляется триггер 15 блокировки, с нулевого выхода которого выдается сигнал готовности выдать код, или через элемент ИЛИ 16 обнуляется триггер 12 блокировки, с нулевого вы- 10 хода которого вьщается запрос на прием очередного входного кода, и устанавливается в исходное состояние триг- .гер 10 подготовкиi

Сокращение оборудования в предла- fs гаемом преобразователе достигается за счет того, что в нем не используется лидирующая единица для фиксирования входного кода в сдвигающем регистре, поэтому исключены дешифратор ,20 две группы схем ИЛИ и входная группа схем И..

Формула изобретения

25

Преобразователь И -значного двоичного кода в р -значный, содержащий дешифратор, первый и второй счетчики, регистры значности входного и выходного кодов, группу элементов И, груп-30 пу элементов ИЛИ, сдвигающий регистр, триггер подготовки, первый и второй триггеры блокировки, четыре элемента И, четыре элемента ИЖ, генератор импульсов, выход которого соединен 35 с первым входом первого элемента И, второй и третий входы которого соединены соответственно с единичными выходами первого и второго триггеров блокировки, нулевые выходы которых я в-40 ляются соответственно выходами запроса и готовности преобразователя, вход установки нуля которого соединен с первыми входами первого и второго элементов PfflH и входом сброса сдви- 45 гающего регистра, вход сдвига которого соединен с выходом первого элемента И п с первым входом второго элемента И, второй вход которого соединен с единичным в ькодом триггера 50 подготовки, нулевой выход которого соединен с первым входом третьего элемента И, 1 -и выход дешифратора ( i 1-N, где N - максимальная значность выходного кода) соединен с входами 55 с первого по t -и элементов ИЛИ группы, -выходы элементов ИЛИ группы соединены соответственно с первыми входами элементов И группы, вторые входы которых соединены с выходом четвертого элемента ИЛИ и с вторым входом первого элемента ИЛИ, выход которого соединен с единичным входом второго триггера блокировки, нулевой выход которого соединен с первым входом четвертого элемента И, вт.орой вход которого соединен с входом разрешения считывания преобразователя,входы значности входного и выходного кодов которого соединены соответственно с входами регистра значности входного кода и регистра значности выходного кода, выходы которого соединены с входами дешифратора, выходы сдвигающего регистра соединены соответственно с третьими входами элементов И группы с. 1-го по (N-1) -и, третий вход N -го элемента И группы соединен с N -м выходом дешифратора, выходы элементов И группы являются информационными выходами преобразователя, вход разрешения записи которого соединен с единичным входом первого триггера блокировки, выход второго элемента И соединен с входами вычитания первого и второго счетчиков, выход третьего элемента ИЛИ соединен с нулевым входом второго триггера блокировки, отличающий- с я тем,что,с целью упрощения преобразователя , в нем разрядные входы сдвигающего регистра являются информационными входами преобразователя, вход разрешения записи которого соединен С установочным входом сдвигающего регистра и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с нулевым выходом триггера подготовки, единичный вход которого сое-- динен с выходом переноса первого счетчика и первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом заема второго счетчика, установочный вход которого соединен с нулевымвыходом второго триггера блокировки, разрядные входы первого и второго счетчиков соединены соответственно с выходами регистров значности входного и вькодного кодов, нулевые входы первого триггера блокировки и триггера подготовки соединены с выходом второ.го элемента ИЛИ, второй вход которого соединен с выходом

заема первого счетчика, входы установ ки и сложения которого соединены соответственно с выходами четвертого

51256210Ь

элемента ИЛИ и третьего эле - го соединен с выходом первого мента И , второй вход которо- элемента И.

Редактор И. Шулла

Сос7 ав - тель М. Аршавский

Техред ИЛоповкч Корректор В. Синицкая

Заказ 4837/58Тира;к816Подписное

Государственного комитета СССР по делам изобретений и открытий

. 113035, Москва, Ж-35, Раушская наб.., д, 4/5

Производственна-полиграфииеское предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь @ -значного двоичного кода в @ -значный код | 1983 |

|

SU1087982A1 |

| Преобразователь @ -значного двоичного кода в @ -значный | 1983 |

|

SU1156057A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ПЕРЕКРЫВАЮЩИХСЯ ШАБЛОНОВ БИТ В ДВОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2022 |

|

RU2787294C1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1501276A1 |

| Устройство для преобразования форматов слов двоичной последовательности | 1988 |

|

SU1513436A1 |

| Устройство для преобразования кодов с одного языка на другой | 1981 |

|

SU985793A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении средств согласования устройств с различнымиразрядными сетками. Целью изобретения является упрощение преобразователя. В предлагаемом преобразователе блок фиксации конца подготовительной части работы преобразователя использующий метод лидирующей единицы, заменен на счетчик длины слова. Кроме того, выходы регистров значности входного и выходного кодов соединены с разрядными входами счетчиков, выходы переноса и заема которых через элементы ИЖ соединены с нулевыми входами триггеров блокировки, установочные входы счетчиков соединены с нулевыми выходами триггера подготовки и второго триггера блокировки. 1 ил. I (Л

| 1971 |

|

SU421989A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь @ -значного двоичного кода в @ -значный код | 1983 |

|

SU1087982A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1985-02-12—Подача