вычислительного блока, выход умножителя J -го вычислительного

1179327

блока

является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень | 1983 |

|

SU1087990A1 |

| УСТРОЙСТВО для ВОЗВЕДЕНИЯ ЧИСЕЛ В СТЕПЕНЬ ЧЕТЬ[РЕ | 1971 |

|

SU290279A1 |

| Устройство для возведения в степень | 1978 |

|

SU752334A1 |

| Устройство для вычисления функции А @ | 1986 |

|

SU1383343A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

| Устройство для возведения в степень | 1985 |

|

SU1290308A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1133593A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Вычислительное устройство | 1983 |

|

SU1130862A1 |

| Устройство для возведения в степень | 1987 |

|

SU1434428A1 |

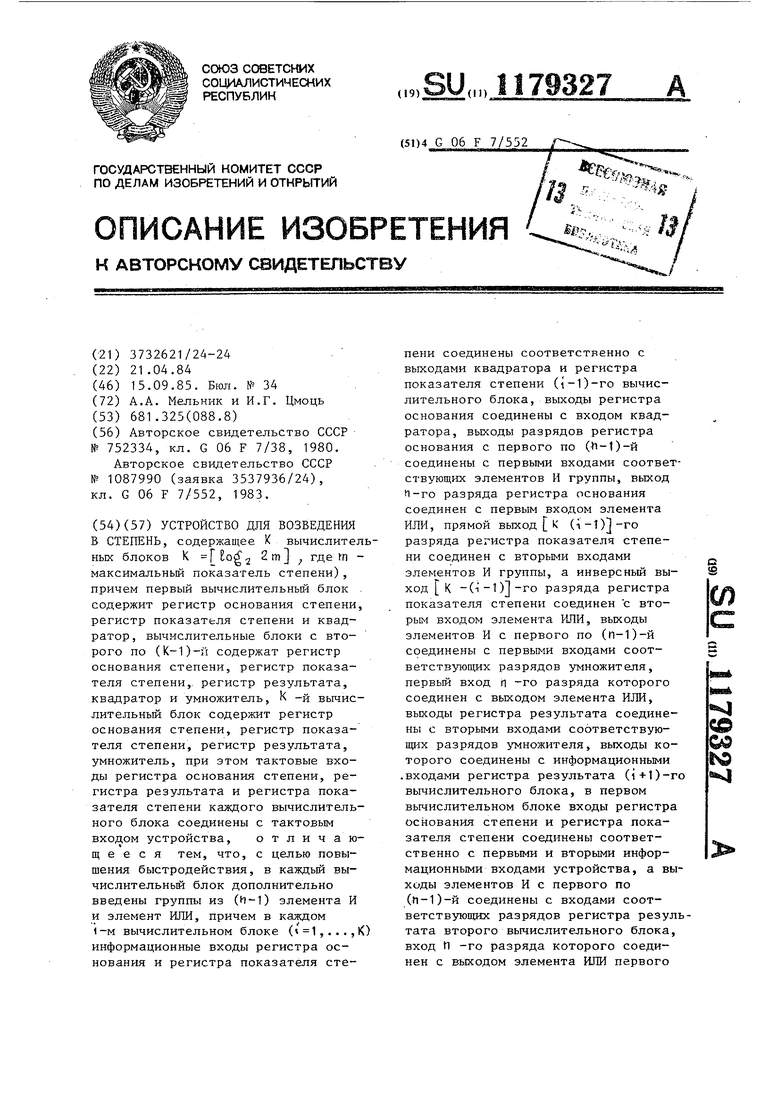

УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ Б СТЕПЕНЬ, содержащее К вычислительных блоков К ; Д максимальньм показатель степени), причем первый вычислительный блок . содержит регистр основания степени, регистр показателя степени и квадратор, вычислительные блоки с второго по (К-1)-й содержат регистр основания степени, регистр показателя степени,- регистр результата, квадратор и умножитель, -и вычислительньй блок содержит регистр основания степени, регистр показателя степени, регистр результата, умножитель, при этом тактовые входы регистра основания степени, регистра результата и регистра показателя степени каждого вычислительного блока соединены с тактовым входом устройства, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, в каждый вычислительньй блок дополнительно введены группы из (li-1) элемента И и элемент ИЛИ, причем в каждом 1-м вычислительном блоке ( 1,...,К) информационные входы регистра основания и регистра показателя степени соединены соответственно с выходами квадратора и регистра показателя степени (i-1)-ro вычислительного блока, выходы регистра основания соединены с входом квадратора, выходы разрядов регистра основания с первого по

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных устройствах обработки цифровой информации.

Цель изобретения - повьшение быстродействия.

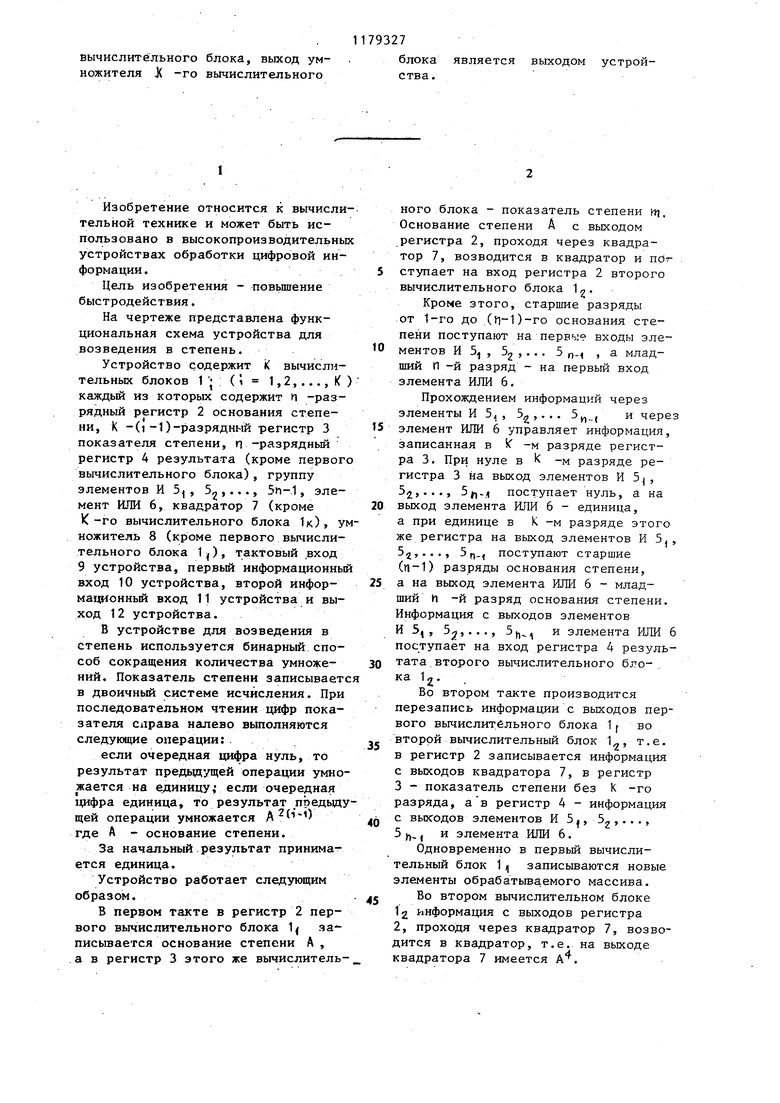

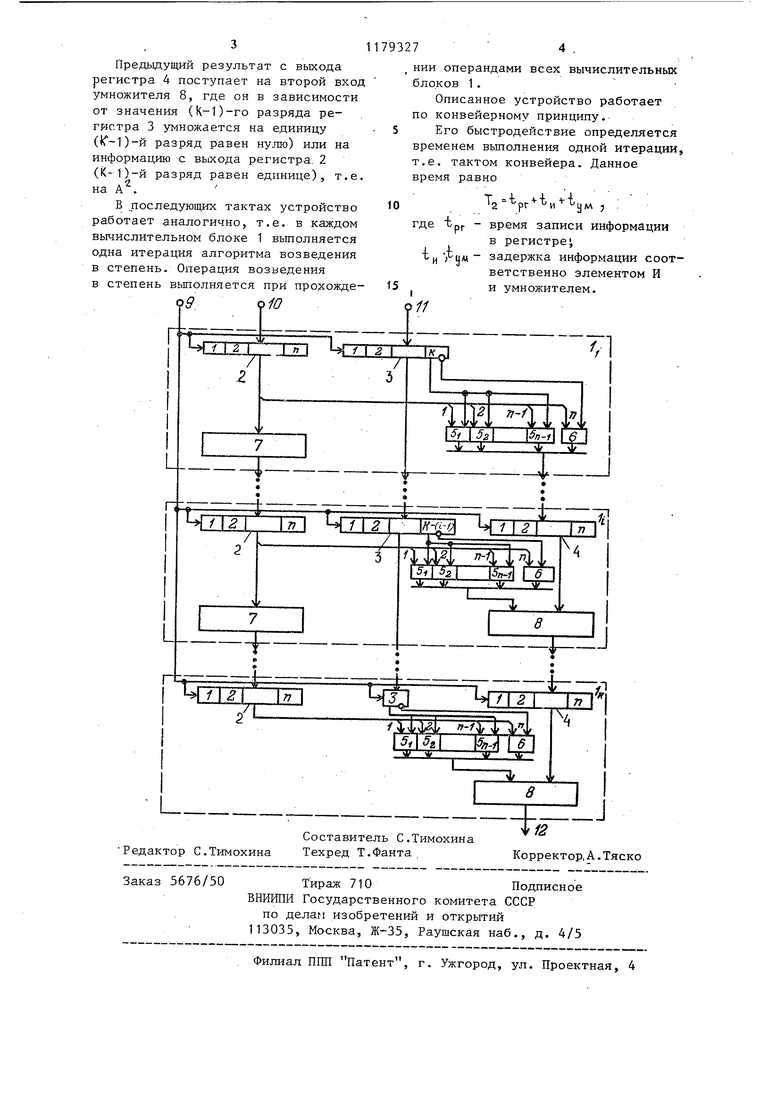

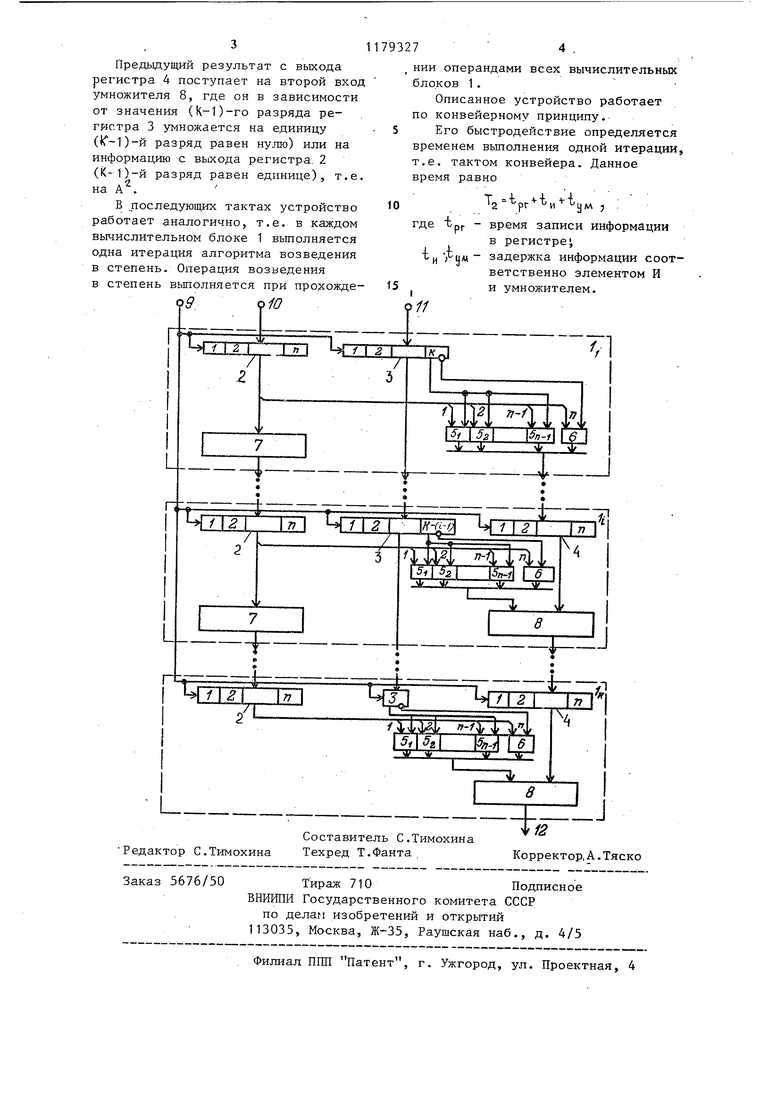

На чертеже представлена функциональная схема устройства для возведения в степень.

Устройство содержит К вычислительных блоков 1 ( 1 1,2, ..., К ) каждый из которых содержит и -разрядный регистр 2 основания степени, К -(i-1)-разрядный регистр 3 показателя степени, п -разрядный регистр 4 результата (кроме первого вычислительного блока), группу элементов И 5, З,j., 5п-1, элемент ИЛИ 6, квадратор 7 (кроме К -го вычислительного блока 1к), умножитель 8 (кроме первого вычислительного блока 1, тактовый вход 9 устройства, первый информационный вход 10 устройства, второй йнформац онньй вход 11 устройства и выход 12 устройства.

В устройстве для возведения в степень используется бинарный способ сокращения количества умножеНИИ. Показатель степени записываетс в двоичный системе исчисления. При последовательном чтении цифр показателя справа налево выполняются следующие операции:.

если очередная цифра нуль, то результат предыдущей операции умножается на единицу,- если очередная 1дифра единица, то результат предыдущей операции умножается А ( где А - основание степени.

За начальный результат принимается единица.

Устройство работает следующим образом.

В первом такте в регистр 2 первого вычислительного блока 1| записывается основание степени А , а в регистр 3 этого же вычислительного блока - показатель степени wi. Основание степени А с выходом регистра 2, проходя через квадратор 7, возводится в квадратор и поступает на вход регистра 2 второго вычислительного блока y,

Кроме этого, старшие разряды от 1-го до (li-1)-ro основания степени поступают на первые входы элементов И 5;, , 52 , ... 5 пн , а младший П -и разряд - на первый вход элемента ИЛИ 6.

Прохождением информации через элементы И 5, , 5д ,. . . 5j, и чере элемент ИЛИ 6 управляет информация, записанная в k -м разряде регистра 3. При нуле в -м. разряде регистра 3 на выход элементов И 5(, З,..., 5.1 поступает нуль, а на выход элемента ИЛИ 6 - единица, а при единице в К -м разряде этого же регистра на выход элементов И 5 5,..., 5 f,, поступают старшие (fl-1) разряды основания степени, а на выход элемента ИЛИ 6 - младший И -и разряд основания степени. Информация с выходов элементов И 5,, Sj,..., 3(, и элемента ИЛИ поступает на вход регистра 4 результата второго вычислительного блока 1 2. .

Во втором такте производится перезапись информации с выходов первого вычислит.ёльного блока 1 j во второй вычислительный блок 1- т.е. в регистр 2 записывается информация с выходов квадратора 7, в регистр 3 - показатель степени без К -го разряда, ав регистр 4 - информация с выходов элементов И 3 , 3,. . ., 3 У),, и элемента ИЛИ 6.

Одновременно в первый вычислительный блок 1ц записьшаются новые обрабатьтаемого массива.

Во втором вычислительном блоке 12 информация с выходов регистра 2, проходя через квадратор 7, возводится в квадратор, т.е. на выходе квадратора 7 имеется А .

Предьщущий результат с выхода регистра 4 поступает на второй вход умножителя 8, где он в зависимости от значения (К-1)-го разряда регистра 3 умножается на единицу (1С-1)-й разряд равен нулю) или на информацию с вькода регистра. 2 (1(-1)-й разряд равен единице), т.е. на А.

В ,1аоследующих тактах устройство работает аналогично, т.е. в каждом вычислительном блоке 1 выполняется одна итерация алгоритма возведения в степень. Операция возведения в степень выполняется при про сождео

НИИ операндами всех вычислительных блоков 1.

Описанное устройство работает по конвейерному принципу.

Его быстродействие определяется временем выполнения одной итерации т.е. тактом конвейера. Данное время равно

2 tyw 5

время записи информации

где

рг в регистреi

in (jnзадержка информации соответственно элементом И и умножителем.

| Устройство для возведения в степень | 1978 |

|

SU752334A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для возведения в степень | 1983 |

|

SU1087990A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-15—Публикация

1984-04-21—Подача