Изобретение относнтсв к области вычислвггельной техники и может быть иопользовано в различных вычислительных устройствах обработки информашш.

Известно устройство {ij содержащее блок программного управления, сумматор, узел сравнения, лопгческие элементы, формирователи и линии з шержки. Оно имеет низкую точность вьписления.

Наиболее близким по технической сущности к изобретению является устройство {2 , содержащее блок управления, первый элемет ИЛИ, результирующий сумматор и первый блок суммирования, причем первый, второй и третий выходы блока управления соединены соответственно с первым, вторым и треты1М входами первого блока суммирования, четвертый вход которого подключен к четвертому выходу блока управления, пвтый выхрд которого соединен с первым входом первого элемента ИЛИ второй вход которого подключен к первому первого блока суммирования, в

выход элемекЕта ИЛИ соединен со входом результирукмиего сумматора.

Недостатком известного устройства является низкая точность и быстродеЙ ствие.

Целью изобретения является повышокие точности и быстродействия.

Поставленная цель достигается тем, что В известно устройство дополнительрно введены (,т -1) алементов ИЛИ

ж -I) блоков суммирования, ( ж -1) элементов И и ( Ж -1) узлов умножения, причем первый, второй и третий входы ( m -l) блоков суммирования соединены с первым, вторым и третьим выходами блока управления, четвертый вы« ход которого подключен к четвертым входам ( nt-l) блоков суммирования, пятый выход блока управления соединен с первыми входами ( Ж-l) элементов ИЛИ|

второй вход каждого i -го ( i -2,3.. ..ж) лек|ента ИЛИ соединен с первым выходом 1 гго блока суммирования, а выход 1 -Фго элемента ИЛИ йодключён

3643

к пятому входу ( 1-1) блока суммирования, второй выход ( 1 -1) блока суммирования соединен через ( i -l) узел умножения с первым входом ( i -l) элемента И, второй вход которого подключей к шестому выходу блока /правления, а выход ( i -l) элемента И соединен с шестым входом -го блока суммиро. вания, кроьсе того, блок суммирова шя .содержат два элемента И, запоминаю щий регистр и сумматор, причем первый вход заяомина1сшего регистра соединен с первым входом блока суммирования, второй &ЗЕоа которого соед)1Нен с первым входом первого элемента И, второй вход которого подключен к выходу зашминакяаего регистра и первому ю 1ходу блока еумиироваяия, третий вход которого соединен с первым входом сумматора, второй вхоа которого подключен к выходу первого элемента И, третий вход сумматора соединено пятым входом блока суммирования, четвер тый вход которого соеайнен с первым входом второго элемента И, второй вход которого подключен к выходу сумматоре и второму выгоду блока суммировашш, шестой юсод ко1«рого соединен со вторым входом запемшаюшего регистра я выходом второго элемента И.

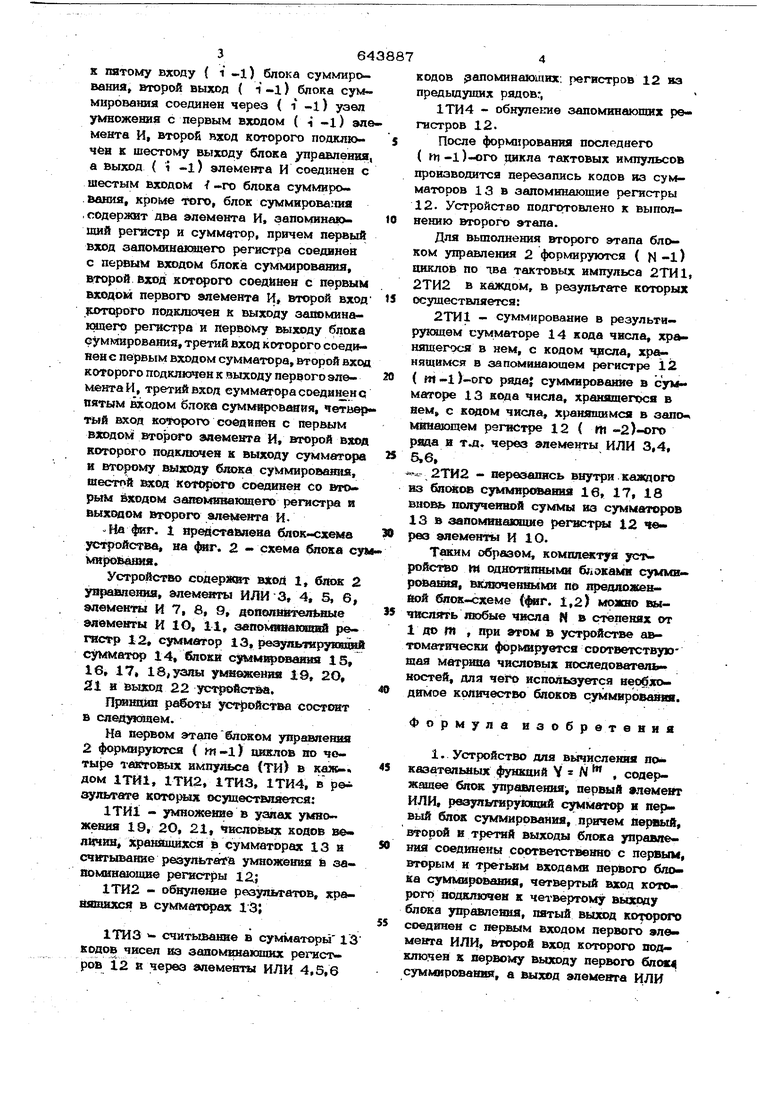

Ш , 1 яревств&яена блок-схедла ус ойсгва, на фкг. 2 схема блока сум мнроЁаЮ1Я.

Устройство содержат вход 1, бяок 2 увравяения, элементы ИЛИ 3, 4, 5, 6, элемен1гы И 7, 8, 9, допопштвя1лые

алементы И 1О, 11, зепом1Швкя)Ешй регистр 12, сумматор 13, реэуяьтарующий сумматор 14, блоки суммйрсивашш 15, 16, 17, 18, узлы умнеакеН1Ш 19, 2О, 21 и вызсод 22 устройет&а,

ЩлйШОИ работы устройства состоит в следующем.

На первом этапе@лежом управпешш 2 форкйруются { m-l) цваклов но четыре т ш товых импульса (ТИ) в каж дом 1ТЙ1, 1ТИ2, 1ТИЗ, 1ТИ4, в р© аульч-ате которых осуществляется;

1ТИ1 - умножемае в уапах умвожевия 19, 2О, 21, число аых кодов № Л1пи8, х:равЯщихся в сумматорах 13 н счт-ывание резуяьтата умножения 6 аааоминакмцие регистры 12;

1ТИ2 - обнуление резутштатов, хранявшхся в сумматорах 13;

1ТИЗ - считывание в сумматоры 13 кодов чисел 113 зааомхрюкшшх регистров 12 и через апемеетпы ИЛИ 4,5,6

кодов запоминающих; регистров 12 на предьвдуших рядов:,

- обнуление запоминающих регистров 12.

После формирования последнего ( fti-l)-oro цикла тактовых импульсов производится перезапись кодов из сумматоров 13 в запоминающие регистры 12. Устройство подготовлено к выполнению второго этапа.

Для вьшолнения второго этапа блоком управления 2 формируются ( М -1) шислов по 1ва тактовых импульса 2ТИ1, 2ТИ2 в каждом, в результате которых осуществляется:

2ТИ1 - суммирование в результи- руюшем сумматоре 14 кода числа, хранящегося в нем, с кодом чясла, хр нящимся в запоминающем регистре 12 ( m -1 )-ого ряда; суммирование в сумматоре 13 кода числа, хранящегося в нем, с кодом числа, хранящимся в запо-% минающем penaci 12 ( rti -2)-ого ряда в тл, через элементы ИЛИ 3,4, 5,6,

а. 2ТИ2 - перезапись внутри каждого вз блсжсж суммирования 16, 17, 18 вшж попучеявой суммы из сумматоров 13 в запомввахшше pemcTfnd 12 че рез элементы И 1О.

Таким образом, комплектуя уст ройство m однотв гаымн 6fioKiaMH суммвровашш, включенными п& предложенной &1ок-схеме (ф«г. 1,2) можно вычислять любые числа Н в степенях от 1 до rti , при этом в устройстве автоматически форми|дгвтся соответствующая матрша числовых носяедоватвлькостей, для чего используется необходимое количество блоксйв суммнров швя.

Формула изобретения

1. Устройство для вычисления по казатвлы{ых функций V г N , содержащее блок управления, первый ллвмент ИЛИ, рвзутлирукший сумматор и первый блок суммирования, причем , второй 8 третий выходы блсжа управления соединены соответственно с первым вторым и третьим входами nepisoro блока суммирования, четвертый вход которого подключен к четвертому выходу блока управлошш, пятый вьиюд которого соединен с входом первого эле мента ИЛИ, второй вход которого подключен к первому выходу первого блок суммировавдаг, а выход элемента ИЛИ

соединен со входом результирующего сумматора, отличающеесв тем, что, с целью повьиневия тояностн и быстродействия, в него дополнительно введены ( ) элементов ИЛИ, ( m-l) блоков суммирования, ( m-l) элементов И и ( Wl-l) узлов умноже ния, причем первый, второй я третий . входы { m -1) блоков суммирования соединены с первым, вторым и третьим выходами блока управления, четвертый выход которого подключен к четвертым входам ( m-l) блоков суммирования, пятый выход блока управления соединен с первыми входами (m-l) элементов ИЛИ, второй вход каждого i -го ( i - 2, 3, ... гп) элемента ИЛИ соединен с первым выходом i -го блсжа суммирования, а выход i -го элемента ИЛИ подключен к пятому входу ( 1 -l) блока суммирования, второй аыход ( i -1) блока суммирования соединен через ( i -l) узел умножения с пернлм входом ( i -l) элемента И, второй вход которого подключен к шестому выходу блсжа управления, а выход ( t -l) лемевта И соединен с шестым входом 1 -го блока суммирования.

2. Устройство по п. 1, 6 т я и чаюшееся тем, что блсж суммерования содержит два элемента И, оопоминакяикй регнстр и сумматор, причем первый вход звпоминаюшего ре гистра соединен с пе|жым входом блока суммирова:шя, второй вход которого соединеи с первым входом первого элемента И, второй вход которого подключен к выходу запоминающего регистра и первому выходу блока суммирования, третий вход которого соединен с первым входом сумматора, второй вход которого подключен к ылходу первого элемёш-а И, третий ывоа. сумматора соединен с пятым входом блока суммирования, четвертый вход которого соединен с первым входом второго элемента И, второй вход которого подключен к выходу сумматора и.второму вы4:оду блока суммирования, шестой вход которого соединен со вторым входом запоминающего регистра и выхо« дом второго элемента И.

Источники информапии, пришггыд во внимание при «Kcnept ae1.Г. Корн, Т Кори. Справочник по математике. М.. Наука, , стр. 33-34.,

2.Авторское свидетельство CCCf

N 378875, кл. Q Об Р 15/34, 1804.7

t.t

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислитель положения луча фазированной антенной решетки | 1982 |

|

SU1841222A1 |

| Устройство для преобразования координат | 1980 |

|

SU898426A1 |

| Интегро-арифметическое устройство | 1979 |

|

SU783813A1 |

| Устройство для преобразования координат | 1985 |

|

SU1254475A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для выполнения операций обращения матриц | 1985 |

|

SU1265796A1 |

| Устройство для преобразования координат | 1983 |

|

SU1141405A1 |

| Устройство для умножения чисел в @ -кодах Фибоначчи | 1980 |

|

SU1137459A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

Авторы

Даты

1979-01-25—Публикация

1976-07-13—Подача