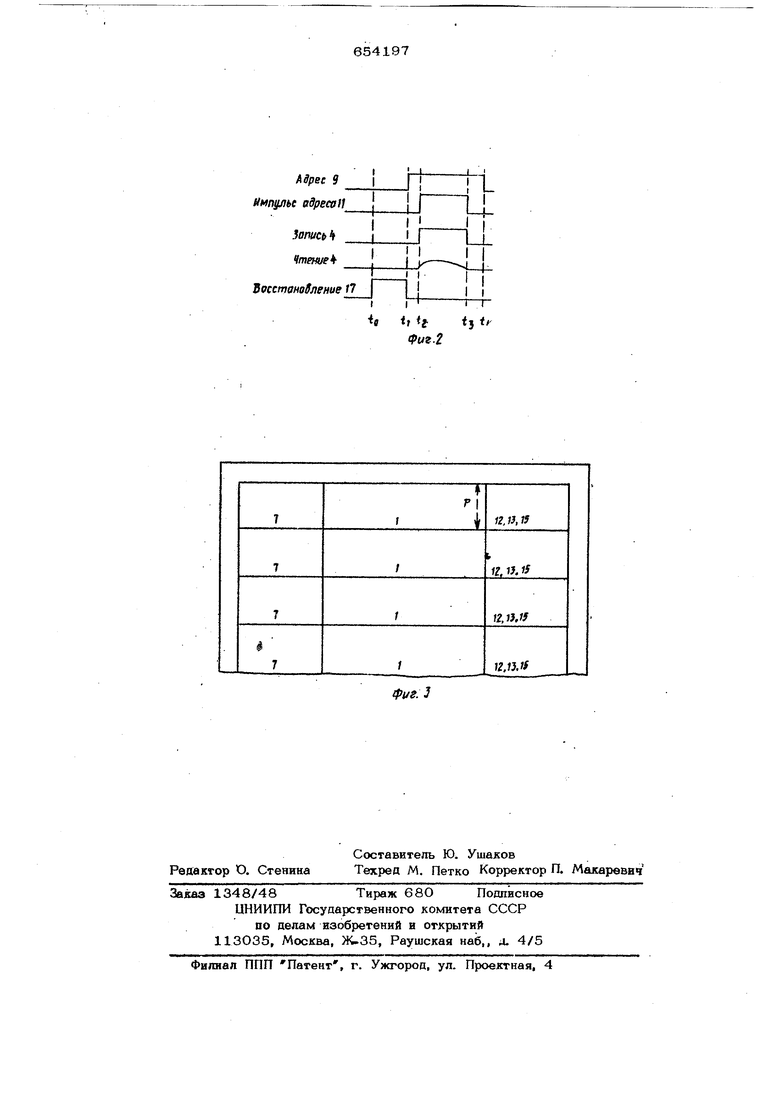

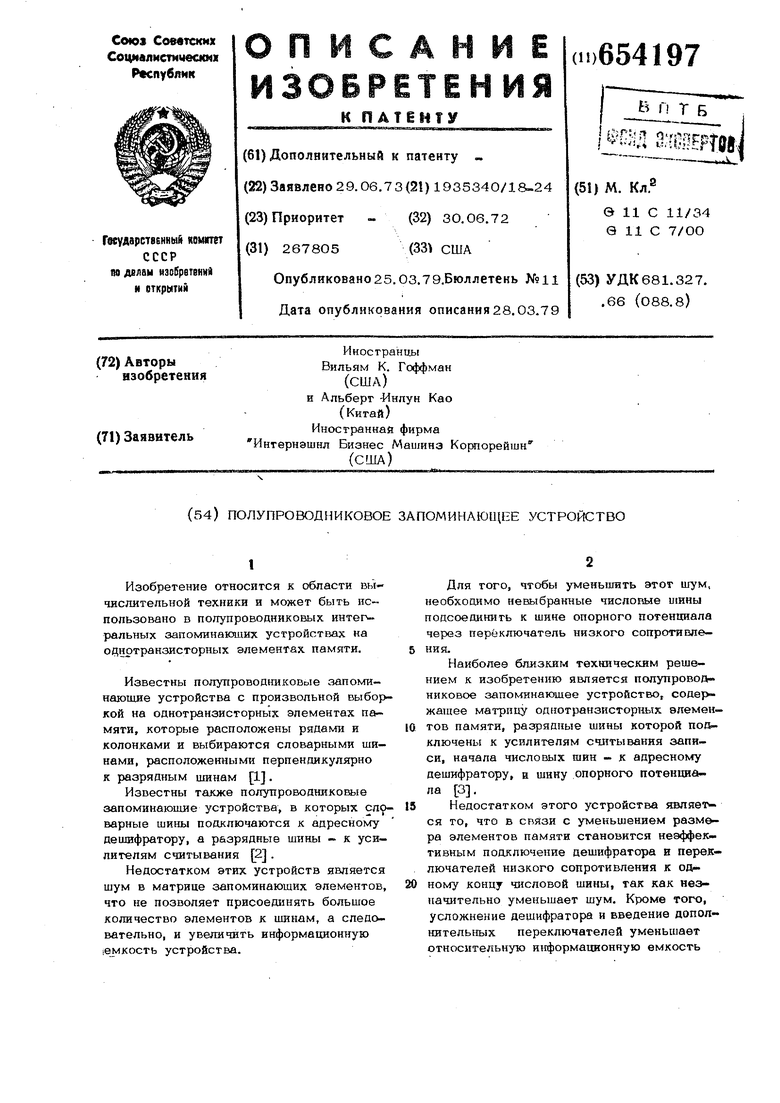

.устройства, так как требует дополпитель- пой. площади кристалла. ЦелБЮ изобретения является повышение ннформашюнной емкости н помехоус тойчлвости полупроводникового запоминаю шегс устройства. Поставленная цель достигается тем, что в полупроводниковое запоминающее устройство, содержащее матрицу элементов памяти, разрядные шины которой подключены к усилителям считывания записи, начала числовых щин - к адресному деилифратору, и шину опорного потенциала введены общий ключ, источник восстанав ливающего напряжения и два дополнитель- ных ключа для каждой числовой шины, ис точниквосстанавливающего напряжения че рез обший ключ подключен ко входу первого и одному из выходов второго допол нительных ключей, вход второго и один из выходов первого дополнительных ключей подключены к концу соответствующей числовой шины, другие выходы дополнительных ключей соединены с шиной опорног о потенциала. Подключение дополнительных ключей к концу числовой шины позволяетполучит большую гибкость при размещении устройства на полупроводниковой пластине, сохранить минимальный шаг между числовыми щинами и исключить дополнительные связи между адресным дешифратором и дополнительными ключами, что, в конечном счете, ведет к снижению уровня шума в матрице и повышеншо информационной емкости устройства. На фиг. 1 представлена электрическая схема полупроводш{кового запомина1 щего устройства; на фиг. 2 - временная диаграмма работы; на фиг. 3 - вариант размещения устройства на кристалле. Полупроводниковое зaпo щнaющee уст ройство содержит матрицу 1 элементов памяти 2, каждый из которых состоит из транзистора и конденсатора. Затворы транзисторов соеди 1ены с соотвегств то- шими числовыми шинами 3, а стоки - с соответствующими разрядными щинами 4, которые подключены к усилителям 5 считывания записи, одновременно разрядные шины подключены к элементам 6 согласования, которые могут быть 5Ыведены. Начала чиcлoB Jlx шин 3 подключены к адресному де1иифратору 7, который на вы ходе содержит коммутирующие транзисторы 8, saTBopf.i О которых соединен) с выходами потенциального декодера 10, истоки 11 coeutiFieui, с .мходами импуль674 сного декодера (на схеме не показан), а стоки - с выходами адресного дешифратора 7 и, следовательно, с соответствуюи ими числовыми шинами 3. Конец каждой числовой шины 3 подключен к одному из выходов первого дополнительного ключа 12 к входу второго дополнительного ключа 13. Входы всех первых 12 и выходы всех вторых 13 дополнительных ключей объединены в узел 14 и через общий ключ 15 подключены к источнику 16 восстанавливающего напр жения, на вход 17 общего ключа 15 подают импульс восстановления. Устройство содержит также шину опорного потенциала, общеизвестную для подобных устройств. Устройство работает в соответствии с временной диаграммой, приведенной на фиг. 2. В момент времени to на вход 17 общего ключа 15 поступает импульс восстановления, чтобы предварительно зарядить узел 14 для включения каждого первого дополнительного ключа 12 и подключения каждой числовой щины 3 к шине общего потенциала. В момент времени потенциального Декодера 10 на затворы 9 коммутирующих транзисторов 8 адресного дешифратора 7 поступает сигнал разрешения, а импульс восстановления выклкьчается. В момент времени ta на исток 11соответствующего коммутирующего транзистора 8 подается импульс адреса, в результате чего соответствующий транзистор 8 открывается и импульс строба адреса поступает на соответствующую числовую щину 3 и вход второго дополнительного ключа 13, который включаерся и разряжает узел 14, что приводит к включению первых дополнительных ключей 12и повыщению входного сопротивления соответствующей числовой шины 3. Невыбранные числовые шины 3 остаются при этом подключенными к шине опорного потенциала через соответствующие коммутирующие транзисторы 8. При записи единицы на разрядную шину 4 от усилителя считывания записи 5 одновременно подается импульс записи, что приводит к открытию транзистора элемента памяти 2 и заряду конденсатора. При записи нуля импульс записи не подается, и элемент памяти разряжается на разряд {ую шину 4. Запись заканчивается в момент времени ta включением имульса записи. При чтении сигнал на разрядной шине 4 усиливается усилителем считывания записи 5, Цикл обрадцения к памяти за,канчивавтся в момент времени tyC оконча нием сигнала разрешения адреса на затворах 9 коммутир тощих транзисторов 8. Затем, в момент времени toC импульса восстановления начинается новый цикл. Предлагаемое полупровощшковое запоминающее устройство обеспечивает равномерное я эффективное использование поверхности кристалла, на котором оно размешается, и одинаковый шаг р как матрицы 1 однотранзисторных элементов памяти, так и де1Ш1фратора и дополшгтель ных ключей с источником весе тана BfiHBaK шего напряжения и обшим ключом (см.фиг. З). При этом не требуетсявнугрен них связей между деш11фратором 7 и дополни тельгш ми ключами 12, 13 и обшим ключом 15, а внешние связи выполняются по периферии кристалла. При использовании данного изобретения наблюдается повышение информационной емкости устройства на 20% и значительное снижение уровня помех и шума. Формула изобретения Полупровопниковое запоминающее устройство, содержашее матрицу элементов памяти, разрядные шины которой подклк 1 чены к усилителям считывания записи, начала числовых шин - к адресному дешифратору, и шину опорного потенциала, отличающееся тем, что, с целью повышения информа шонной емкости и помехоустойчивости устройства, оно содержит обший ключ, источник восстанавливаюшего напряжения и два дополнительных ключа для каждой числовой шины, источник восстанавливающего напряжения через обший ключ подключен ко входу первого и одному из выходов второго дополнительных ключей, вход второго и один из выходов первого дополнительных ключей подключены к концу соответствующей числовой шины, другие выходы дополнительных ключей соединены с шиной опорного потенциала. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3387286, кл. 340-173, 1968. 2.Патент Швейцарки № 529419, кл. 6 11 С 7/О(3, 1972. 3.Патент США № 3510856, кл. 34О-173, 197О.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Запоминающее устройство | 1983 |

|

SU1112412A1 |

| Запоминающее устройство | 1975 |

|

SU604032A1 |

| Запоминающее устройство | 1973 |

|

SU481067A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОЦП•'t-li | 1971 |

|

SU419982A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

ППППП / д X f X г I X Z пилж X М

fiBpee 9 I

ампулы адресаП L J| j

Записи I I Г I I 4mmjek I

Ъосстано8ленае П

IL

Авторы

Даты

1979-03-25—Публикация

1973-06-29—Подача