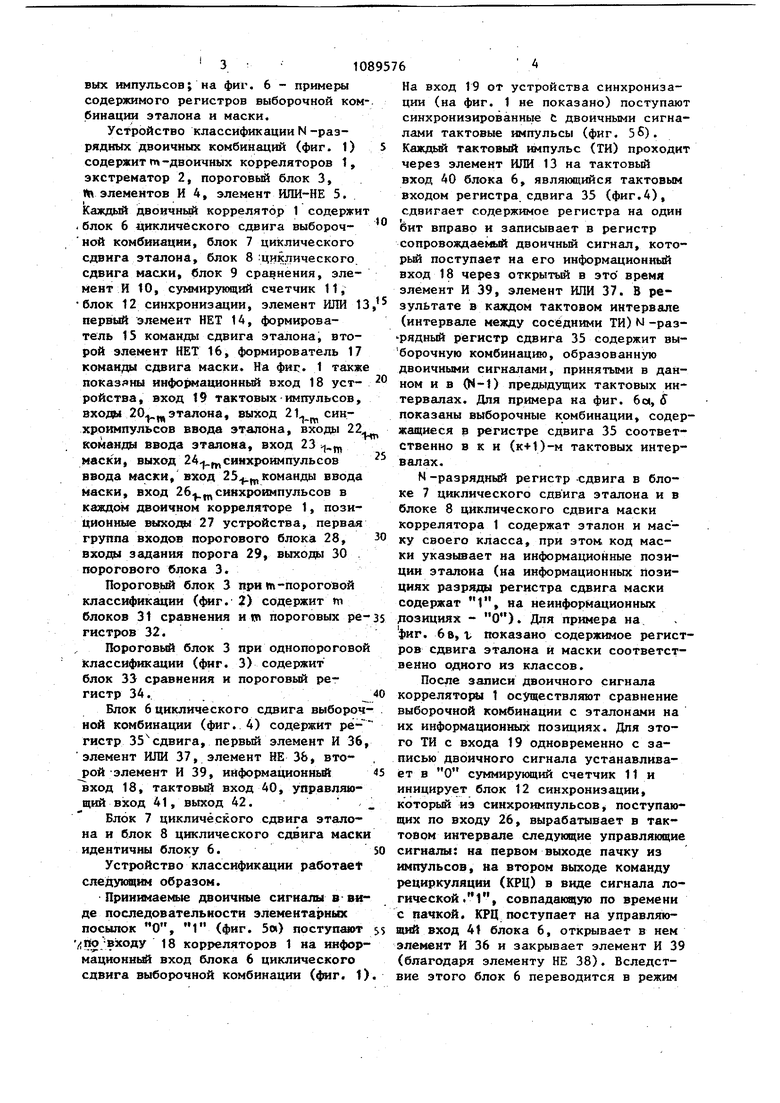

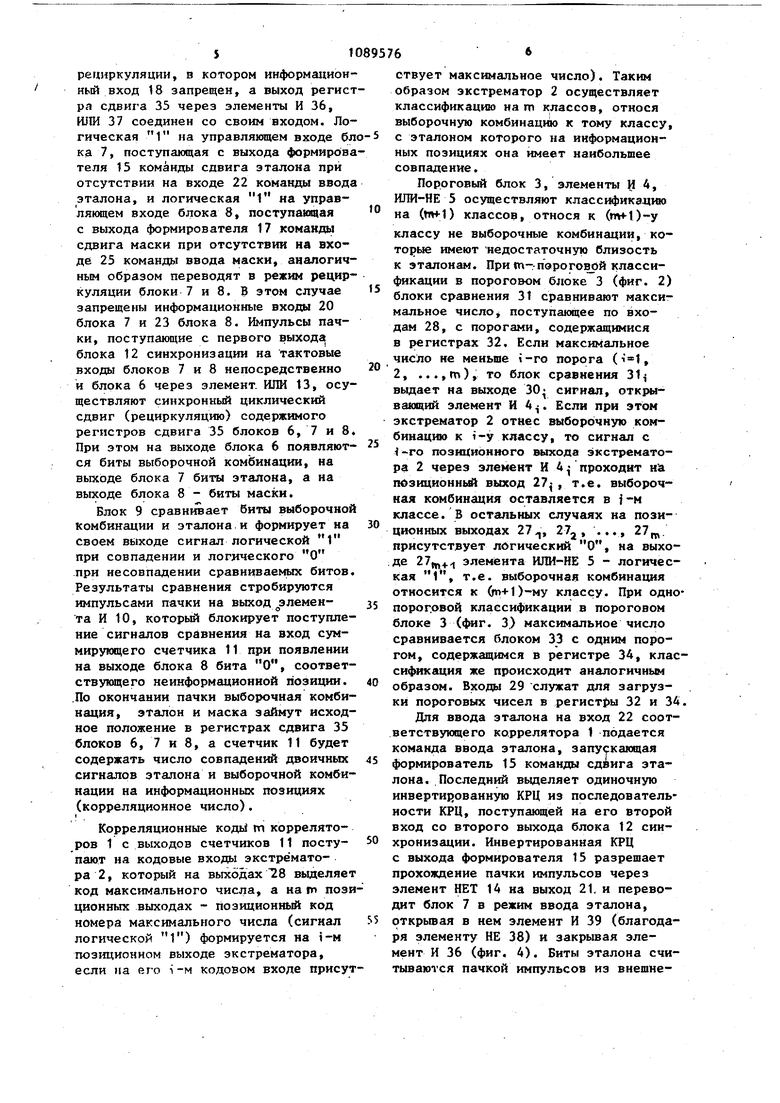

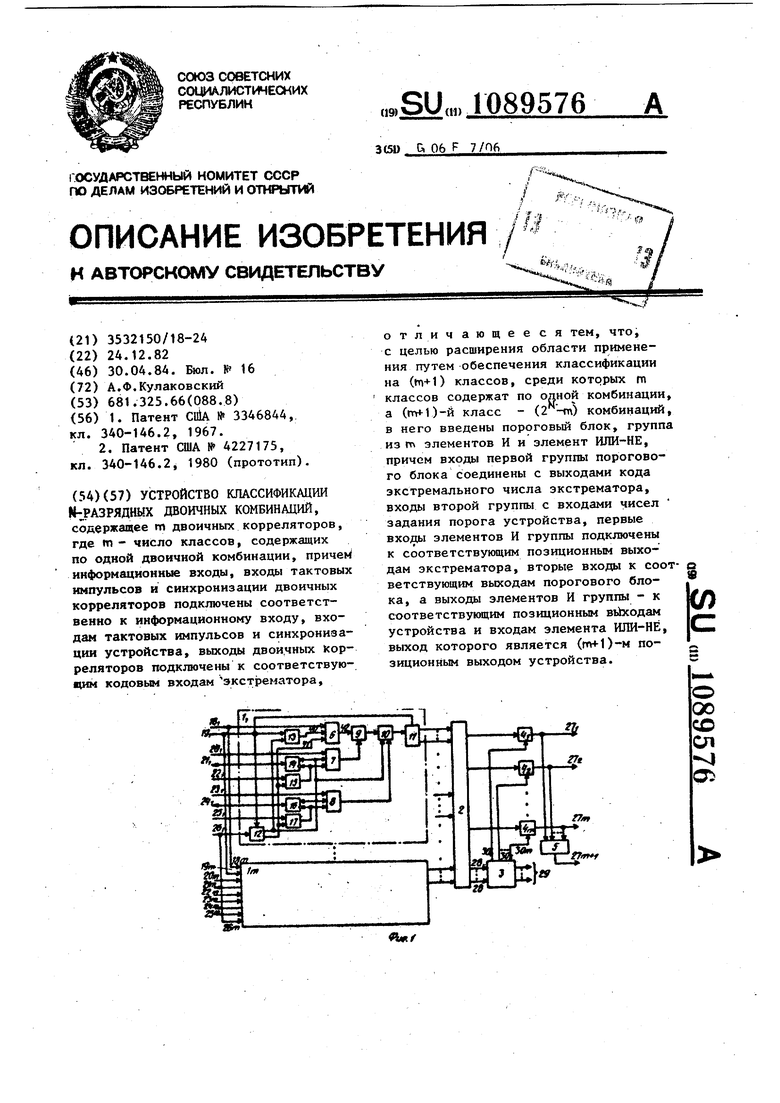

Изобретение относится к,связи и может использоваться в устройствах обработки дискретных сообщений для классификации -разрядных двоичных комбинаций ма m классов, содержащих по одной комбинацииt и один класс, содержащий 2 -т) комбинаций. Известно устройство классификации содержащее N-разрядный регистр сдвига, выходы разрядов.которого через элементы И подкш чены к вертикальным шинам блока памяти, m горизонтальных шин которого соединены через пороговые схемы с выходами устройства ft 1Недостатком данного устройства является низкая точность класси опсации в случаях, если алфавит выборочных комбинаций значительно превышает т. Ложная классификация при зтом определяется низкой разрешающей способностью аналоговой схемы формирования меры корреляции и большим числом комбинаций, близких к эталонам. Наиболее близким по технической бущИости к предлагаемому является устройство классификаций, содержащее Гп двоичных декодирутачих согласованных фильтров, выходы которых подключены к входам экстрематора, ко «горого является выходом устройства С 23. Не|1()остатком данного устройства является невозможность классификации в случаях, когда m классов содержат по одной комбинации, а (пн-1)-й класс - остальные (2 -гп) комбинаций. Этот недостаток определяется логикой работы устройства, которое гаобую из 2 выборочных комбинаций относит к одному из m классов. Этот недостаток в прищипе можно устранить, если в устройстве для (m-fl)-го класса ввести (2Г-т) двоичных декодирующих согласованных фильтров. Однако такое устройство классификации при больших М будет чрезвычайно сложньм. Вторьм недостатком устройства классификации является низкая оперативность его перестройки на новые эталоны классов, что связано с необходимостью замены согласованных филь ров. Этот недостаток может быть устранен применением вместо корреляторов на согласованных фильтрах цифровых двоичных корреляторов, содержащих регистр выборочной комбинации, регистр эталона и компаратор этих комбинаций. Однако недостатком такого коррелятора является невозможность использования эталонов, в которых присутствуют неинформационные позиции, т.е. позиции, двоичные сигналы которых не участвуют в сравнении с соответству1ощш и сигналами выборочной комбинации. Цель изобретения - расширение функциональных возможностей устройства классификации N-разрядных двоичных комбинаций путем обеспечения классификации на (пм-1) классов. Среди которых m классов содержат по одной комбинации,, а ()-й класс - (2 -п) комбинаций. Указанная цель достигается тем, что в устройство классификации N-разрядных двоичных комбинаций, содержащее m двоичных корреляторов, где т- число классов, содержащих по одной двоичной комбинации, причем информационные входа, входы тактовых импульсов и синхронизации двоичных корреляторов подключены соответственно к инфо1 1ационному входу, входам тактовых импульсов и синхронизации устройства, выходы двоичных корреляторов подювочены к соответств -ющим кодовым входам экстрематора, введены пьроговый блок, группа из in элементов И я элемент ШШ-НБ, причем входы первой группы порогового блока соединены с выходами кода экстремального числа экстрематорд, входы второй группы с входами чисел задания Порога устройства, первые входы элементов И группы подключены к соответствующим позиционным выходам зкстрематора вторые входь к соответствумцнм выходам порогового блока, а выхода элементов И группы - к соответствующим поэиционнът выходам устройства и входам элемента ШШ-КЕ, выход которого является (п+1)-м поЗИЦИОНН1М выходом устройства. На фиг. t приведена схема ус тройства класси1 кации (пример выполнения двоичного коррелятора N-разрядных двоичных комбинаций); на фиг.2 схема порогового блока при «п-пороговой классификации; на фиг. 3 - схема порогового блока при однопороговой классификации; на фиг. 4 - схема блока циклического сдвига комбинаций, входящего в состав двоичного оррелятора; на фиг. 5 - диаграммы входных двоичных сигналов и такто 3 10 вых импульсов; на фиг. 6 - примеры содержимого регистров выборочной комбинации эталона и маски. Устройство классификации N-разрядных двоичных комбинаций (фиг. 1) содержит т-двоичных корреляторов 1, экстрематор 2, пороговый блок 3, to элементов И 4, элемент ИЛИ-НЕ 5. Каждый двоичный коррелятор 1 содержит .блок 6 циклического сдвига выборочной комбинации, блок 7 циклического сдвига эталона, блок 8 :циклического. сдвига маски, блок 9 сравнения, элемент И 10, суммирующий счетчик 11, блок 12 синхронизации, элемент ИЛИ 13 первый элемент НЕТ 14, формирователь 15 команды сдвига эталона, второй элемент НЕТ 16, формирователь 17 команды сдвига маски. На фиг. 1 также показяны информационный вход 18 устройства, вход 19 тактовых импульсов, входа 20 эталона, выход синхроимпульсов вводе эталона, входы 22, команды ввода эталона, вход 23 , маски, выход 24 синхроимпульсов ввода маски, вход 25 „команды ввода маски, вход 26 „синхроимпульсов в каждом двоичном корреляторе 1, позиционные выхоли 27 устройства, первая группа входов порогового блока 28, входы задания порога 29, выходы 30 . порогового блока 3. Пороговый блок 3 при m-пороговой классификации (. 2) содержит m блоков 31 сравнения иип пороговых регистров 32.

Порогов блок 3 при однопороговой классификации (фиг. 3) содержит блок 33 сравнения и пороговый регистр 34. 40

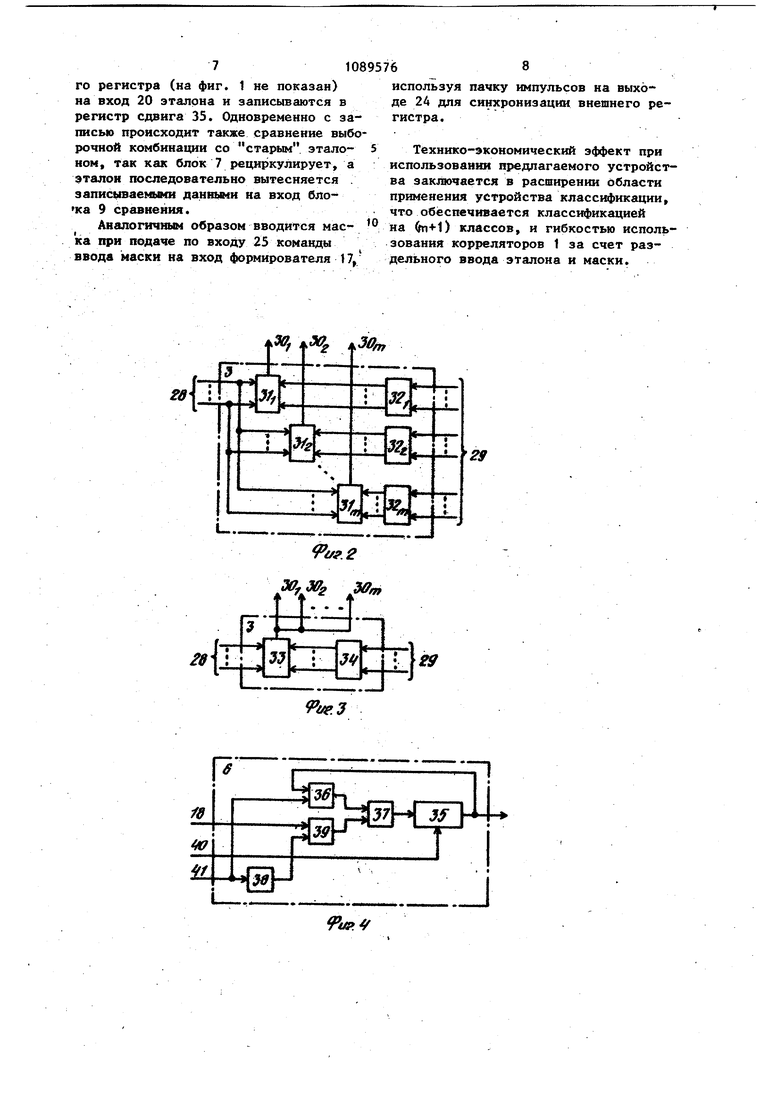

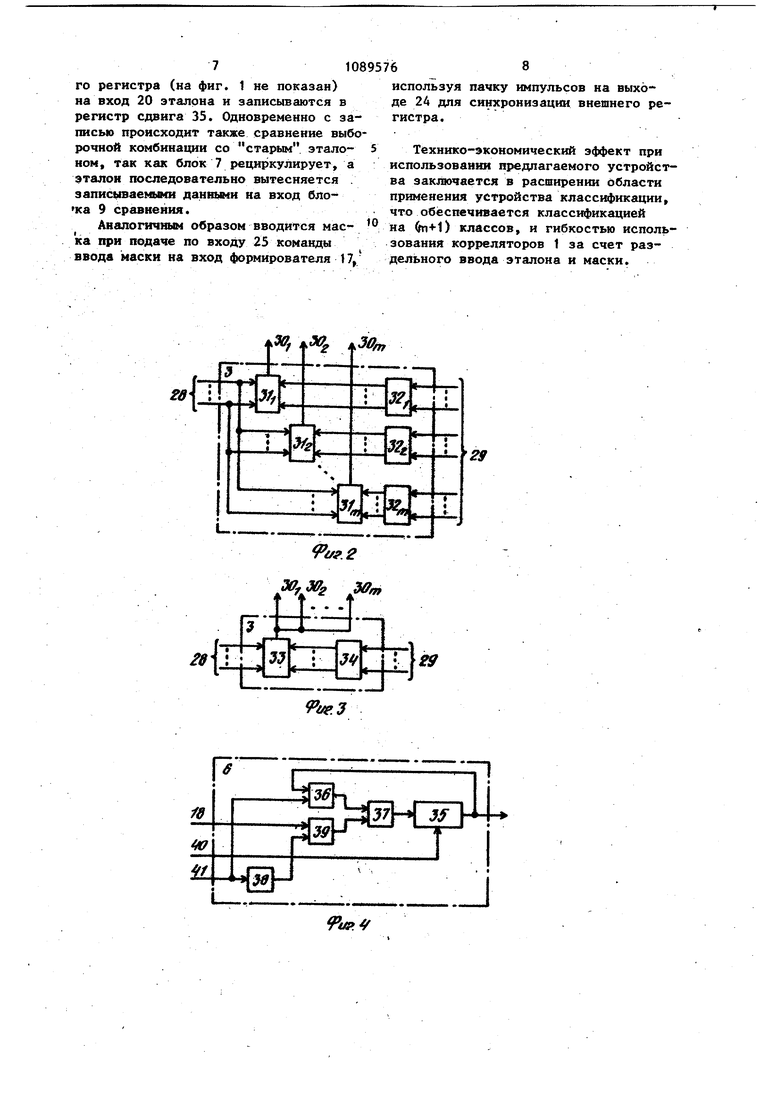

Блок 6 циклического сдвига выборочной комбинации (фиг. 4) содержит ре- гистр 35 сдвига, первый элемент И 36, элемент ИЖ 37, элемент НЕ 38, второй-элемент И 39, инфррмационньй 5 ход 18, тактовый вход 40, управляющий вход 41, выход 42. .

Блок 7 циклического сдвига эталона и блок 8 циклического сдвига маски идентичны блоку 6.50

Устройство классификации pa6oTaet следукщим образом.

Принимаеьше двоичные сигналы в-виде последовательности элементарных посылок О, 1 (фиг. 5«) поступают ss йо -входу 18 корреляторов 1 на информационный вход блока 6 циклического сдвига выборочной комбинации (фиг. 1).

ров сдвига эталона и маски соответственно рдиого из классов.

После 3алией двоичного сигнала корреляторы 1 осуществляют сравнение выборочной комбинации с эталонами на их информационных позициях. Для этого ТИ с входа 19 одновременно с записью двоичного сигнала устанавлива1вт в О суммирукадий счетчик 11 и иницирует блок 12 синхронизации, который иэ синхроимпульсов поступающих по входу 26, вырабатывает в тактовом интервале следующие управляющие сигна ш: на первом выходе пачку из импульсов, на втором выходе команду рециркуляции (КРЦ) в виде сигнала логической .I, совпадающую по времени с пачкой. КРЦ поступает на управляющ вход 4f блока 6, открывает в нем элемент И 36 и закрывает элемент И 39 (благодаря элементу НЕ 38). Вследствие этого блок 6 переводится в режим 6 На вход 19 от устройства синхронизации (на фиг. 1 не показано) поступают синхронизированные t двоичными сигналами тактовые импульсы (фиг. 5S). Каждьй тактовый импульс (ТИ) проходит через элемент ИЛИ 13 на тактовый вход 40 блока 6, являкяцийся тактовым входом регистра сдвига 35 (фиг.4), сдвигает содержимое регистра на один бит вправо и записывает в регистр сопровождаемый двоичный сигнал, которьШ поступает на его информационный вход 18 через открытый в это время элемент И 39, элемент ИЛИ 37. В результате в каждом тактовом интервале (интервале между соседними ТИ)N -разфядный регистр сдвига 35 содержит выборочную комбинацию, образованную двоичными сигналами, принятыми в данном и в (N-1) предыдущих тактовых интервалах. Для примера на фиг. бел, 6 показаны выборочные комбинации, содержащиеся в регистре сдвига 35 соответственно в к и (к+1)-м тактовых интервалах. N -разрядный регистр -сдвига в блоке 7 циклического сдвига эталона и в блоке 8 циклического сдвига маски коррелятора 1 содержат эталон и маску своего класса, при этом код маски указывает на информационные позиции эталона (на информационных Позициях разряды регистра сдвига маски содержат 1, на неинформационных дозициях - О). Для примера на фиг. бе, V показано содержимое регист$1рециркуляции, в котором информационный вход 18 запрещен, а выход регист ра сдвига 35 через элементы И 36, ИЛИ 37 соединен со своим входом. Логическая 1 на управляющем входе бл ка 7, поступающая с выхода формирЬва теля 15 команды сдвига эталона при отсутствии на входе 22 команды ввода эталона, и логическая 1 на управляющем входе блока 8, поступающая с выхода формирователя 17 команды сдвига маски при отсутствии на вхо де 25 команды ввода маски, аналогичным образом переводят в режим рециркуляции блоки 7 и 8. В этом случае запрещены информационные входы 20 блока 7 и 23 блока 8. Импульсы пачки, поступающие с первого выхода блока 12 синхронизации на тактовые входы блоков 7 и 8 непосредственно и блока 6 через элемент. ИЛИ 13, осуществляют синхронный циклический сдвиг (рециркуляцию) содержимого регистров сдвига 35 блоков 6, 7 и 8. При этом на выходе блока 6 появляются биты выборочной комбинации, на выходе блока 7 биты эталона, а на выходе блока 8 - биты маски. Блок 9 сравнивает биты выборочной комбинации и эталона и формирует на своем выходе сигнал логической 1 при совпадении и логического О при несовпадении сравниваемых битов. Результаты сравнения стробируются импульсами пачки на выход элемента И 10, который блокирует поступление сигналов сравнения на вход суммирующего счетчика 11 при появлении на выходе блока 8 бита О, соответствующего неинформационной позиции. .По окончании пачки выборочная комбинация, эталон и маска займут исходное положение в регистрах сдвига 35 блоков 6, 7 и 8, а счетчик 11 будет содержать число совпадений двоичных сигналов эталона и выборочной комбинации на информационных позициях (корреляционное число). Корреляционные кодь m корреляторов 1 с выходов счетчиков 11 поступают на кодовые входы экстрёматора 2, который на выходах 28 вьщеляет код максимального числа, а на m пози ционных выходах - позиционный код номера максимального числа (сигнал логической 1) формируется на i-м позиционном выходе экстрематора, если на его -i -м кодовом входе присут 6 ствует максимальное число). Таким образом экстрематор 2 осуществляет классификацию на m классов, относя выборочную комбинацию к тому классу, с эталоном которого на информационных позициях она имеет наибольшее совпадение. Пороговый блок 3, элементы И 4, ИЛИ-НЕ 5 осуществляют классификацию на () классов, относя к (ти-1)-у классу не выборочные комбинации, которые имеют -недостаточную близость к эталонам. При tn--пороговой классификации в пороговом блоке 3 (фиг. 2) блоки сравнения 31 сравнивают максимальное число поступающее по входам 28, с порогами, содержащимися в регистрах 32, Если максимальное число не меньше i-ro порога (, 2, ...,m), то блок сравнения 31 выдает на выходе 30 сигнал, открывающий элемент И 4.J. Если при этом экстрематор 2 отнес выборочную комбинацию к i-у классу, то сигнал с i-ro позиционного выхода экстремато- ра 2 через элемент И 4{ проходит НА позиционный выход 27, т.е. выборочная комбинация оставляется в j-м классе. В остальных случаях на позиционных выходах 27, 27, ..., 27fp. присутствует логический О, на выходе 27.,, элемента ИЛИ-НЕ 5 - логическая 1, т.е. выборочная комбинация относится к ОП+О-МУ классу. При одно пороговой классификации в пороговом блоке 3 (фиг. 3.) максимальное число сравнивается блоком 33 с одним порогом, содержащимся в регистре 34, классификация же происходит аналогичным образом. Входы 29 служат для загрузки пороговых чисел в регист{ ы 32 и 34. Для ввода эталона на вход 22 соответствующего коррелятора 1 подается команда ввода эталона, запускающая формирователь 15 команды сдвига эталона. .Последний выделяет одиночную инвертированную КРЦ из последовательности КГЦ, поступающей на его второй вход со второго выхода блока 12 синхронизации. Инвертированная КРЦ с выхода формирователя 15 разрешает прохождение пачки импульсов через элемент НЕТ 14 на выход 21. и переводит блок 7 в режим ввода эталона, открьгоая в нем элемент И 39 (благодаря элементу НЕ 38) и закрывая элемент И 36 (фиг. 4). Биты эталона считываются пачкой импульсов из внешнего регистра (на фиг. 1 не показан) на вход 20 эталона и записываются в регистр сдвига 35. Одновременно с записью происходит также сравнение выборочной комбинации со старым эталоном, так как блок 7 рециркулирует, а эталон последовательно вытесняется записмваемьв4И данкьми на вход блока 9 сравнения. Аналогичным образом вводится маска при подаче по входу 25 команды ввода маски на вход формирователя 17 108 6 используя пачку импульсов на вых6 де 24 дпя синхронизации внешнего регистра. Технико-экономический эффект при использовании предлагаемого устройства заключается в расширении области применения устройства классификации, что обеспечивается классификацией на Оп+1) классов, и гибкостью использования корреляторов 1 за счет раздельного ввода эталона и маски.

| название | год | авторы | номер документа |

|---|---|---|---|

| Обнаружитель комбинации двоичных сигналов | 1983 |

|

SU1270898A1 |

| Устройство классификации @ -разрядных двоичных комбинаций | 1983 |

|

SU1087985A1 |

| Выделитель составной комбинации двоичных сигналов | 1984 |

|

SU1223411A1 |

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Устройство приема двоичных сигналов | 1984 |

|

SU1197116A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1984 |

|

SU1156110A1 |

| Обнаружитель комбинаций двоичных сигналов | 1986 |

|

SU1356266A1 |

УСТРОЙСТВО КЛАССИФИКАЦИИ ПОРАЗРЯДНЫХ ДВОИЧНЫХ КОМБИНАЦИЙ, содержащее m двоичных корреляторов, где m - число классов, содержащих по одной двоичной комбинации, причей информационные входы, входы тактовых импульсов и синхронизации двоичных корреляторов подключены соответственно к информационному входу, входам тактовых импульсов и синхронизации устройства, выходы двоичных Корреляторов подключены к соответствующим кодовым входам экстрематора. отличающееся тем, что, с целью расширения области применения путем обеспечения классификации на (fn+O классов, среди которых m классов содержат по опной комбинации, а ()-й класс -

lh(ovf/cMf/Koffdt/ffotfffff нтче/т

eiMfffferowoff /ft dffifAXitf/ff

A

1-:: jfi

/ /

7bfyrr9 6f € ivime f& «SrSt /

TtfK/ifo t/

- -«ш@Ж::-;-,

Tb ftffM l

-g- Ufff ffotfifOf/

/ |Ш

Tixtyr Kf

T t;

vfffjif

-I

I t 11 I t

ffiifre

i/f.ff

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 4227175, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1984-04-30—Публикация

1982-12-24—Подача