,

Изобретение относится к области связи и может использоваться в устройствах обработки дискретных сообщений для обнаружения составной комбинации двоичных сигналов.

Цель изобретения - повышение точности выделения составной комбинации двоичных сигналов,

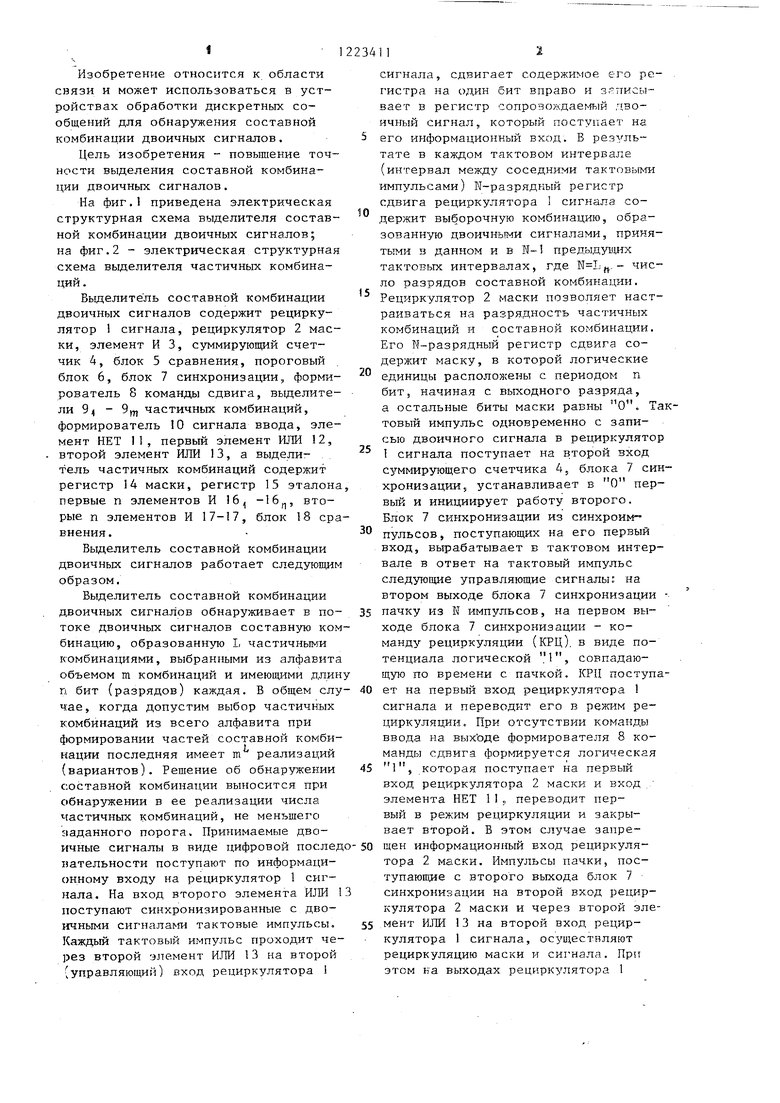

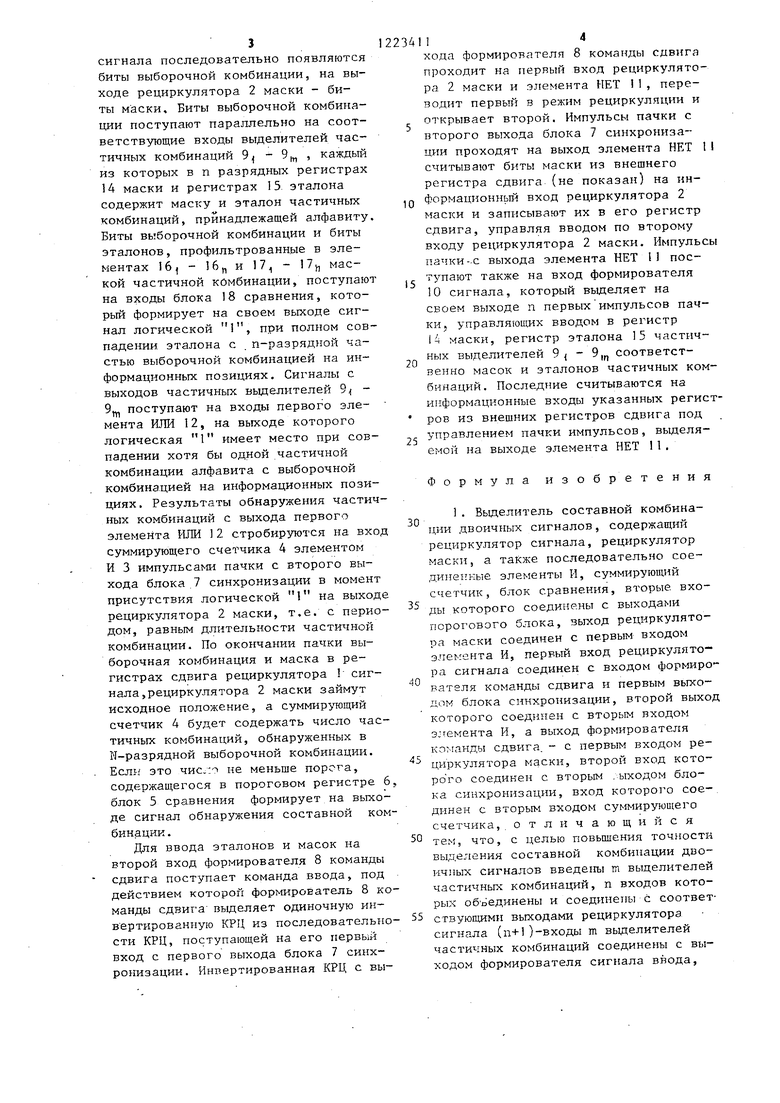

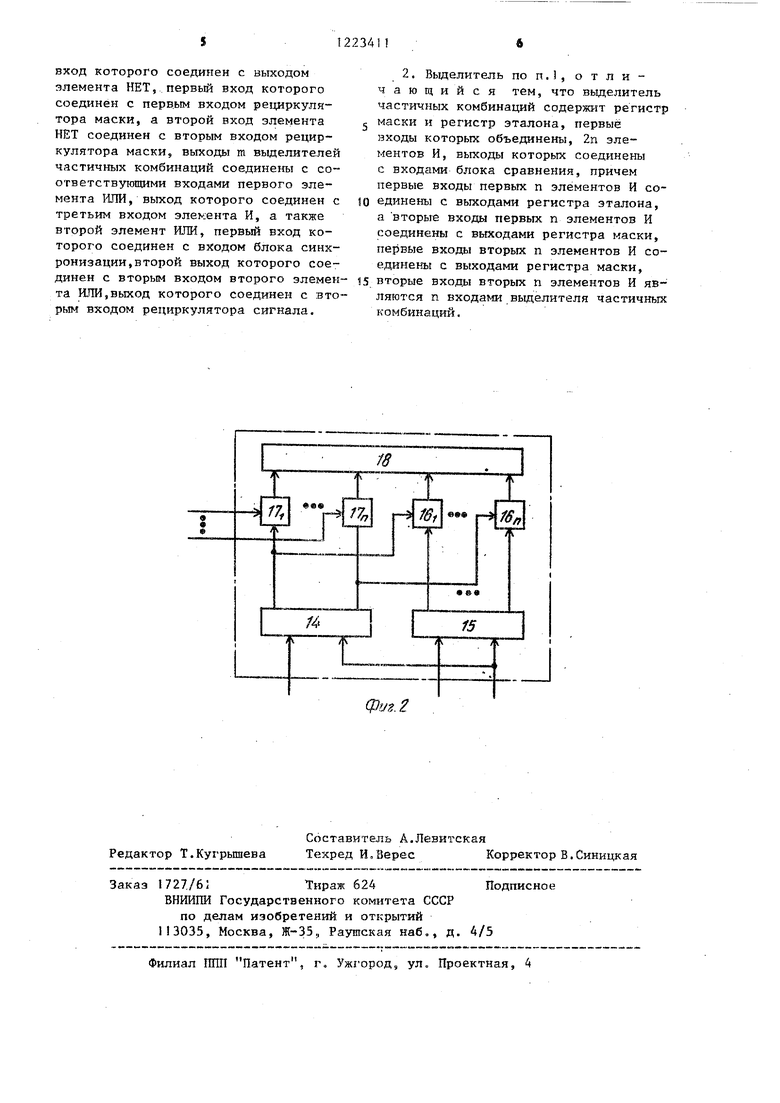

На фиг,1 приведена электрическая структурная схема выделителя состав ной комбинации двоичных сигналов; на фиг.2 - электрическая структурная схема выделителя частичных комбинаций.

Вьщелите ль составной комбинации двоичных сигналов содержит рецирку- лятор 1 сигнала, рециркулятор 2 маски, элемент И 3, суммирующий счетчик 4, блок 5 сравнения, пороговый блок 6, блок 7 синхронизации, форми- рователь 8 команды сдвига, выделители 94 - 9р1 частичных комбинаций, формирователь 10 сигнала ввода, элемент НЕТ 11, первый элемент ИЛИ 12, второй элемент ИЛИ 13, а выделитель частичных комбинаций содержит регистр 4 маски, регистр 15 эталона первые п элементов И 16 вторые п элементов И 17-17, блок 18 сравнения .

Вьщелитель составной комбинации двоичных сигналов работает следующим образом.

Выделитель составной комбинации двоичных сигналов обнаруживает в по- токе двоичных сигналов составную комбинацию, образованную L частичньми комбинациями, выбранными из алфавита объемом m комбинаций и имеющими длин п бит (разрядов) каждая. В общем слу чае, когда допустим выбор частичных комбинаций из всего алфавита при формировании частей составной комбинации последняя имеет m реализаций (вариантов). Решение об обнаружении составной комбинации выносится при обнаружении в ее реализации числа частичных комбинаций, не меньшего ;)аданного порога. Принимаемые двоичные сигналы в виде цифровой послед пательности поступают по информационному входу на рециркулятор 1 сигнала. На вход второго элемента ШШ поступают синхронизированные с двоичными сигналами тактовые импульсы, Каждый тактовый импульс проходит через второй элемент ИЛИ 13 на второй (управляющий) вход рециркулятора

5

5

0

5 0 5 0 5

сигнала, сдвигает содержимое его ре- , гистра на один бит вправо и з.писы- вает в регистр сопровождаег-1ый двоичный сигнал, который поступает на его информационный вход. В результате в каждом тактовом интервале (интервал между соседними тактовыми импульсами) N-разрядный регистр сдвига рециркулятора 1 сигнала содержит выборочную комбинацию, образованную двоичньми сигналами, принятыми в данном и в N-1 предыдукщх такто7зых интервалах, где , - число разрядов составной комбинации. Рециркулятор 2 маски позволяет настраиваться на разрядность частичных комбинаций и составной комбинации. Его N-разрядный регистр сдвига содержит маску, в которой логические единицы расположены с периодом п бит, начиная с выходного разряда, а остальные биты маски равны О. Тактовый импульс одновременно с записью двоичного сигнала в рециркулятор 1 сигнала поступает на второй вход суммирующего счетчика 4, блока 7 синхронизации, устанавливает в О первый и инициирует работу второго. Блок 7 синхронизации из cинxpoи { пульсов, поступающих на его первый вход, вырабатывает в тактовом интервале в ответ на тактовый импульс следзтощие управляющие сигналы: на втором выходе блока 7 синхронизации - пачку из N импульсов, на первом выходе блока 7 синхронизации - команду рециркуляции (КРЦ), в виде потенциала логической 1, совпадающую по времени с пачкой. КРЦ поступает на первый вход рециркулятора сигнала и переводит его в режим рециркуляции. При отсутствии команды ввода на вых оде формирователя 8 команды сдвига форьшруется логическая 1, которая поступает на первый вход, рециркулятора 2 маски и вход , элемента НЕТ 11, переводит первый в режим рециркуляции и закрывает второй. В этом случае запрещен информационный вход рециркулятора 2 маски. Импульсы пачки, пос- тупаюш51е с второго выхода блок 7 синхронизации на второй вход рециркулятора 2 маски и через второй элемент ИЛИ 13 на второй вход рециркулятора 1 сигнала, осуществляют рециркуляцию маски и сигнала. При этом ка выходах рециркулятора 1

сигнала последовательно появляются биты выборочной комбинации, на выходе рециркулятора 2 маски - биты маски. Биты выборочной комбинации поступают параллельно на соответствующие входы выделителей частичных комбинаций 9( - 9|„ , каждый из которых в п разрядных регистрах 14 маски и регистрах 15 эталона содержит маску и эталон частичных комбинаций, принадлежащей алфавиту. Биты выборочной комбинации и биты эталонов, профильтрованные в элементах 16, - 16„ и 17, - 17)1 маской частичной комбинации, поступают на входы блока 18 сравнения, который формирует на своем выходе сигнал логической 1, при полном совпадении эталона с п-разрядной частью выборочной комбинацией на информационных позициях. Сигналы с выходов частичных вьщелителей 94 - 9 поступают на входы первого эле- мента ИЛИ 12, на выходе которого логическая 1 имеет место при совпадении хотя бы одной частичной комбинации алфавита с выборочной комбинацией на информационных позициях. Результаты обнаружения частичных комбинаций с выхода первого элемента ИЛИ 12 стробируются на вхо суммирующего счетчика 4 элементом И 3 импульсами пачки с второго выхода блока 7 синхронизации в момент присутствия логической 1 на выход рециркулятора 2 маски, т.е. с периодом, равным длительности частичной комбинации. По окончании пачки выборочная комбинация и маска в регистрах сдвига рециркулятора 1 сигнала, рециркулятора 2 маски займут исходное положение, а суммирзлощий счетчик 4 будет содержать число частичных комбинаций, обнаруженных в N-разрядной выборочной комбинации. Если это чис.:о не меньше порога, содержащегося в пороговом регистре 6 блок 5 сравнения формирует на выходе сигнал обнаружения составной комбинации .

Для ввода эталонов и масок на второй вход формирователя 8 команды сдвига поступает команда ввода, под действием которой формирователь 8 команды сдвига выделяет одиночную ин- в ертированную КРЦ из последовательности КРЦ, поступающей на его первый вход с первого выхода блока 7 синхронизации. Инвертированная КРЦ с вы2341I4

хода формирователя 8 команды сдвига проходит на первый вход рециркулятора 2 маски и элемента НЕТ 11, переводит первый в режим рециркуляции и открывает второй. Импульсы пачки с второго выхода блока 7 синхронизации проходят на выход элемента НЕТ II считывают биты маски из внешнего регистра сдвига (не показан) на ин- Q формационньш вход рециркулятора 2 маски и записывают их в его регистр сдвига, упр.авляя вводом по второму входу рециркулятора 2 маски. Импульсы пачки-с выхода элемента НЕТ 11 поступают также на вход формирователя 10 сигнала, который выделяет на своем выходе п первых импульсов пачки, управляющих вводом в регистр 14 маски, регистр эталона 15 частичных выделителей 9 - 9, соответственно масок и эталонов частичных комбинаций . Последние считываются на информационные входы указанных регист- ров из внешних регистров сдвига под -,. управлением пачки импульсов, выделяемой на выходе элемента НЕТ 11.

Формула изобретения

15

1. Выделитель составной комбинации двоичных сигналов, содержащий рециркулятор сигнала, рециркулятор маски, а также последовательно соединенные элементы И, суммирующий счетчик, блок сравнения, вторые вхо- ды которого соединены с выходами

порогового блока, выход рециркулятора маски соединен с первым входом элемента И, первый вход рециркулятора сигнала соединен с входом формирователя команды сдвига и первым выходом блока синхронизации, второй выход которого соединен с вторым входом э. емента И, а выход формирователя команды сдвига. - с первым входом рециркулятора маски, второй вход кото- ро го соединен с вторым /ыходом блока синхронизации, вход которого сое-. дивен с вторым входом суммирующего счетчика, отличающийся

тем, что, с целью повышения точности

выделения составной комбинации двоичных сигналов введены m выделителей частичных комбинаций, п входов которых объединены и соединены с соответ- ствующими выходами рециркулятора сигнала (n+i)-входы m выделителей частичных комбинаций соединены с выходом формирователя сигнала ввода.

вход которого соединен с выходом элемента НЕТ, первый вход которого соединен с nepBbtM входом рециркуля- тора маски, а второй вход элемента НЕТ соединен с вторым входом рецир- кулятора маски, выходы m вьщелителей частичных комбинаций соединены с соответствующими входами первого элемента I-UIH, выход которого соединен с третьим входом элемента И, а также второй элемент ИЛИ, первый вход которого соединен с входом блока синхронизации, в торой выход которого соединен с вторым входом второго элемента ИЛИ,выход которого соединен с вторым входом рециркулятора сигнала.

2. Выделитель по п., о т л и - чающийся тем, что выделитель частичных комбинаций содержит регистр

маски и регистр эталона, первые входы которых объединенъ, 2п элементов И, выходы которых соединены с входами блока сравнения, причем первые входы первых п элементов И соединены с выходами регистра эталона, а вторые входы первых п элементов И соединены с выходами регистра маски, первые входы вторых п элементов И соединены с выходами регистра маски,

вторые входы вторых п элементов И являются п входами вьщелителя частичных комбинаций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство классификации N-разрядных двоичных комбинаций | 1982 |

|

SU1089576A1 |

| Обнаружитель комбинации двоичных сигналов | 1983 |

|

SU1270898A1 |

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Выделитель комбинации цифровых сигналов | 1979 |

|

SU882029A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Устройство приема двоичных сигналов | 1984 |

|

SU1197116A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1984 |

|

SU1156110A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1140172A1 |

Изобретение относится к связи и может быть использовано в устройствах обработки дискретных сообщений для обнаружения составной комбинации двоичных сигналов. Изобретение повы/ ЛЩ7. шает точность выделения составной комбинации двоичных сигналов. Устройство содержит рециркулятор 1 сигнала, рециркулятор 2 маски, элемент ИЗ, суммирующий счетчик 4, блок 5 сравнения, пороговьпЧ блок 6, блок 7 синхронизации, формирователь 8 команды сдвига, вьщелители 9, - 9 частичных комбинаций, формирователь 10 сигнала ввода, элемент НЕТ 11, два элемента ИЛИ 12, 13. Цель достигается введением выделителей частичных комбинаций, каждьш из которых состоит из регистра рециркуляторов маски и эта лона, 1 - п элементов И, 2 - п элементов И, блока сравнения, 1 з.п. . ф-лы. 2 ил. (О «М ts5 Ь9 Од 4: фЦ1.1

Ф.

Редактор Т.Кугрышева

Составитель А.Левитская

Техред И,Верес Корректор В.Синицкая

Закаэ 172776;Тираж 624Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35,, Раугаская набо, д. 4/5

Филиал ППП Патент, г, Ужх ород, ул. Проектная, 4

| Патент США № 3346844, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Выделитель комбинации цифровых сигналов | 1979 |

|

SU882029A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-04-07—Публикация

1984-03-07—Подача