Изобретение относится к связи и MOKet использоваться в устройствах обработки дискретных сообщений для обнаружения составных комбинаций двоичных сигналов, образованной 1 классами из п комбинаций известного вида при неизвестном моменте ее прихода .

Цель изобретения - расширение функциональных возможностей путем обеспечения обнаружения составной комбинации двоичных сигналов, образованной 1 классами из п комбинаций известного кода.

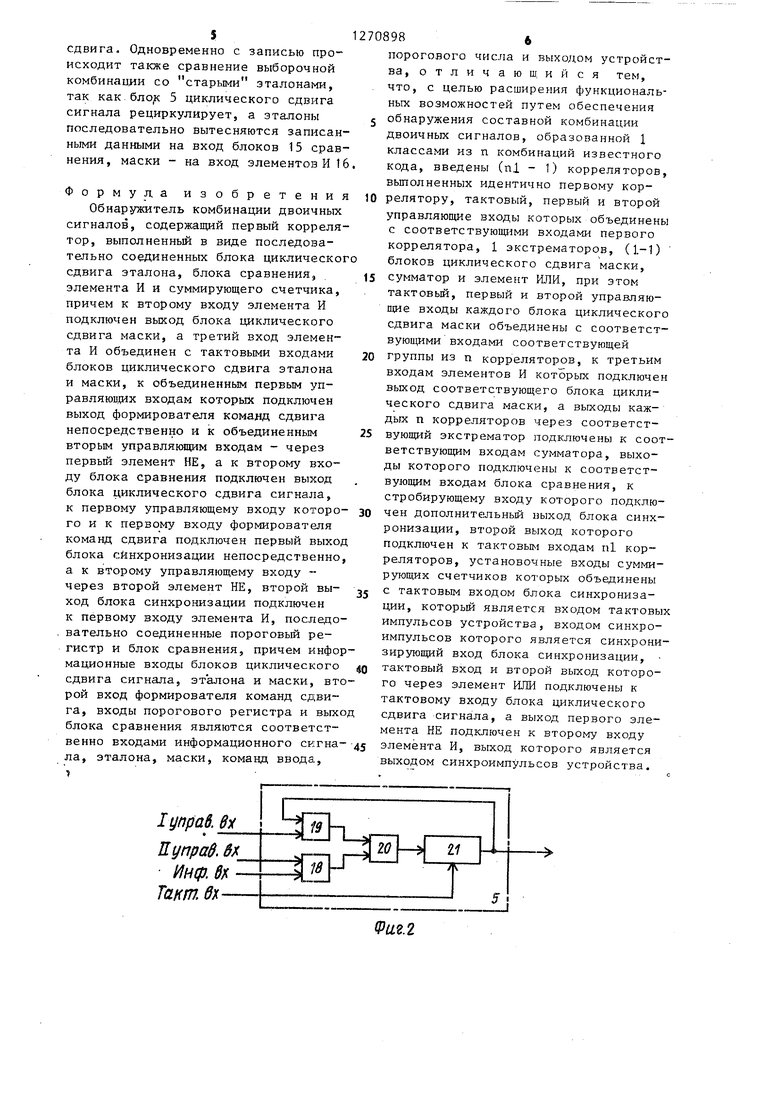

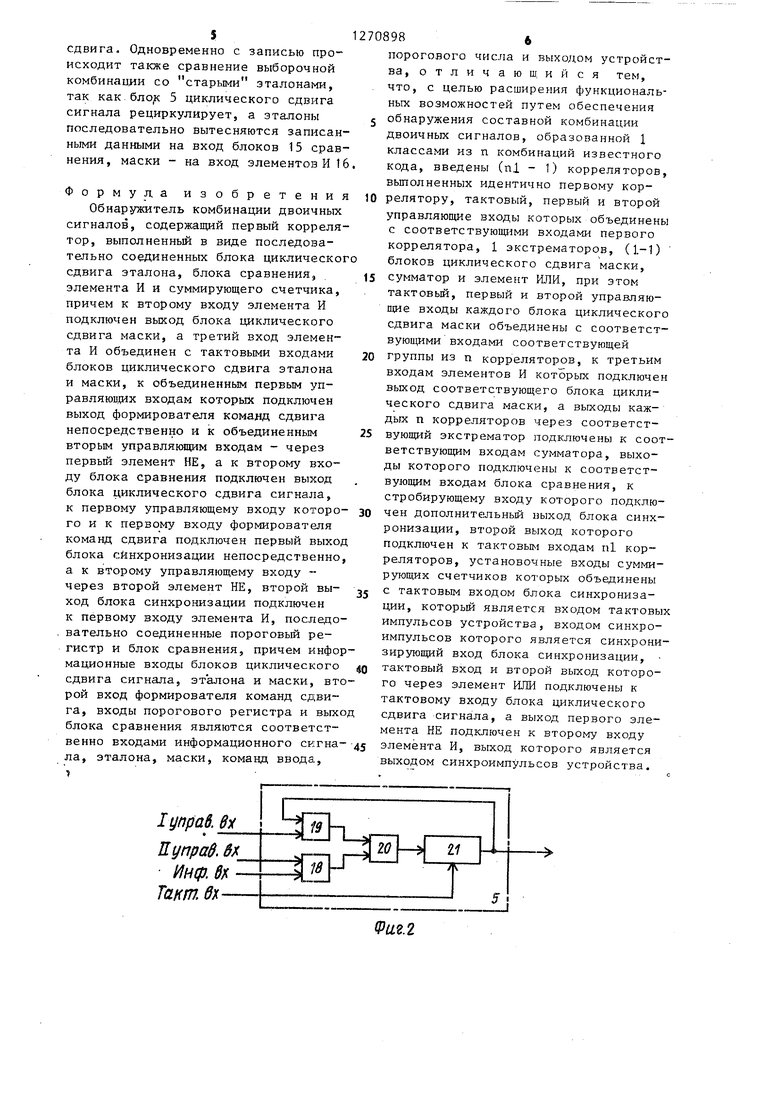

На фиг. 1 приведена структурная электрическая схема обнаружителя комбинацрш двоичных сигналов, на фиг.2вариант реализации блоков циклического сдвига сигнала, эталона и маски на фиг„ 3 - временные диаграммы, поясняющие работу обнаружителя комбинации двоичных сигналов.

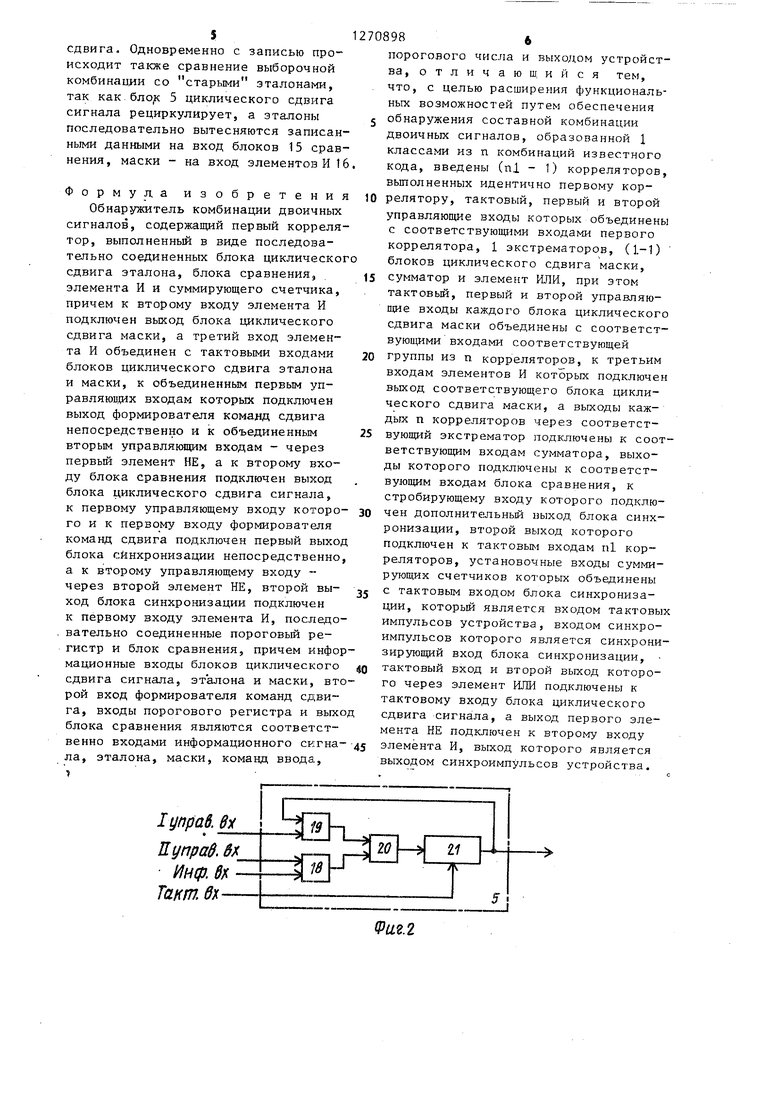

Обнару:китель комбинации двоичных сигналов содержит п1 корреляторов 1, - Inf, сумматор 2, блок 3 сравнения, пороговый регистр 4, блок 5 циклического сдвига сигнала, элемент ИЛИ 6, первый и второй элементы НЕ 7 и 8,элемент И 9,блок 10 синхронизахщи,формирователь 11 команд сдвига 1 экстрематоров 12j - 12р и 1 блоков циклического сдвига маски 13 -- 13, причем в состав каждого коррелятора входят блок 14 циклического сдвига эталона, блок 15 сравнения, элемент И 16 и суммирующий сч-етчик 17, а в состав блоков циклического сдвига сигнала, эталона и маски 5, 14 и 13 входят элементы И 18 И. 19, элемент ИЛР- 20 и регистр 21 сдвига.

Обнаружитель комбинации двоичных

сигналов работает следующим образом. I

Принимаемые двоичные сигналы в виде последовательности элементарных посылок 1 и О (фиг. За) поступает на информационный вход блока 5 циклического сдвига сигнала, на тактовый вход которого через элемент ИЛИ 6 поступают тактовые импульсы (фиг. 36)5 синхронизированные с двоичными сигналами. Каждый тактовый импульс сдвигает содержимое регистра 21 сдвига на один бит вправо и записывает в него принятый двоичньй сигнал через открытьй в это время элемент И 18 и элемент ИЛИ 20. В результате в каждом тактовом интервале (интервале между соседними тактовыми импульсами) N-разрядньм регистр 21 сдвига содержит выборочную комбинацию, образованную двоичными сигналами, принятыми в данном и в N-1 предыдущих тактовых интерналах (N - число двоичных сигналов в составной комбина1:1ии) « На фиг. 3 в, г показаны выборочные комбинации, содержащиеся в регистре сдвига 21 в К и (к+1)-м

тактовых интервалах,

N-разрядные регистры 21 сдвига в блоках циклического сдвига маски 13 и эталона 14 содержат маски и эталоны своего класса, при этом код маски указывает на и формационные позиции эталона (на информационных позициях разряды регистра 21 сдвига мас-кисодержат 1, на неинформационных позициях - О), Для примера на

фиг. 3 показано содержимое регистров 21 сдвига эталонов и маски в случае составной комбинации, образованной двумя классами: на фиг. Зд, е - эталоны первого класса; на фиг. Зж маска первого класса; на фиг. Зз,и эталоны второго класса; на фиг.Зк маска второго класса (знаком X обозначено безразличное состояние разряда регистра 21 сдвига). В общем случае

составная комбинапия образована 1 комбинациями, при этом каждый класс в составной комбинации представлен одной комбинацией, а комбинации классов следуют в строго определенной

,последоватапьности. В приведенном

примере первой по времени следует комбинация второго класса (фиг. За, б, в, ж, к).

Тактовые импульсы одновременно с

записью двоичного сигнала в блок 5 циклического сдвига сигнала устанавливают в О суммирующие счетчики 17 - и инициирует блок 10 синхронизации, который из синхроимпульсов, поступающих на синхронизирующий его вход, вырабатывает в тактовом интервале следующие управляющие на первом выходе - команду рециркуляции в сигнала логической 1, на втором выходе - пачку из N импульсов, на дополнитепьиом выходе - одиночньй импульс. Команда рециркуляции поступает jsa первый управляющий вход и через второй элемент НЕ 8 - на второй управляющ1-гй вход блока 5 циклического сдвига сигнала, открывает в нем элемент И 19 и закрывает элемент И 18 и переводит его в режим рециркуляции, при котором информационный вход запрещен, а выход регистра 2 Г соедине с его входом через элементы И 19 и ИЛИ 20. При отсутствии команд вво да на втором входе формирователь 11 команд сдвига формирует на выходе логическую 1, которая поступает непосредственно и через первый элемент НЕ 7 на первый и второй управляющие входы блоков циклического сдвига эталона 14.j - , и блоков циклического сдвига маски 13 - 13р и п-ереводит их в режим рециркуляции Импульсы пачки, поступающие со второго выхода блока 10 си гхронизации на тактовые входы блоков циклического сдвига маски и эталона 13, 13 и 14, - lAnl непосредственно и на тактовый вход блока 5 циклическо- 20 ния

го сдвига сигнала через элемент ИЛИ 6, осуществляют синхронньй циклический сдвиг (рециркуляцию) содержимого регистров 21 сдвига. При этом на выходе блока 5 циклического сдви- 25 га сигнала последовательно появляют ся биты выборочной комбинации, на выходе блоков 14 циклического сдвига эталона - биты эталонов, на выхо де блоков 13 циклического сдвига ма ки - биты маски. Блоки 15, - 15,J сравнения формируют на своем выходе сигнал логической 1 при совпадении и логического О при несовпадении сравниваемых битов выборочной комбинации и эталонов. Результаты сравнения стробируются импульсами пачки на-выход элементов И. 16 - 16,, которые блокируют поступление результатов сравнения на вход суммирующих счетчиков 17, - 17 при появлении на выходе блоков циклического сдвига маски 13 - 13 бита О, соответствующего неинформахщонной позиции. По окончании пачки выборочная комбинация, эталоны и маски займут исходное положение в регистрах 21 сдви га блоков циклического сдвига сигна- эталона и маски 5, 14 - 14f, ,и 13, - 13, , а суммирующие счетчики 17, - 17,, будут содержать число совпадений двоичных сигналов выборочной комбинации и соответствующих эталонов на информационных позициях (корреляционное число). Полученные описанным образом корреляционные числа в каждой группе из п корреляторов 1 являются мерой

составной комбинации, который считывается на выход устройства одиночным импульсом, поступающим на стробирующ1-ш вход блока 3 сравнения с допол984совпадения выборочной комбина1Ц1и с эталонами данного класса. Коды корреляционных чисел с выходов суммирующих счетчиков 15 - 15„ поступают на входы экстрематора 12, который выделяет максимальное число, соответствующее наилучшему совпадению выборочной комбинации с классом комбинаций. Корреляционные коды с выходов экстрематоров 12 -12 поступают на входы сумматора 2, на выходе которого формируется корреляционное число, равное числу совпадений двоичных сигналов выборочной комбинации и составной комбинации на информационных позициях. Если это число не меньше порогового числа, содержащегося в пороговом регистре 4, блок 3 сравнеформирует сигнал обнаружения нительного выхода блока 10 синхронизации. Аналогичным образом протекают процессы обнаружения в каждом тактовом интервале. Для ввода эталонов и маски на соответствующий вход устройства поступает команда ввода, запускающая формирователь 11 команд сдвига, который выделяет одиночную инвертированную команду рециркуляции из последовательности команд рециркуляции, поступающей на его первый вход с первого выхода блока 10 синхронизации. Инвертированная команда рециркуляции с выхода формирователя 11 команд сдвига проходит через первый элемент НЕ 7 и открывает элемент И 9, а такл ;е непосредственно и через первый элемент НЕ 7 поступает на первый и второй управляющие, входы блоков циклического сдвига маски и эталона 13 - 13р и 14 - 14f,p, в которых открывает элемент И 18 и закрывает элемент И 19. Импульсы пачки со вто , . синхронизации проходят через элемент И 9 на выход устройства, считывают биты эталонов и масок из внешних регистров (не показаны), которые поступают на информационные входы блоков циклического сдвига маски и эталона 13 и 14 соответственно и записываются в соответствующие регистры 21 сдвига. Одновременно с записью происходит также сравнение выборочной комбинацией со старыми эталона1 №, так как. 5 циклического сдвига сигнала рециркулирует, а эталоны последовательно вытесняются записанными данными на вход блоков 15 сравнения, маски - на вход элементов И 16 Формула изобретения Обнаружитель комбинации двоичных сигналов, содержащий первый коррелятор, выполненный в виде последовательно соединенных блока циклическог сдвига эталона, блока сравнения, элемента И и суммирующего счетчика, причем к второму входу элемента И подключен выход блока циклического сдвига маски, а третий вход элемента И объединен с тактовыми входами блоков циклического сдвига эталона и маски, к объединенным первым управляюдах входам которых подключен выход формирователя команд сдвига непосредственно и к объединенным вторым управляющим входам - через первый элемент НЕ, а к второму входу блока сравнения подключен выход блока циклического сдвига сигнала, к первому управляющему входу которо го и к первому входу формироват(У1я команд сдвига подключен первый выхо блока синхронизации непосредственно а к второму управляющему входу через второй элемент НЕ, второй выход блока синхронизации подключены к первому входу элемента И, последо . вательно соединенные пороговьм регистр и блок сравнения, причем инфо мационные входы блоков циклического сдвига сигнала, эталона и маски, вт рой вход формирователя команд сдвига, входы порогового регистра и вых блока сравнения являются соответственно входами информационного сигна ла, эталона, маски, команд ввода. порогового числа и выходом устройства, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения обнаружения составной комбинации двоичных сигналов, образованной 1 классами из п комбинаций известного кода, введены (п1 - 1) корреляторов, выполненных идентично первому коррелятору, тактовый, первый и второй управляющие входы которых объединены с соответствующими входами первого коррелятора, . экстрематоров, (1.-1) блоков циклического сдвига маски, сумматор и элемент ИЛИ, при этом тактовьй, первый и второй управляющие входы каждого блока циклического сдвига маски объединены с соответствующими входами соответствующей группы из п корреляторов, к третьим входам элементов И которых подключен выход соответствующего блока циклического сдвига маски, а выходы каждых п корреляторов через соответствующий экстрематор подключены к соответствующим входам сумматора, выходы которого подключены к соответствующим входам блока сравнения, к стробирующему входу которого подключен дополнитешьньй ныход блока синхронизации, второй выход которого подключен к тактовым входам п1 корреляторов, установочные входы суммирующих счетчиков которых объединены с тактовым входом блока синхронизации, которьм является входом тактовых импульсов устройства, входом синхроимпульсов которого является синхронизирующий вход блока синхронизации, тактовый вход и второй выход которого через элемент ИЛИ подключены к тактовому входу блока циклического сдвига сигнала, а выход первого элемента НЕ подключен к второму входу элемента И, выход которого является выходом синхроимпульсов устройства.

Выборочная комЗинация 6 монент t

Выборочная комбинацая 6 момент t

00110001 0011- 10 101000 1 01 1 1 г 1 а.) . . . П . I . . . I П П , . П I . . . . I

у I I I I I I I I I I I I И I I I i I I I И I I I I I I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство классификации N-разрядных двоичных комбинаций | 1982 |

|

SU1089576A1 |

| Устройство классификации @ -разрядных двоичных комбинаций | 1983 |

|

SU1087985A1 |

| Выделитель составной комбинации двоичных сигналов | 1984 |

|

SU1223411A1 |

| Обнаружитель комбинаций двоичных сигналов | 1986 |

|

SU1356266A1 |

| Выделитель комбинации цифровых сигналов | 1979 |

|

SU882029A1 |

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Устройство приема двоичных сигналов | 1984 |

|

SU1197116A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

/) ./ . .

Вход..

г)

я Вход .„Rhijfnff

J±: LiiJi- jOinoiy|o|g|/|g|x{xlxlxlxlxlxlxixlxixixixixix x1-

e) od

mg77Tn gTfixlx|xixix|x x|xlxfxlxlx|xlx|xrx

ж) 5)(0д Bkiynd () bi(Qd ,,,,,.,,,., -r-T-1 , , . . . 1 . , , , , g

jy.± lJ i- rxixlxlxlxixl7 xi/ig|gTgTg|f|/HI/l(7lf|gin/lffg1

Ькод... Bhiicnd

u) -g i xixixlxixlxixlxl/m f fiPigi/|g| I HIPtg| yi/l

Входfihfjffj/

Kj 1 1 i 1 1 i Выкод

.г.3

| Патент США № 4227175, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Выделитель комбинации цифровых сигналов | 1979 |

|

SU882029A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-11-15—Публикация

1983-05-18—Подача