регистр 1, а в триггер 10 через вход 22 записывается код «1. Выходы регистров 1 и 2 соединены с входами схемы 7, которая является комбинационной. Она предназначена для формирования (я+1) старших разрядов очередкого частичного произведения на основе суммирования л старших разрядов предыдуш,его частичного произведения с сомножителем, если в триггере 10 заиисана «1, или с нулем, если в триггере 10 записан «О.

Так как в первом блоке в регистре 2 записан код «О, а в триггере 10 код «1, то на выходах схемы 7, определяюш.их младшие п разрядов, повторяется значение кода регистра 1. Выход схемы 7, о:пределяюш,ий значение младшего разряда сомножителя, соединен с входом управляюш,его триггера 10, а выходы схемы 7, определяющие старшие п разрядов, соединены с входами регистра 4 п старших разрядов частичного произведения. Таким образом, в следуюш,ем такте на регистр 4 второго блока записывается код сомножителя, сдвинутый на один разряд вправо, а в триггер 10 того же первого - блока записывается код младшего разряда того же сомножителя. Кроме того, в следуюш.ем такте код .первого сомножителя перепишется в регистр 3 второго блока, а на регистр 1 первого блока запишется код нового сомножителя. Таким образом, во втором также на выходах схемы 7 появится первое частичное произведение, определяемое состоянием триггера 10, т. е. на выходах схемы 7 может появиться либо код множимого, либо «О.

Так как в триггере -12 второго блока записан код «О, то передача множителя на схему 8 запрещена, и, следовательно, на выходах схемы 8 появится код, повторяюший код, записанный в регистр 4, т. е. сдвинутый на один разряд код первого сомножителя.

В третьем такте выполняются следующие преобразования.

На регистр 3 второго блока записывается код второго сомножителя, а код первого сомножителя с регистра 3 переписывается на регистр 5 третьего блока. В триггер 12 записывается вторая младшая -цифра первого сомножителя. На регистр 4 второго блока записываются старшие п разрядов первого частичного произведения, т. е. практически реализуется сдвиг частичного произведения вправо на один разряд, а выдвинутый младший разряд данного частичного произведения записывается в управляющий триггер 10 первого блока. Так как код данного разряда произведения является окончательным, то он может быть сразу использован для умножения искомого произведения двух первых сомножителей на следующий третий сомножитель последовательности. Поэтому в рассматриваемом такте на регистр 1 первого блока принимается новый, третий сомножитель. На основе содержимого триггера 10 и кода в регистре 1 на выходе схемы 7 появится первое частичное произведение от умножения трех сомножителей, причем младший разряд этого произведения

использовать на следующем такте для умножения на следующий сомножитель последовательности чисел, и так далее.

На основе кода, записанного в триггере 12, и кодов, записанных в регистрах 3 и 4, на выходах комбинационной схемы 8 появится второе частичное произведение, причем младший разряд данного частичного произведения является окончательным и определяет вторую цифру произведения двух первых сомножителей, код которого запишется в триггер 12 и будет использован на следующем такте для умножения на третий сомножитель и т. д.

Если необходимо перемножить / чисел, то для этой цели необходимо использовать () уровпей (где р - величина, зависящая от точности представления результата). Если, например, необходимо получить /fen-разрядное произведение, то р должно быть равно (й+1).

Точность представления определяется состоянием триггеров 11, 13, 15, которые устанавливаются извне через вход 23. Если, например, в триггеры 11, 13, 15 записан код «1, то состояние триггеров 10, 12, 14 переписываются через схемы «И 16, 17 и 18 в старшие разряды регистров 4, 6 и т. д.

Как отмечалось ранее, коды этих регистров сдвигаются на каждом такте на один разряд вправо и, таким образом, к моменту окончания умножения оказываются на требуемой позиции.

Таким Образом, для получения -разрядной точности произведения необходимо иметь k регистров 2, 4, 6, т. е. для формирования результата необходимо использовать k блоков. Это означает, что после приема последнего /-го сомножителя, в каждом (/+s)-M такте (где s 1, 2, ..., k-1) в триггер 11 следует записывать «1.

Полное произведение последовательности из / чисел формируется за l-r(k-1)« тактов (где п - разрядность чисел).

В (/+)-м такте можно принимать новую последовательность чисел для перемножения. Следовательно, основное преимущество конвейернбго принципа обработки информации, заключающееся в эффективном использовании аппаратуры многорегистровых устройств, в данном случае сохраняется.

С помощью предлагаемого устройства наряду с умножением последовательности чисел возможно выполнение суммирования последовательности чисел, сдвига чисел, а также вычисление полинома типа P(Xi, Xz, ..., Хп) апл: 4-й п 1Х --1+-. . ао и некоторые другие операции.

Предмет изобретения

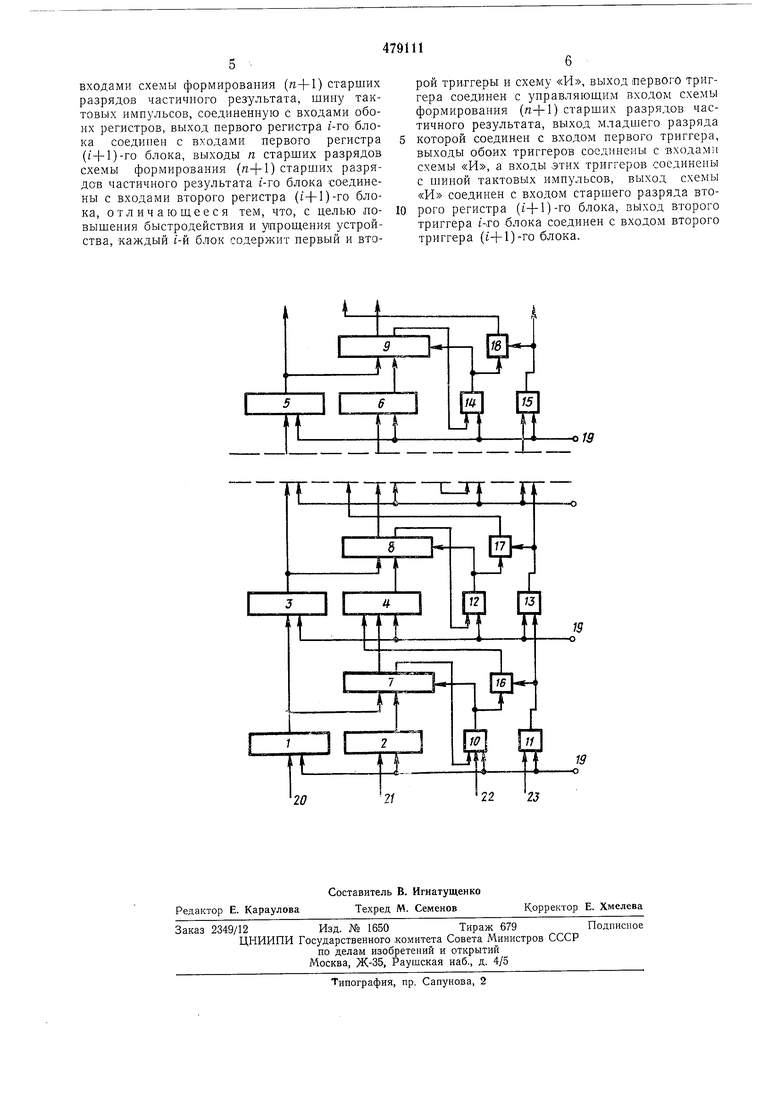

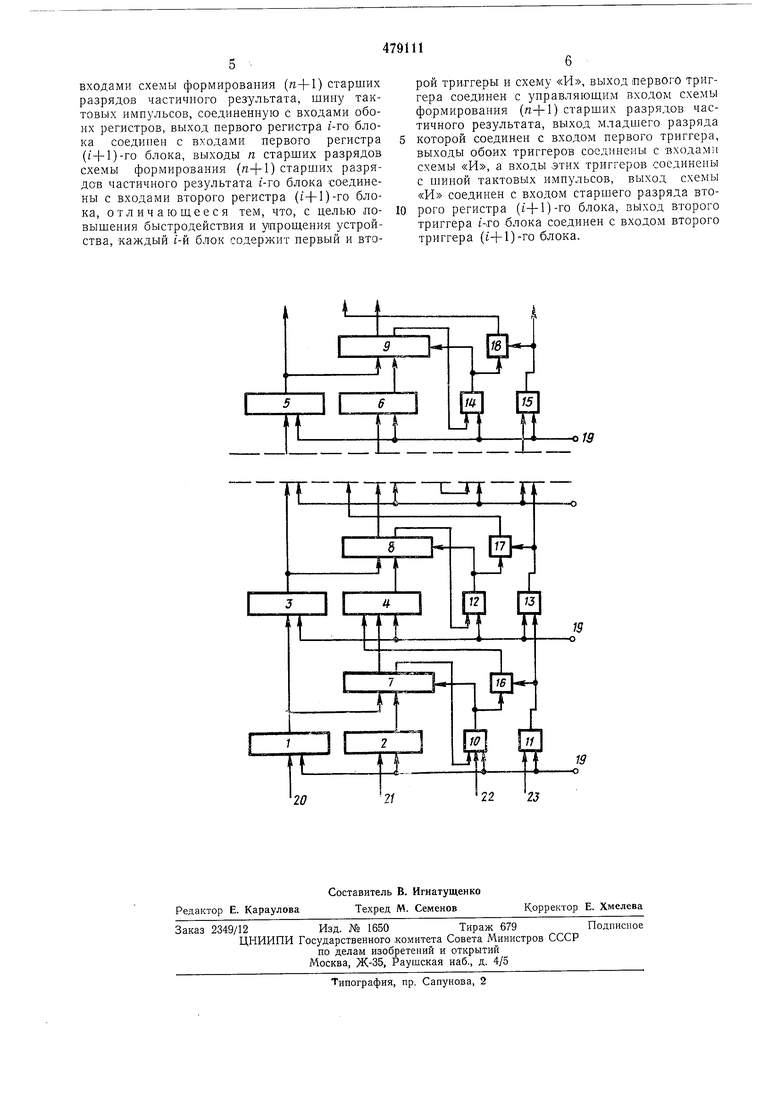

Устройство для одновременного выполнения арифметических операций над множеством чисел, выполненное из однотипных блоков, причем каждый i-й блок содержит первый и второй регистры, выходы которых соединены с

входами схемы формирования (га+1) старших разрядов частичного результата, шину тактовых импульсов, соединенную с входами обоих регистров, выход первого регистра i-ro блока соединен с входами первого регистра (i + l)-ro блока, выходы п старших разрядов схемы формирования {п-{-) старших разрядов частичного результата i-ro блока соединены с входами второго регистра (f+l)-ro блока, отличающееся тем, что, с целью повышения быстродействия и у1нрош,ения устройства, каждый f-й блок содержит первый и второй триггеры и схему «И, выход первого триггера соединен с управляющим входом схемы формирования («+) старших разрядов частичного результата, выход младшего разряда которой соединен с входом первого триггера, выходы обоих триггеров соединены с входами схемы «И, а входы этих триггеров соединены с шиной тактовых импульсов, выход схемы «И соединен с входом старшего разряда второго регистра (t+l)-ro блока, выход второго триггера 1-го блока соединен с входом второго триггера (t+1)-го блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| Конвейерное устройство для одновременного выполнения арифметических операций над множеством чисел | 1977 |

|

SU922726A1 |

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Арифметическое устройство | 1976 |

|

SU656059A1 |

| Устройство для вычисления сумм произведений | 1988 |

|

SU1569826A1 |

| Устройство для умножения | 1981 |

|

SU1035601A2 |

| Последовательное множительное устройство | 1981 |

|

SU987620A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

Авторы

Даты

1975-07-30—Публикация

1973-07-19—Подача