20

25

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных устройств для выполнения операций умножения, деления, извлечения квад- ратного корня при обработке массивов многоразрядных чисел.

Цель изобретения - сокращение затрат оборудования.

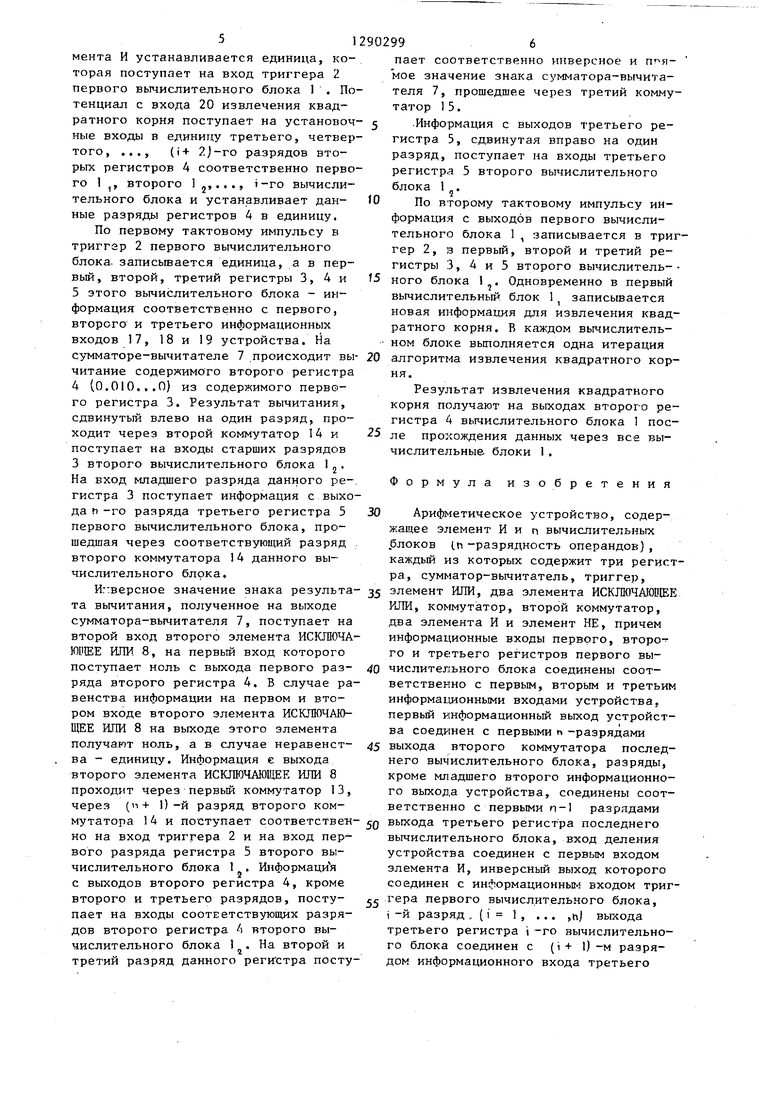

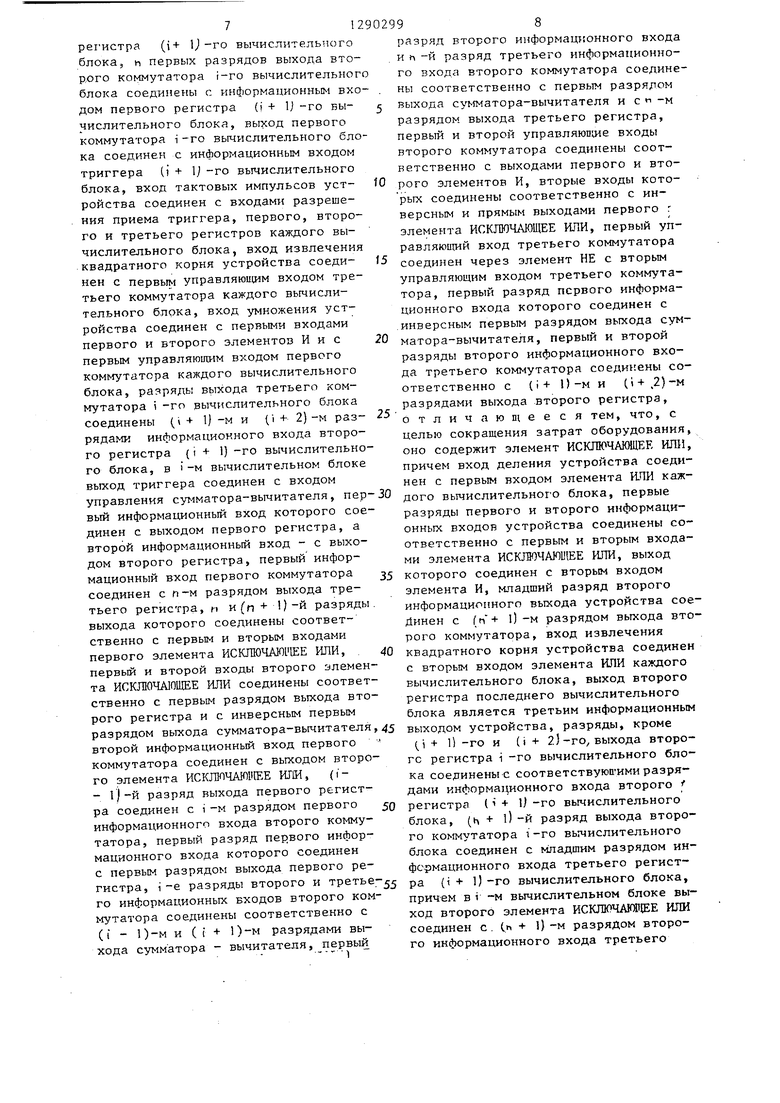

На чертеже представлена схема 0 арифметического устройства.

Арифметическое устройство содержит вычислительные блоки 1, каждый вычислительный блок 1 содержит триггер 2, первый, второй и третий ре- 55 гистры 3, А и 5, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, сумматор-вычитатель 7, второй элемент ИСКЛЮЧА 01ЧЕЕ 8, первь й и второй элементы И 9 и 10, элемент ИЛИ 11, элемент НЕ 12,, первый, второй и третий коммутатора 13, 14 и 15, вход 16 тактовых импульсов устройства, первь Й, второй и третий информационные входы 17, 18 и 19 устройства, вход 20 извлечения квадратного корня устройства, вход 21 умножения устройства, вход 22 деления устройства, элемент ИСКЛЮЧАЮЩЕЕ IdHM 23, элемент И 24, первый, второй и третий информационные выходы 25, 26 30 и 27 устройства.

Арифметическое устройство работает следуьощим образом.

В исходном состоянии информационные 17, 18 и 19 и управляющие 20, 21 3.5 и 22 входы находятся в нуле.

При операции умножения на вход 21 умножения подается единичный потенциал, а на входы 20 и 22 извлечения 40 квадратного корня и деления - нулевой потенциал.

Множимое и множитель потупают соответственно на второй и третий ин- 45 формационные входы 18 и 19 устройства, а на первый информационный вход I 7 устройства при этом пос 1 упает нулевой потенциал.

На третий управляющий вход комму- 50 татора 14 с выхода элемента ИЛИ 11 по поступает нулевой потенциал.

По первому тактовому импульсу в триггер 2 первого вычислительного блока 1, записывается единица, а в пер- 55 умножения. В каждом вычислительном

задает сумматору-вычислителю 7 опер цию вычитание.

Значения п-го и (п 1)-го разря дов множителя поступают на входы эл мента ИСКЛЮЧАЮЩЕЕ ИЛИ 6, на прямом и инверсном выходах которого формир ются соответственно единичные сигна лы при неравенстве указанных разрядов.

Инфюрмация с выходов элемента ИС КЛЮЧАК№Е ИЛИ 6 проходит через элем ты И 9 и 10 и поступает на первый и второй управляющие входы коммутатора 14.

В зависимости от значений на пер вом и втором управляющих входах на выход коммутатора 14 передается сдв нутая на один разряд информация с в хода регистра 3 или сумматора-вьтчит теля 7„

Информация с выхода второго комм татора i 4 первого вычислительного б ка 1 поступает на вход первого регистра 3 ((пстарших разрядов) и на вход, первого разряда третьего реги ра 5 (( п + 1) -и разряд) второго вычислительного блока 1 ,

На остальные входы третьего реги ра 5 второго вычислительного блока W

поступает множитель С третьего реги ра 5, сдвинутый вправо на один разряд. Значение h-го разряда множител проходит через первый коммутатор 13 и поступает на информационный вход триггера 2 второго вычислительного блока 1 . Множимое с выходов второг регистра 4, кроме второго и третьег разрядов, поступает на входы соотве ствующих разрядов второго регистра второго вычислительного блока 1.

Второй и третий разряд множимог проходит через третий коммутатор 1 на входы второго и третьего разрядо второго регистра второго вычислител ного блока 1.

По второму тактовому импульсу инфор мация с выходов первого вычислитель ного блока 1 записывается в тригге

2,в первый, второй, третий регистр

3,4 и 3 второго вычислительного бл ка Ц. Одновременно в первый вычисл тельньй блок 1, записывается новая информация для вьпюлнения операции

вый, второй и третий регистры 3, 4 и 5 этого же вычислительного блока - соответственно Нуль, множимое и житель. Сигнал с выхода триггера 2

0

5

0

5 0

.5

0

5

0

5 умножения. В каждом вычислительном

задает сумматору-вычислителю 7 операцию вычитание.

Значения п-го и (п 1)-го разрядов множителя поступают на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6, на прямом и инверсном выходах которого формируются соответственно единичные сигналы при неравенстве указанных разрядов.

Инфюрмация с выходов элемента ИС- КЛЮЧАК№Е ИЛИ 6 проходит через элементы И 9 и 10 и поступает на первый и второй управляющие входы коммутатора 14.

В зависимости от значений на первом и втором управляющих входах на выход коммутатора 14 передается сдвинутая на один разряд информация с выхода регистра 3 или сумматора-вьтчита- теля 7„

Информация с выхода второго коммутатора i 4 первого вычислительного блока 1 поступает на вход первого регистра 3 ((пстарших разрядов) и на вход, первого разряда третьего регистра 5 (( п + 1) -и разряд) второго вычислительного блока 1 ,

На остальные входы третьего регистра 5 второго вычислительного блока 1 W5

поступает множитель С третьего регистра 5, сдвинутый вправо на один разряд. Значение h-го разряда множителя проходит через первый коммутатор 13 и поступает на информационный вход триггера 2 второго вычислительного блока 1 . Множимое с выходов второго регистра 4, кроме второго и третьего разрядов, поступает на входы соответствующих разрядов второго регистра 4 второго вычислительного блока 1.

Второй и третий разряд множимого проходит через третий коммутатор 15 на входы второго и третьего разрядов второго регистра второго вычислительного блока 1.

По второму тактовому импульсу информация с выходов первого вычислительного блока 1 записывается в триггер

2,в первый, второй, третий регистры

3,4 и 3 второго вычислительного блока Ц. Одновременно в первый вычисли- тельньй блок 1, записывается новая информация для вьпюлнения операции

блоке выполняется одна интеграция алгоритма умножения. Результат умножения с з двоенной точностью снимается с выходов второго коммутатора 14 и с

третьего регистра 5 вычислительного блока Ij .

При операции деления на вход, 22 деления подается единичный .потенциал а на входы 20 и 21 извлечения квадратного корня и умножения - нулевой потенциал. ,

Старшие разряды делимого (первое полуслово) поступают на первый вход 17 устройства, а его младшие разряды (второе полуслово) поступают на третий информационный вход 19 устройства, причем младший разряд второго полуслова поступает на вход первого разряда этого информационного входа. Делитель поступает на второй информационный вход 18 устройства.

Знаковые разряды делимого и делителя поступают на входы элемента ИСКЛК1ЧАЮЩЕЕ ИЛИ 23| сигнал с выхода ко-20 мутатор 15 и поступает на входы соотторого проходит через элемент И 24 и при равенстве 3 знаков устанавливает триггер 2 первого вычислительного блока в единицу.

По первому тактов ому импульсу ин- 25 тельного блока 1 записывается в тригформация с информационных входов 17, 18 и 19 устройства записывается соответственно в регистры 3, 4 и 5 первого вычислительного блока 1,, сумма- тор-вычитатель 7 которого выполняет 30 вычитание или суммирование при соответственно единичном или нулевом значении триггера 2.

Инверсное значение знака результата, полученное на выходе сумматора- 5 вычитателя 7, поступает на второй вход второго элемента ИСКЛЮЧАЮЩЕЕ РШИ В, на первый вход которого поступает знак делителя.

В случае равенства информации на 0 первом и втором входе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 на выходе этого элемента получаем ноль, а в случае неравенства - единицу. Информация с выхода второго элемента ИСКЛЮЧАЮЩЕЕ 5 ИЛИ 8 проходит через первый коммутатор 13 и поступает на вход триггера 2 второго вычислительного блока ,

гер 2, в первый, второй и третий регистры 3, 4 и 5 второго вычислительного блока 1,. Одновременно в первый вычислительный блок t записывается новая информация для выполнения операции деления. В вычислительном блоке выполняется одна интерация алгоритма деления. Результат деления С гимают с выходов ( h - ) -го разрядов третьего регистра 5 и (h + 1) -го разряда второго коммутатора 14 вычислительного блока 1, причем янформа- ция на выходе (и- 1) -го разряда третьего регистра 5 является знаком результата, а информация на выходе

(h+ 1)-го разряда второго коммутатора - младшим разрядом после прохождения даннь(х через все вычислительные блоки 1.

При извлечении квадратного корня на вход 20 подается единичный потенциал, а на входы 21 и 22 умножения и деления - нулевой потенциал- Старшие

Информация из вьщодов сумматора- вычитателя 7, сдвинутая влево на один разряд, проходит через второй коммутатор 14 и поступает на входы старших разрядов первого регистра 3 второго вычислительного блока.

На вход младшего разряда данного регистра 3 поступает информация с выхода h-го разряда третьего регистра 5 первого вычислительного блока, прогпедшая через соответствующий разряд второго коммутатора 14 данного вычислительного блока. Информация с выхода (+ ) -го разряда второго коммутатора 14 (знак частного} поступает на вход первого разряда третьего регистра 5 второго вычислительного блока 1j. На входы остальных разрядов данного регистра 5 поступает информация с выходов третьего регистра 5 первого вычислительного блока 1,, сдвинутая вправо на один разряд. Делитель с выхода второго регистра 4, кроме второго и третьего разрядов, поступает на входы соответствующих разрядов второго регистра 4 вычислительного блока 1, Информация с выходов второго и третьего разрядов второго регистра 4 проходит через третий комветствующих разрядов второго регистра 4 второго вычислительного блока 1 .

По второму тактовому импульсу информация с выходов первого вьсчислигер 2, в первый, второй и третий регистры 3, 4 и 5 второго вычислительного блока 1,. Одновременно в первый вычислительный блок t записывается новая информация для выполнения операции деления. В вычислительном блоке выполняется одна интерация алгоритма деления. Результат деления С гимают с выходов ( h - ) -го разрядов третьего регистра 5 и (h + 1) -го разряда второго коммутатора 14 вычислительного блока 1, причем янформа- ция на выходе (и- 1) -го разряда третьего регистра 5 является знаком результата, а информация на выходе

(h+ 1)-го разряда второго коммутатора - младшим разрядом после прохождения даннь(х через все вычислительные блоки 1.

При извлечении квадратного корня на вход 20 подается единичный потенциал, а на входы 21 и 22 умножения и деления - нулевой потенциал- Старшие

разряды подкоренного числа (первое поуслово) поступают на первый информационный вход 17 устройства, младшие разряды (второе полуслово) - на третий информационный вход 19 устройства,

ричем младший разряд второго полуслова поступает на вход первого разряда этого информационного входа. На второй информационный вход 18 устройства поступает ноль. На выходе эле51

мента И устанавливается единица, которая поступает на вход триггера 2 первого вычислительного блока 1 . Потенциал с входа 20 извлечения квадратного корня поступает на установочные входы в единицу третьего, четвертого, ..., ( 2)-го разрядов вторых регистров 4 соответственно первого , второго 1 j,..., i-ro вычислительного блока и устанавливает данные разряды регистров 4 в единицу.

По первому тактовому импульсу в триггер 2 первого вычислительного блока, записывается единица, а в вый, второй, третий регистры 3, 4 и 5 этого вычислительного блока - информация соответственно с первого, второго и третьего информационных входов 17, 18 и 19 устройства. На сумматоре-вычитателе 7 происходит вычитание содержимого второго регистра 4 (0.010,..П) из содержимого первого регистра 3. Результат вычитания, сдвинутый влево на один разряд, проходит через второй коммутатор 14 и поступает на входы старших разрядов 3 второго вычислительного блока 1. На вход младшего разряда данного регистра 3 поступает информация с выхода h-го разряда третьего регистра 5 первого вычислительного блока, прошедшая через соответствующий разряд второго коммутатора 14 данного вычислительного блока.

И::версное значение знака результата вычитания, полученное на выходе сумматора-вычитателя 7, поступает на второй вход второго элемента ИСКШОЧА- Ю1ЧЕЕ ИЛИ 8, на первый вход которого поступает ноль с выхода первого разряда второго регистра 4. В случае равенства информации на первом и втором входе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 на выходе этого элемента получают ноль, а в случае неравенства - единицу. Информация е выхода второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 проходит через первый коммутатор 13, через (ч+ 1)-и разряд второго коммутатора 14 и поступает соответственно на вход триггера 2 и на вход первого разряда регистра 5 второго вычислительного блока 1 . Информаци я с выходов второго регистра 4, кроме второго и третьего разрядов, поступает на входы соответствующих разрядов второго регистра А второго вычислительного блока 1,. На второй и третий разряд данного регистра посту

902996

пает соответственно инверсное и мое значение знака сумматора-вычитателя 7, прошедшее через третий коммутатор 1 5.

5 .Информация с выходов третьего регистра 5, сдвинутая вправо на один разряд, поступает на входы третьего регистра 5 второго вычислительного блока 1 .

10 По второму тактовому импульсу информация с выходов первого вычислительного блока 1 , записывается в триггер 2, 3 первый, второй и третий регистры 3, 4 и 5 второго вычислитель-

5 ного блока 1 . Одновременно в первый вычислительный блок 1 записывается новая информация для извлечения квадратного корня. В каждом вычислитель- - ном блоке выполняется одна итерация

20 алгоритма извлечения квадратного корня.

Результат извлечения квадратного корня получают на выходах второго регистра 4 вычислительного блока 1 пос- ле прохождения данных через все вычислительные блоки 1.

Формула изобретения

30 Арифметическое устройство, содержащее элемент И и п вычислительных блоков {.п -разрядность операндов , каждый из которых содержит три регистра, сумматор-вычитатель, триггер,

35 элемент ИЛИ, два элемента ИСКЛЮЧАЮИЩЕ

ИЛИ, коммутатор, второй коммутатор, два элемента И и элемент НЕ, причем информационные входы первого, второго и третьего регистров первого вы40 числительного блока соединены соответственно с первым, вторым и третьим информационными входами устройства, первый информационный выход устройства соединен с первыми п-разрядами

45 выхода второго коммутатора последнего вычислительного блока, разряды, кроме младшего второго информационного выхода устройства, соединены соответственно с первыми п-1 разрядами

50 выхода третьего регистра последнего

вычислительного блока, вход деления устройства соединен с первым входом элемента И, инверсный выход которого соединен с информационны входом триг- гг гера первого вычислительного блока, i -и разряд , (1 1 , ... , выхода третьего регистра i-го вычислительного блока соединен с (i+ 1) -м разрядом информационного входа третьего

регистра (i+ Ij-го вычислительного блока, h первых разрядов выхода второго коммутатора i-ro вычислительног блока соединены с информационным входом первого регистра (i + Ij -го вычислительного блока, выход первого коммутатора i-го вычислительного блока соединен с информационным входом триггера (i + Ij -го вычислительного блока, вход тактовых импульсов устройства соединен с входами разрешения приема триггера, первого, второго и третьего регистров каждого вычислительного блока, вход извлечения квадратного корня устройства соединен с первым управляюц им входом третьего коммутатора каждого вычислительного блока, вход умножения устройства соединен с первыми входами первого и второго элементов И и с первым управляющим входом первого коммутатора каждого вычислительного блока, разряды выхода третьего коммутатора i -го вычислительного блока соединены ( 1} -м и (i + 2) -м разрядами информационного входа второго регистра {i + 1) -го вычислительного блока, в i-м вычислительном блоке

разряд второго информационного входа и п-и разряд третьего информационного входа второго коммутатора соедине ны соответственно с первьгм разрядом выхода сумматора-вычитателя и с « -м разрядом выхода третьего регистра, первый и второй управляюпще входы второго коммутатора соединены соответственно с выходами первого и второго элементов И, вторые входы которых соединены соответственно с инверсным и прямым вь ходами первого г элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый управляющий вход третьего коммутатора 5 соединен через элемент НЕ с вторым управляющим входом третьего коммутатора, первый разряд первого информационного входа которого соединен с инверсным первым разрядом выхода сумматора-вычитателя, первый и второй разряды второго информационного входа третьего коммутатора соединены соответственно с (i+ 1)-м и (1+,2)-м разрядами выхода второго регистра, отличающееся тем, что, с целью сокращения затрат оборудования, оно содержит элемент ИСКЛЮЧАЩЕЕ ИЛИ, причем вход деления устройства соединен с первым входом элемента КПИ кажвыход триггера соединен с входом

управления сумматора-вычитателя, пер-30 дого вычислительного блока, первые вый информационный вход которого сое- разряды первого и второго информаци- динен с выходом первого регистра, а второй информационный вход - с выходом второго регистра, первый информационный вход первого коммутатора соединен с п-м разрядом выхода третьего регистра, и и(п + 1)й разряды, выхода которого соединены соответственно с первым и вторым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, о первый и второй входы второго элемента ИСКЛЮЧА10ЩЕЕ ИЛИ соединены соответственно с первым разрядом выхода второго регистра и с инверсным первым разрядом выхода сумматора-вычитателя,45 выходом устройства, разряды, кроме второй информационный вход первого (i + 1) -го и (i + 2/-го, выхода вторс- коммутатора соединен с выходом второго элемента ИСКЛЮЧАЮ111ЕЕ ИЛИ, (iонных входов устройства соединены соответственно с первым и вторым входами элемента ИСКЛОЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом элемента И, младщий разряд второго информационного выхода устройства сое динен с (п + 1)-м разрядом выхода вто рого коммутатора, вход извлечения квадратного корня устройства соединен с вторым входом элемента ИЛИ каждого вычислительного блока, выход второго регистра последнего вычислительного блока является третьим информационным

го регистра i -го вычислительного блока соединены с соответствуюшими разрядами информационного входа второго f регистра ( + }) -го вычислительного блока, (h + l) -и разряд выхода второго коммутатора т-го вьмислительного блока соединен с младшим разрядом информационного входа третьего регист- Г)-и разряд выхода первого регистра соединен с i-м разрядом первого информационного входа второго коммутатора, первый разряд первого информационного входа которого соединен с первым разрядом выхода первого регистра, i -е разряды второго и третье-«;5 ра {i + 1) -го вычислительного блока, го информационных входов второго ком- причем в i -м вычислительном блоке вы- мутатора соединены соответственно с (i - 1)-м и ( i + 1)-м разрядами выход второго элемента ИСКЛЮЧАКЯЦЕЕ ИЛИ соединен с. (.п + 1)-м разрядом второго информационного входа третьего

хода сумматора - вычитателя,первый

разряд второго информационного входа и п-и разряд третьего информационного входа второго коммутатора соединены соответственно с первьгм разрядом выхода сумматора-вычитателя и с « -м разрядом выхода третьего регистра, первый и второй управляюпще входы второго коммутатора соединены соответственно с выходами первого и второго элементов И, вторые входы которых соединены соответственно с инверсным и прямым вь ходами первого г элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый управляющий вход третьего коммутатора соединен через элемент НЕ с вторым управляющим входом третьего коммутатора, первый разряд первого информационного входа которого соединен с инверсным первым разрядом выхода сумматора-вычитателя, первый и второй разряды второго информационного входа третьего коммутатора соединены соответственно с (i+ 1)-м и (1+,2)-м разрядами выхода второго регистра, отличающееся тем, что, с целью сокращения затрат оборудования, оно содержит элемент ИСКЛЮЧАЩЕЕ ИЛИ, причем вход деления устройства соединен с первым входом элемента КПИ каж

дого вычислительного блока, первые разряды первого и второго информаци- выходом устройства, разряды, кроме (i + 1) -го и (i + 2/-го, выхода вторс-

дого вычислительного блока, первые разряды первого и второго информаци- выходом устройства, разряды, кроме (i + 1) -го и (i + 2/-го, выхода вторс-

онных входов устройства соединены соответственно с первым и вторым входами элемента ИСКЛОЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом элемента И, младщий разряд второго информационного выхода устройства соединен с (п + 1)-м разрядом выхода второго коммутатора, вход извлечения квадратного корня устройства соединен с вторым входом элемента ИЛИ каждого вычислительного блока, выход второго регистра последнего вычислительного блока является третьим информационным

дого вычислительного блока, первые разряды первого и второго информаци- выходом устройства, разряды, кроме (i + 1) -го и (i + 2/-го, выхода вторс-

го регистра i -го вычислительного блока соединены с соответствуюшими разрядами информационного входа второго f регистра ( + }) -го вычислительного блока, (h + l) -и разряд выхода второго коммутатора т-го вьмислительного блока соединен с младшим разрядом информационного входа третьего регистра {i + 1) -го вычислительного блока, причем в i -м вычислительном блоке вы-

ход второго элемента ИСКЛЮЧАКЯЦЕЕ ИЛИ соединен с. (.п + 1)-м разрядом второго информационного входа третьего

91290299 . 10

коммутатора, соединен с первым разря- второго регистра, третий управляющий дом выхода сумматора-вычитателя, вто- вход второго коммутатора и второй рой вход элемента ИЛИ соединен с уста- управляющий вход первого коммутатора новочным входом ( 2)-го разряда соединен с выходом элемента ИЛИ.

5

ТгГ

Редактор М. Дьшын

Составите,пь А, Клюев

Техред Л 0лейник Корректор С. Черни

7902/46

Тираж 673 Подписное ВИНИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушскал наб., д. 4/5

.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ТгГ

-Т5Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Конвейерное арифметическое устройство | 1984 |

|

SU1203511A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

Изобретение относится к области вычислительной техники и может быть использовано для конвейерной обработки массивов чисел. Целью изобретения является сокращение затрат оборудования. Поставленная цель достигается тем, что арифметическое устройство, содержащее элемент И и вычислительные блоки, казкдый из которых содержит три регистра, сумматор-вычита- тель, триггер, элемент ИЛИ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, три коммутатора, два элемента И и элемент НЕ, содержит элемент ИСКЛЮЧАЮЩЕЕ ШШ с соответствующими связями. 1 ил. (Л С

| Арифметическое устройство | 1979 |

|

SU798825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-08-16—Подача