1Ш

Изобретение относится к преобразованию сигналов в цифровых системах автоматического управленияз в частности к области обработки сигнапов,, передаваемых по цифровым линиям снязи, и может быть использовано в динамических системах для подавления помехи, характеризующейся фиксированной частотой изменения и случайной амплитудой

Известно устройство рдя цифровой фильтрации, содержащее регистры, блок управления, сумматоры блок памяти, аналого-цифровой преобразователь и регистр сдвига Ct 3 .

Наиболее близким по технической сущности к изобретению является устройство для цифровой фильтрации, содержащее три регистра, умножитель, накапливающий сумматор, память козффициентов и блок управления, причем выходы регистров соединены с входами соответствующих умножителей, выходьг которых соединены с входами накапливающего сумматора C2J .

Недостатком известного устройства является вносимьш им фазовый сдвиг выходного сигнала по отношению к вхоному и неполная фильтрация помех.; т низкая точность фильтрации,

Цель изобретения - повышение точности (способности распознавать поме-хи в смеси полезного сигнэ„па и -лума, независимо от соотношения их частот. и вццелять распознангме noMexi- из смеси сигнала и шума практически без искаже.ния амплитудно-фазовой характеристики .

Поставленная цель достигается тем что в устройство, содержащее сдвиговый регистр, информшдионшзй вьгход которого подключен к информационному входу первого регистра, и:- формациовный выход которого является яыформа-ционным выходом устройства, зторой регистр, информациснный выход которО го соединен с информационным BXojjfOM третьего регистра, блок памяти коэффициентов, адрес№ш вход которого поключен к группе выходов блока постоя ной памятиJ выход первого разряда ко торого соединен с управляюз ик сдвигового регистра, информат-щокный вход которого объединен с входами разрядов адреса, кроме первого и второго, блока постоянной памяти и является информациоишлм входом устройства, вьгход второго разряда блс ка постоянной памяти соединен с так552

товыми входами первого, второго, т-ретьего регистров и тактовым входом сдвигового регистра, введены сумматор-вычитатель и блок анализа, содержашдш пррвую и вторую группы элементов И и элемент ИЛИ, выход которого подключен к входу первого разряда адреса блока постоянной памяти, вход второго зазряда адреса которого подключен к выходу разряда знака сумматора-вычитателя, выход разности которого соединен с информационным -входом второго регистра, выход разрядов которого подключен к первому входу сумматора-вычитателя, первым входам соответствующих элементов И второй группы, вторые инверсные вход) которых объединены с вторым -1 входами соответствующих элементов И первой группы, вторым входом cj NMaropa-вычитателя и подключены к выходам соответствующих разрядов третьего регистра, выходы элементов И первой и второй группы подключены к соответствующим входам элемента ИЛИ информационный вход первого регистра соединен с выходом суммы сумматора-вычитатепя, третий вход которого подключен к информационному выходу первого регистра, а четвертый и пятый входы сумматоравы-штателя соединены соответственно с информационным выходом сдвигового регистра и информационным выходом блока п.мяти коэффициентов.

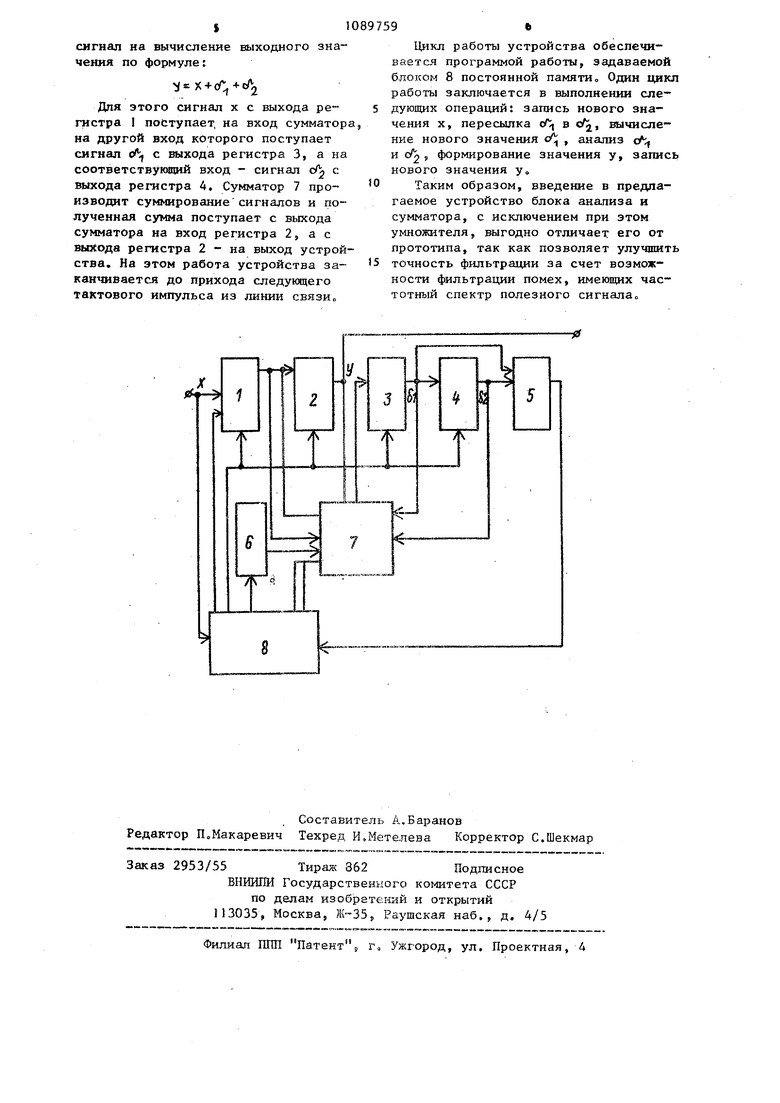

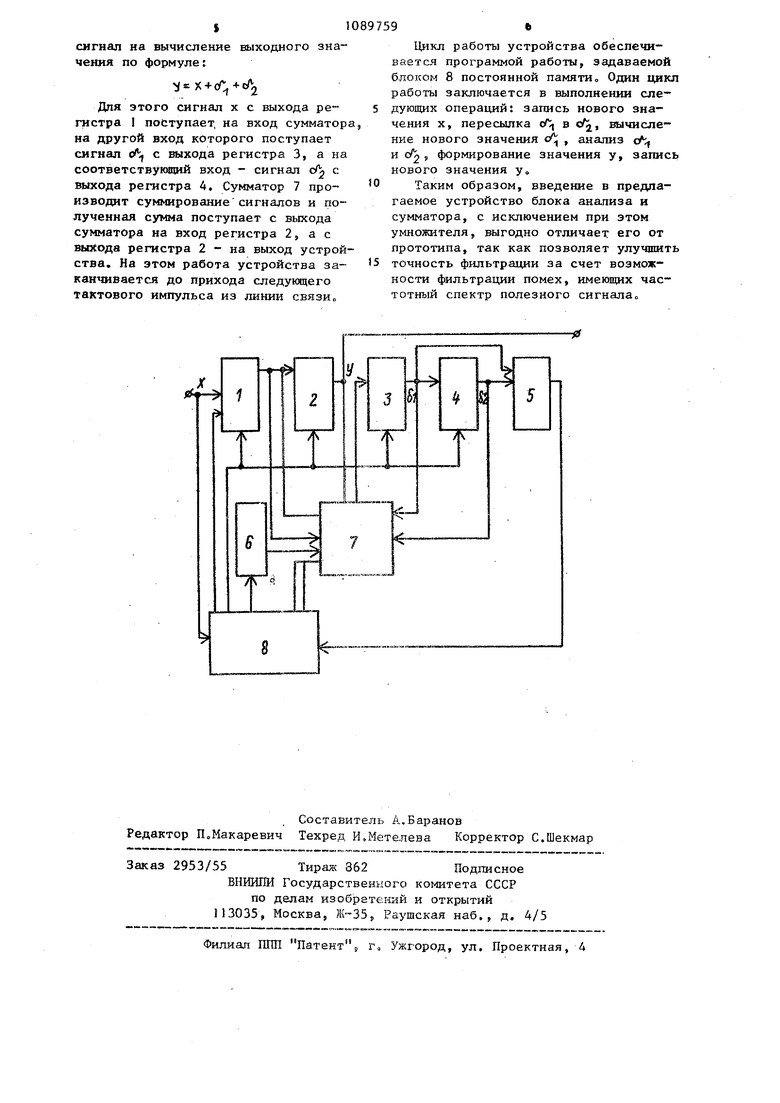

На чертеже представлена функциональная схема устройства для цифроЕюй фильтрации.

Устройство содержит сдвиговый регистр If (параллельные) регистры 2-4 блок 5 анализа, содержащий две группы элементов И, выходы которых подключены к входам элемента ИЛИ, блок памяти коэффициентов, сумматор 7, блок 8 постоянной памяти о На чертеже также обозначено: х - входной сигнал устройства из цифровой линии связи; у - выходной сигнал устройства; сГ - сигнал на выходе регистра 3, равный разности входного сигнала х и выходного сигнала у; сигнал на выход регистра 4, равный разности входного и выходного сигналов на предыдущем такте квантования входного сигнала х 2 - сигнал условия

Работа устройства во времени связана с ч актовыми импульсами в линии связн, двумя тактовыми импуль3сами на линии связи блок 8 формирует сигналы, обеспечивакйцие выполнение алгоритма работы устройства: анализ сигналов на регистрах 1-4 и формирование выходного сигнала у, Устройство работает следукицим образомПо приходу тактового импульса из линии связи входной сигнал х, представляющий собой последовательный код, поступает на сдвиговый регистр 1, где преобразуется в параллельный код и запоминается. Затем блок 8 выдает сигнал, по которому сигнал о вычисленный на предыдущем такте кван тования входного сигнала, с выхода второго регистра 3 поступает на вход регистра 4, где и запоминается„ Затем блок 8 вьщает сигнал на вычисление нового значения о х - у. Для этого входной сигнал х с выхода сдви гового регистра 1 поступает на вход сумматора 7, на другой вход которого поступает входной сигнал с выхода регистра 2. В сумматоре 7 производится вычисление разности j х которая с первого выхода сумматора поступает на вход регистра 3,где и запоминается о Далее производится анализ сигналов о и сУ и формирование выходного сигнала у в зависимости от их значений, В первую очередь значение cA/j сравнивается с пороговым значением д хранящимся в блоке 6 памяти коэффициентов. Если значение с превышает пороговое значение 4 , фильтрация не производится, и в качестве выход ного значение У берется значение входного сигнала х. Для этого по сиг налу блока 8 на вход сумматора посту пает сигнал сУ с выхода регистра 3, а на другой вход сумматора поступает значение 4 из блока 6 памяти коэффи Сумматор 7 производит вычициентов. тание сигналов сУ и /J и формирует признак результата, поступакяций на адресный вход в блок 8; Следуияций си нал блок 8 формирует в зависимости о признака результата: если значение о превысило пороговое значение Д, фор{шруется сигнал, по которому сигнал с вьосода регистра 1 поступает на регистр 2, а с выхода регистра 2 на выход устройства, и на этом работ устройства заканчивается до прихода следующего тактового импульса из лин связи; если же значение (Л, не преил59шает порогового значения Д , формируется сигнал на сравнение значения «/2 с нулем. Для этого сигнал с с выхода регистра 4 поступает на вход сумматора 7, на другой вход которого из блока 6 памяти коэффициентов поступает сигнал, равный нулю Сумматор 7 производит вычитание сиг- налов а и нуля и формирует признак результата, поступающий в блок 8, который формирует следующий сигнал в зависимости от признака результата; если значение о/ равно нулю, работа устройства заканчивается до прихода следуклцего тактового импульса из линии связи и переопределения выходного значения у не происходит; если значение Oj равно нулю, формируется сигнал на сравнение значения сЛ( с нулем Для этого сигнал «Л с выхода регистра 3 поступает на вход сумматора, на другой вход которого из блока 6 памяти коэффициентов поступает сигнал, равный нулю. Сумматор 7 производит вычитание сигналов оС( и нуля и формирует признак результата, поступающий в блок 8, Следующий сигнал формируется в зависимости от признака результата: если значение сЛ( равно нулю, формируется сигнал, по которому сигнал у с выхода регистра 1 поступает на регистр 2, а оттуда на выход устройства, и на этом работа устройства заканчивается до прихода следующего так тового импульса из линии связи; если значение сУ не равно нулю, формируется сигнал, по которому производится анализ знаков сЛ, к ка совпадение. Для этого с выхода регистра 3 сигнал поступает на вход блока 5 анализа, на другой вход которого поступает сигнал выхода регистра 4, Блок 5 анализа представляет собой группы элементов И и элемент ИЛИ, формирующие сигнал t по закону (а - знак с/ , в - знак с ). 2 0(Л Уо«ЛЬ С выхода блока анализа 5 сигнал z поступает на адресный вход в блок В, который формирует следующий сигнал в зависимости от значения z : если Z 1, формируется сигнал, по которому сигнал X с выхода регистра 1 поступает на регистр 2 и на вход устройства, на этом работа устройства заканчивается до следующего тактового импульса; если 2 О, формируется сигнал на вычисление выходного зна чения по формуле: у х-юг:,+«л Для этого сигнал х с выхода регистра 1 поступает, на вход сумматор на другой вход которого поступает сигнал Л| с выхода регистра 3, а на соответствукяций вход - сигнал с/ с выхода регистра 4. Сумматор 7 производит суммирование сигналов и полученная сумма поступает с выхода сумматора на вход регистра 2, а с выхода регистра 2 - на выход устрой ства. На этом работа устройства заканчивается до прихода следующего тактового импульса из линии связи„ 96 Цикл работы устройства обеспечивается программой работы, задаваемой блоком 8 постоянной памяти. Один цикл работы заключается в выполнении еле- дующих операций: запись нового значения X, пересылка сЛ| в c/j, вычисление нового значения с , анализ /; и S формирование значения у, запись нового значения у. Таким образом, введение в предлагаемое устройство блока анализа и сумматора, с исключением при этом умножителя, выгодно отличает его от прототипа, так как позволяет улучшить точность фильтрации за счет возможности фильтрации помех, имеющих частотный спектр полезного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1989 |

|

SU1695321A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для умножения переменной на дробь | 1987 |

|

SU1543400A1 |

| Устройство для калмановской фильтрации | 1987 |

|

SU1564711A1 |

| Устройство коррекции | 1987 |

|

SU1499507A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Устройство для вычисления коэффициентов дискретного преобразования Хаара | 1982 |

|

SU1061151A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ФИЛЬТРАЦИИ, содержащее сдвиговый регистр, информационный выход которого подключен к информационному входу первого регистра, информационный выход которого является информационным выходом устройства, второй регистр, информационный выход которого соединен ,с информационным входом третьего регистра, блок памяти коэффициентов, адресный вход которого подключен к группе выходов блока постоянной памяти, выход первого разряда которого соединен с управляющим входом сдвигового регистра, информационный вход которого соединен с входами разрядов адреса, кроме первого и второго блока постоянной памяти, и является ни- формационным входом устройства, вы-; ход второго разряда блока постоянной памяти соединен с тактовыми входами первого, второго, третьего регистров и тактовым входом сдвигового регистра, отличающееся тем, что, с целью повьппения точности фильтрации, в него введены сумматор-вычитатель и блок анализа, содержащий первую и вторую группь элементов И и элемент ИЛИ, выход которого подключен к входу первого разряда адреса блока постоянной памяти, вход второго разряда адреса котррого подключен к выходу разряда знака сумматоравычитателя, выход разности которого соединен с информационным входом второго регистра, выход разрядов которого подключен к первому входу сумматора-вычитателя, пернмм входам соответствующих элементов И второй группы, вторые инверсные входы которых соединены с вторыми входами соответствующих элементов И первой группы, вторым входом сумматора-вычитатеа К ля и подключены к выходам соответствукйцих разрядов третьего регистра, выходы элементов И первой и второй группы подключены к соответствующим входам элемента ИЛИ, информационный 00 со вход первого регистра соединен с выходом суммы сумматора-вычитателя, i тий вход которого подключен к инСП формационному выходу первого регистра, а четвертый и пятый входы сумматора-вычитателя соединены соответственно с информационным выходом сдвигового регистра и информационным выходом блока памяти коэффициентов.

/ч

/ч

--гт

и И 5

I

ч

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Гольденберг Л.М., Левчук Ю.П, Поляк М.Н | |||

| Цифровые фильтры М., Связь, 1974, Со 116 (гьрототип), | |||

Авторы

Даты

1984-04-30—Публикация

1983-02-15—Подача