Изобретение относится к импульсной технике и может быть использовано при разработке универсальных и специализированных интегральных схем на комплементарных МДП-транзисторах.

Цель изобретения - повышение надежности логического элемента.

Поставленная цель -достигается уменьшением числа используемых транзисторов ,

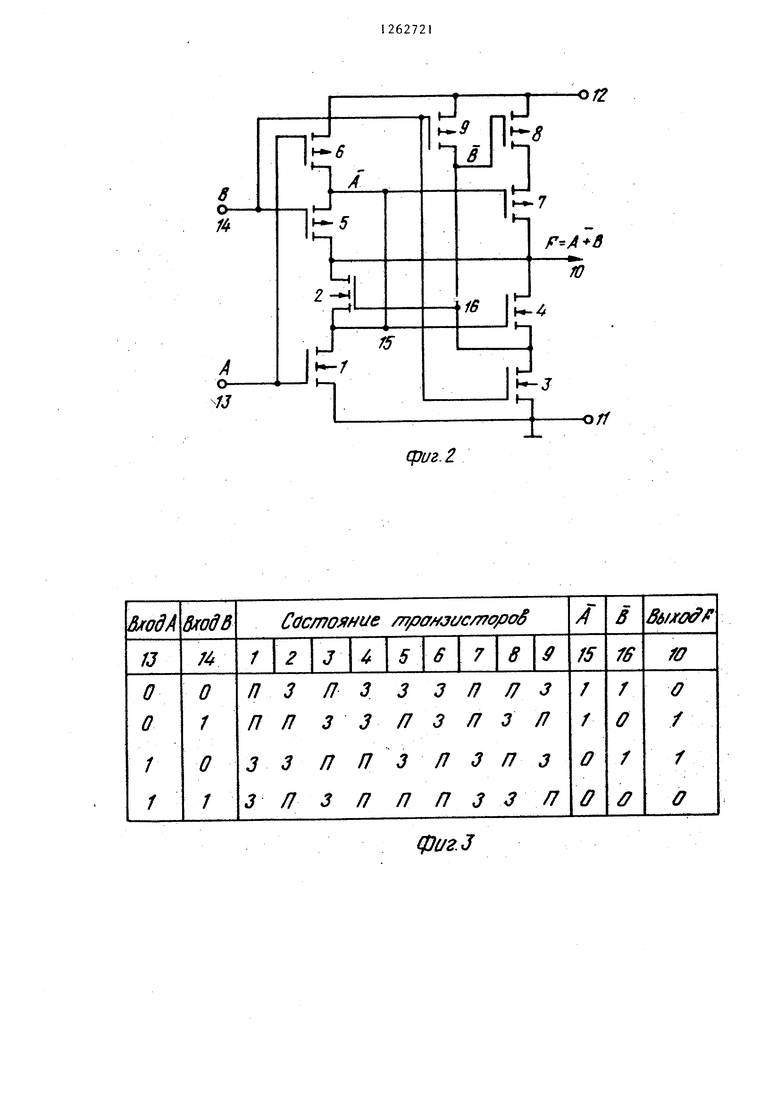

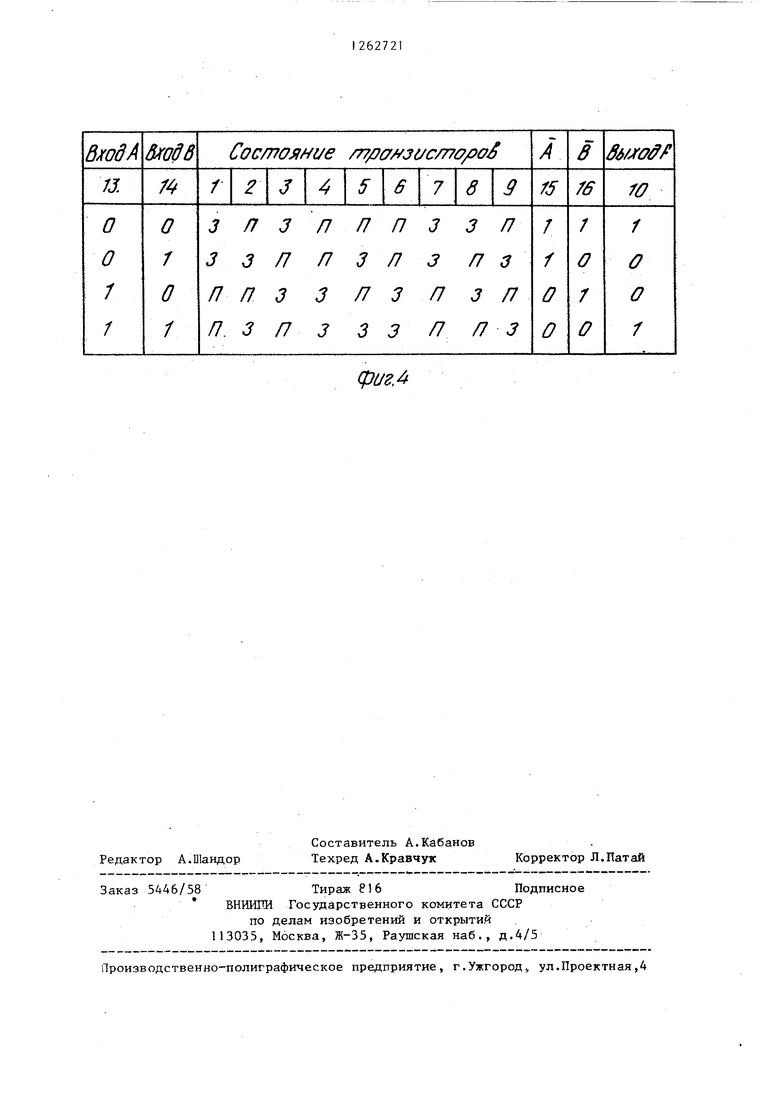

На фиг.1 представлена электрическая принципиальная схема логического элемента НЕРАВНОЗНАЧНОСТЬ; на фиг.2 - то же, логического элемента РАВНОЗНАЧНОСТЬ; на фиг.З - таблица истинности-логического элемента НЕРДВНОЗНАЧНОСТЬ; на фиг. 4 - то же, логического элемента РАВНОЗНАЧНОСТЬ.

Логический элемент содержит рканальные (фиг.) или м -канальные (фиг.2) транзисторы I - 4, я -канальные (фиг.1) или р -канальные (фиг.2) транзисторы 5-9, образующие четыре пары последовательно включенных транзисторов 1 и 2, 3 и 4, 5 и 6, 7 и 8, стоки транзисторов 2,4,5 и 7 подключены к выходной шине 10, истоки транзисторов 1 и 3 подключены к шине 11 питания, истоки транзисторов 6,8 и 9 подключены к йторой шине 12 питания, сток транзистора 9 подключен к затворам транзисторов 2 и 8 и к стоку транзистора 3, затворы транзисторов 1 и 6 подключены к первой входной шине 13, затворы транзисторов 3,5 и 9 подключены к второй входной шине 14.- На входную, шину 13 поступает логическая переменная А , на шину 14 - логическая переменная В , в узле 15 реализуется инверсия логической переменной А-А, в узле 16 - инверсия логической переменной Б-В.

Логический элемент НЕРАВНОЗНАЧНОСТЬ (фиг.1) работает в соответствии с таблицей истинности (фиг.З). В таблице истинности низкому и высокому уровням сигналов соответствуют .логические О и 1 обозначения flL и 3 соответствуют состояниям транзисторов, когда они проводят ( П) и когда закрыты (Э). Во второй строке таблицы истинности приведены подчиненные номера транзисторов, соответствующие фиг..

При А О и В О уровень логического О на выходе F устанавливается

через проводящие транзисторы 7 и 8, при А и В 1 - через транзисторы 5 и 6 .

При А О и В 1 уровень логической 1 на выходе F устанавливается через проводящие 1 и 2, при А 1 и В О - через транзисторы 3 и 4.

Логический элемент РАВНОЗНАЧНОСТЬ (фиг.2)работает в соответствии с таблицей истинности (-фиг.4).

При А О и В О уровень логи-. ческой 1 на выходе F устанавливается через проводящие транзисторы 5 и 6, при А 1 и В 1 - через 5 транзисторы 7 и 8.

При А О и В 1 уровень логического О на выходе F устанавливается через проводящие транзисторы , 0 3 и 4, при А 1 и В О - через

проводящие транзисторы 1 и 2.

I

Формула изобретения

5 Логический элемент на КМДП-транзисторах, содержаш,ий, первый, второй, третий и четверть1Й транзисторы с каналами проводимости первого типа и пятьй, шестой, седьмой, вось0 мой и девятый транзисторы с каналами проводимости второго типа, стоки второго. Четвертого, пятого и седьмого транзисторов подключены к вы- .ходной шине, а их истоки - соответственно к стокам первого, третьего, шестого и восьмого транзисторов, истоки первого и третьего транзисторов подключены к первой шине питания истоки шестого, восьмого и девятого транзисторов подключены к второй шине питания, сток девятого транзистора подключен к затворам второго и восьмого транзисторов и стоку третьего транзистора, затвор первого транзистора подключен к первой входной шине, затворы третьего и девятого транзисторов подключены к второй входной шине, затворы четвертого и седьмого транзисторов подключены к стоку первого транзистора, от л ичающийся тем, что, с целью повьшения надежности, затвор н сток шестого транзистора подключены соответственно к первой входной шине и стоку первого транзистора, а затвор

5 пятого транзистора подключен к второй входной шине.

cpuB.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный компаратор на МДП транзисторах | 1985 |

|

SU1287267A1 |

| Устройство для формирования группового переноса | 1985 |

|

SU1335981A1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| Сумматор по модулю два | 1984 |

|

SU1191906A1 |

| Устройство сравнения на МДП-транзисторах | 1985 |

|

SU1365351A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

| Логический элемент | 1981 |

|

SU997252A1 |

Изобретение относится к импульсной технике и может использоваться при разработке универсальных и спе- , циализированных интегральных схем на комплементарных МДП-транзисторах. Цель изобретения - повьщение надежности логического элемента (ЛЭ) - достигается уменьшением числа используемых транзисторов. ЛЭ содержит р -канальные транзисторы 1-4, П-канальные транзисторы 5-9, образующие четыре пары последовательно включенных транзисторов 1 и 2, 3 и4, 5и6, 7и8, вькодную 10, шины 11 и 12 питания, входные шины 13 и 14, узлы 15 и 16, в которых реализуется инверсия логических переменных А-А и В-В соответственно. На чертеже показана схема ЛЭ НЕРАВНОЗНАЧНОСТЬ. В описании изобретения с приводится схема ЛЭ РАВНОЗНАЭДОСТЬ. (Л 4 ил.

физ.З

фиг А

| Полусумматор на МДП-транзисторах | 1981 |

|

SU1008909A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 4006365, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-10-07—Публикация

1985-01-03—Подача