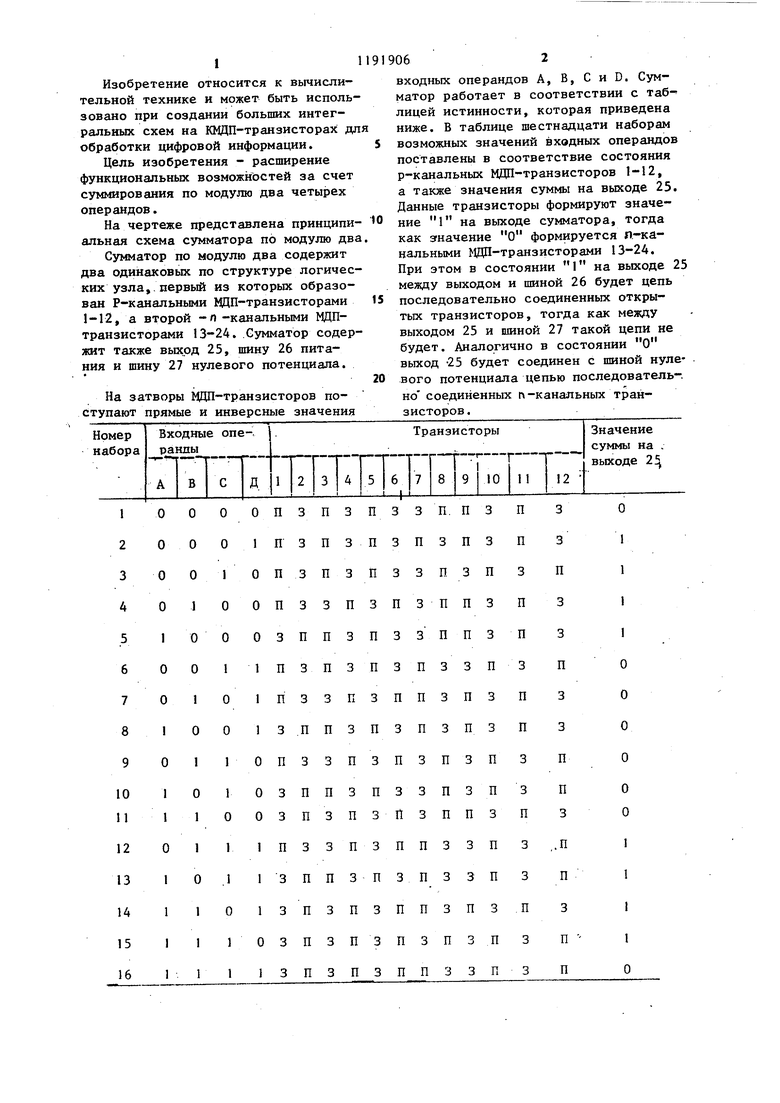

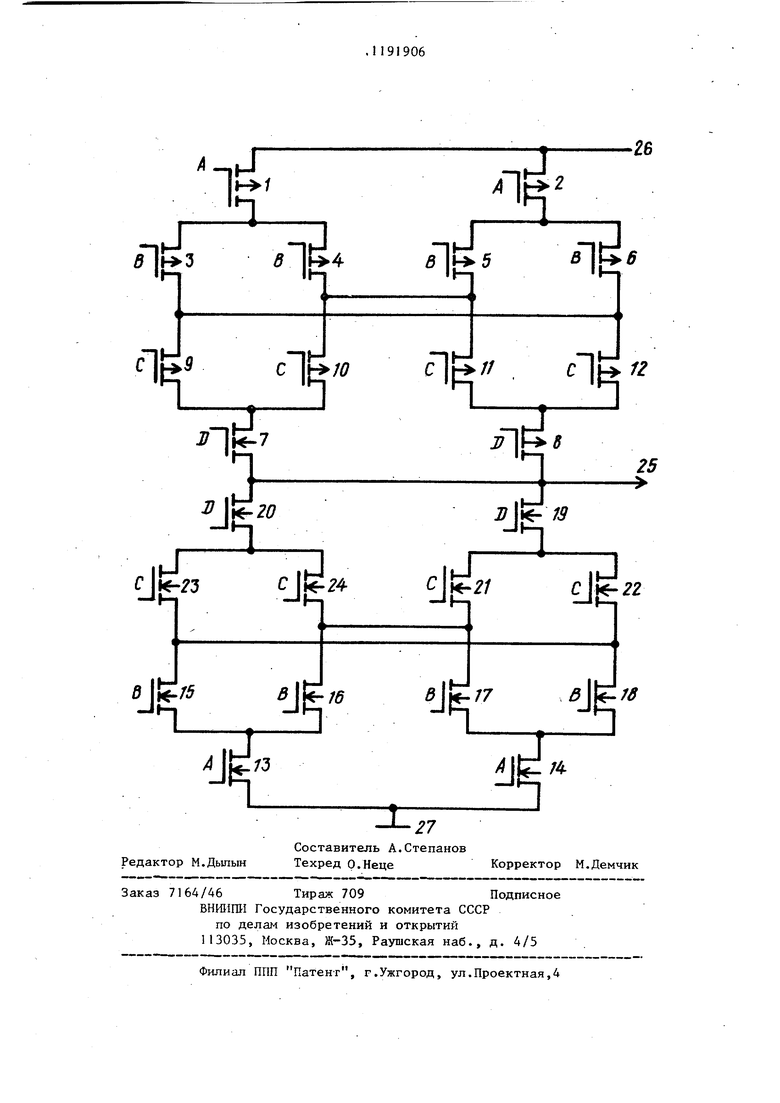

1 Изобретение относится к вычислительной технике и может быть исполь зовано при создании больших интегральных схем на КМДП-транзисторах д обработки цифровой информации. Цель изобретения - расширение функциональных возможностей за счет суммирования по модулю два четырех операндов. На чертеже представлена принципи альная схема сумматора по модулю дв Сумматор по модулю два содержит два одинаковых по структуре логичес ких узла,, первый из которых образован Р-канальными ЦЦП-транзисторами 1-12, а второй -п -канальными МДПтранзисторами 13-24. Сумматор содер жит также вьщрд 25, шину 26 питания и шину 27 нулевого потенциала. На затворы ЩЩ-траизисторов поступают прямые и инверсные значения 062 входных операндов А, В, С и D. Сумматор работает в соответствии с таб-лицей истинности, которая приведена ниже. В таблице шестнадцати наборам возможных значений входных операндов поставлены в соответствие состояния р-канальных МДП-транзисторов 1-12, а также значения суммы на выходе 25. Данные транзисторы формируют значение 1 на выходе сумматора, тогда как значение О формируется п-канальными МДП-транзисторами 13-24. При этом в состоянии 1 на выходе 25 между выходом и шиной 26 будет цепь последовательно соединенных открытых транзисторов, тогда как между выходом 25 и шиной 27 такой цепи не будет. Аналогично в состоянии О выход -25 будет соединен с шиной нулевого потенциала цепью последователь-, но соединенных h-канальных транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

| Одноразрядный сумматор | 1983 |

|

SU1117634A1 |

| Многофункциональное логическое устройство | 1982 |

|

SU1089761A1 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| Формирователь импульсов | 1983 |

|

SU1123056A1 |

| Формирователь импульсов | 1987 |

|

SU1431054A1 |

| Устройство согласования уровней напряжения /его варианты/ | 1983 |

|

SU1138940A1 |

| Управляемый мажоритарный элемент | 1982 |

|

SU1069167A1 |

| @ -Триггер | 1983 |

|

SU1164867A1 |

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

СУММАТОР ПО МОДУЛЮ ДВА, содержащий два логических узла, причем первый узел содержит восемь р-канальных МДП-транзисторов, а второй - восемь п-канапьных МДП-транзисторов , в каждом логическом узле исток Пзрвого МДП-транзистора соединен с истоком второго МЦП-транзистора, а их затворы соединены соответственно с прямым и инверсньм входами первого операнда сумматора, сток первого МДП-транзистора соединен с истоками третьего и четвертого МДПтранзисторов, а сток второго МДП-транзистора соединен с истоками пятого и шестого ВДП-транзисторов, затворы третьего и пятого МДП-транзисторов соединены с прямым входом второго операнда сумматора, а затворы четвертого и шестого ЩЩ-транзисторов соединены с инверсным входом второго операнда сумматора, сток третьего ЦЩ1-транзистора соединен со стоком шестого МДП-транзистора, а сток четвертого МДП-транзистора соединен со стоком пчтого. МДП-транзистора, сток седьмого МЦП-транзистора соединен со стоком восьмого ВДП-транзистора и с выходом сумматора, затворы седьмого и восьмого МДП-транзисторов соединены соответст-. венно с прямым и инверсным входами третьего операнда сумматора, исток первого МДП-транзистора первого логического узла соединен с шиной питания сумматора, а исток первого МДП-транзистора второго логического узла соединен с шиной нулевого потенциала сумматора, отличающийс я тем, что, с целью расширения функциональных возможностей за счет суммирования по модулю два четырех I операндов, сумматор дополнительно (Л содержит в первом логическом узле Р-канальные МДП-транзисторы с девятого по двенадцатый, а во втором логическом узле - п -канальные МЦП транзисторы с девятого по двенадцатый, причем в каждом узле .истоки девятого и десятого МДП-транзисторов соединены соответственно со стокасе ми третьего и четвертого МДП-транS зисторов , истоки одиннадцатого и двенадцатого МДП-транзисторов соедио а нены соответственно со стокамичетвертого итретьего ВДП-транзисторов,затворы девятого и одиннадцатогоМДП-тран зисторов соединены с прямым входом четвертого операнда сумматора, а затворы десятого и двенадцатого МДП-тран.зисторов соединены с инверсным входом четвертого операнда сумматора, стоки девятого и десятого ВДП-транзисторов соединены с истоком седьмого МДП-транзистора,астоки одиннадцатого и двенадцатогоМДП-транзисторов с истоком восьмого МДП-транзистора.

10 11

озппзпззпзп

12 13 14 15

16

-hu

1g

Ли Л Л д d& dg

26

Л

ЛЕ

Щ Лё -п- 271 / Ц dt di

| Патент США № 4417161, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Обзоры по электронной технике | |||

| Сер | |||

| Микроэлектроника, вып | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

Авторы

Даты

1985-11-15—Публикация

1984-04-29—Подача