нен с одним из входов третьего вентиля, к другому входу которого подсоединена через второй элемент задержки шина пуска, выход третьего вентиля соединен с единичным входом триггера блокировки, к нулевому входу которого подсоединен третий выход распределителя.

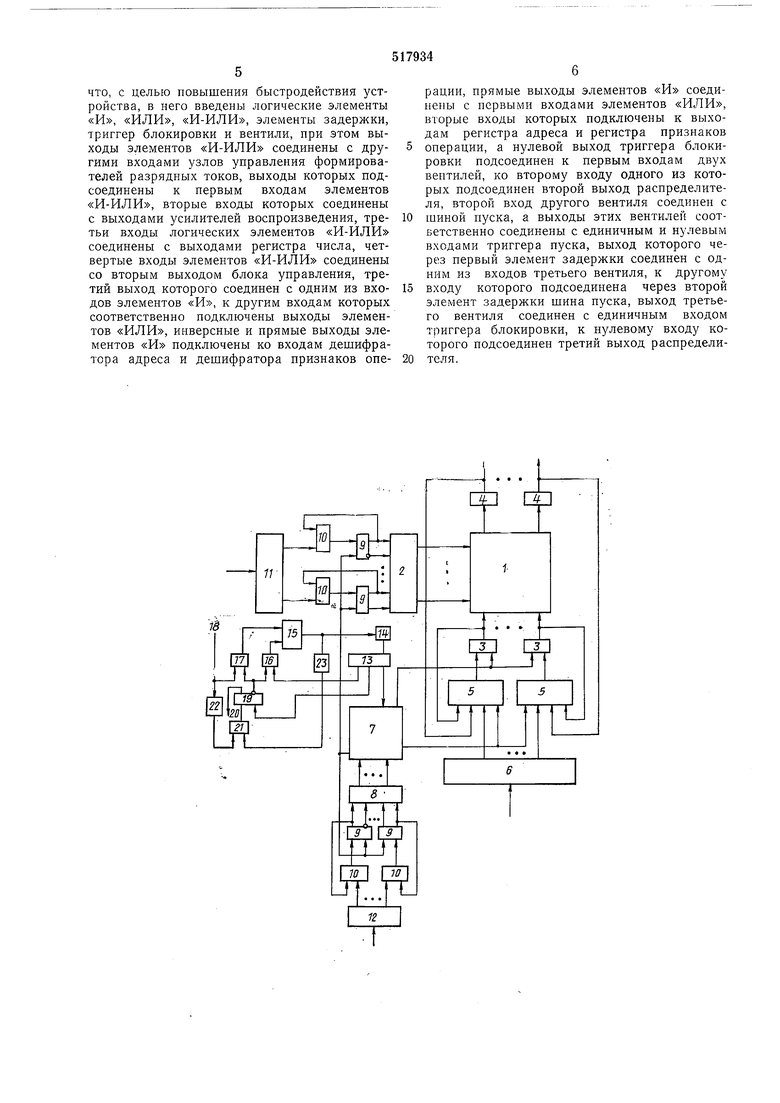

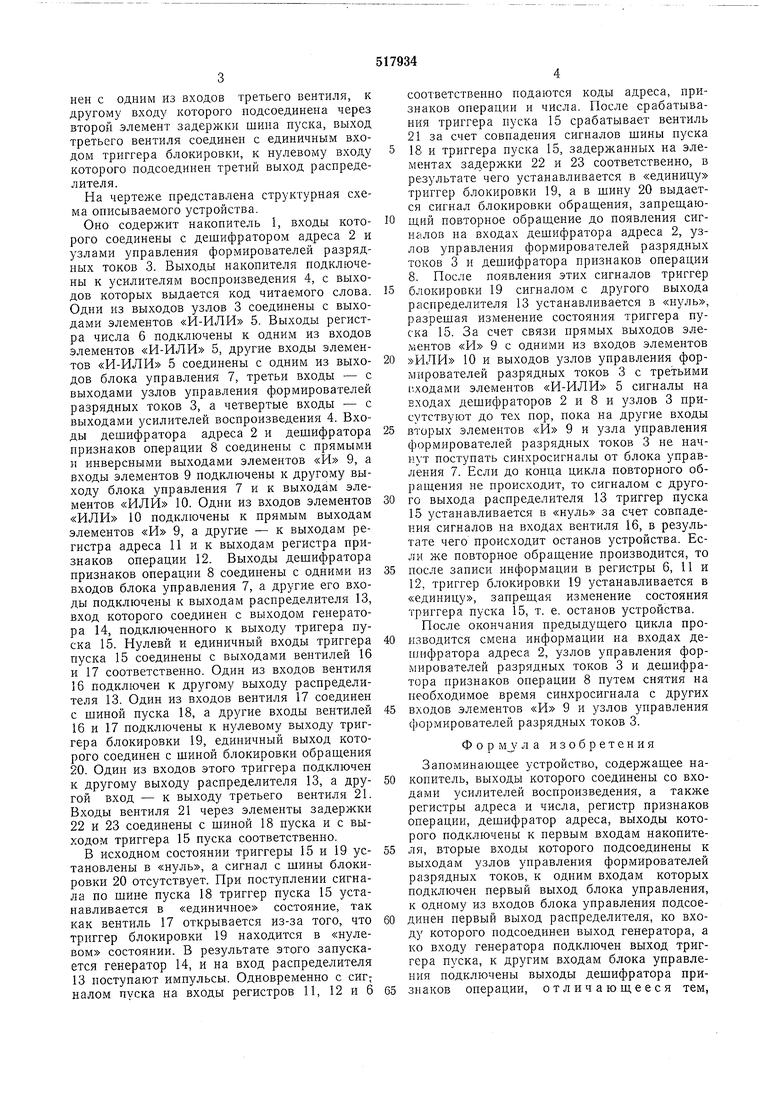

На чертеже представлена структурная схема описываемого устройства.

Оно содержит накопитель 1, входы которого соединены с дешифратором адреса 2 и узлами управления формирователей разрядных токов 3. Выходы накопителя подключены к усилителям воспроизведения 4, с выходов которых выдается код читаемого слова. Одни из выходов узлов 3 соединены с выходами элементов «И-ИЛИ 5. Выходы регистра числа 6 подключены к одним из входов элементов «И-ИЛИ 5, другие входы элементов «И-ИЛИ 5 соединены с одним из выходов блока управления 7, третьи входы - с выходами узлов управления формирователей разрядных токов 3, а четвертые входы - с выходами усилителей воспроизведения 4. Входы дешифратора адреса 2 и дешифратора признаков операции 8 соединены с прямыми }i инверсными выходами элементов «И 9, а входы элементов 9 подключены к другому выходу блока управления Тик выходам элементов «ИЛИ 10. Одни из входов элементов «ИЛИ 10 подключены к прямым выходам элементов «И 9, а другие - к выходам регистра адреса Пик выходам регистра признаков операции 12. Выходы дешифратора признаков операции 8 соединены с одними из входов блока управления 7, а другие его входы подключены к выходам распределителя 13, вход которого соединен с выходом генератора 14, подключенного к выходу тригера пуска 15. Нулевй и единичный входы триггера пуска 15 соединены с выходами вентилей 16 и 17 соответственно. Один из входов вентиля 16 подключен к другому выходу распределителя 13. Один из входов вентиля 17 соединен с шиной пуска 18, а другие входы вентилей 16 и 17 подключены к нулевому выходу триггера блокировки 19, единичный выход которого соединен с шиной блокировки обраш,ения 20. Один из входов этого триггера подключен к другому выходу распределителя 13, а другой вход - к выходу третьего вентиля 21. Входы вентиля 21 через элементы задержки 22 и 23 соединены с шиной 18 пуска и с выходом триггера 15 пуска соответственно.

В исходном состоянии триггеры 15 и 19 установлены в «нуль, а сигнал с шины блокировки 20 отсутствует. При поступлении сигнала по шине пуска 18 триггер пуска 15 устанавливается в «единичное состояние, так как вентиль 17 открывается из-за того, что триггер блокировки 19 находится в «нулевом состоянии. В результате этого запускается генератор 14, и на вход распределителя 13 поступают импульсы. Одновременно с сиг; налом пуска на входы регистров И, 12 и 6

соответственно подаются коды адреса, признаков операции и числа. После срабатывания триггера пуска 15 срабатывает вентиль 21 за счет совпадения сигналов шины пуска 18 и триггера пуска 15, задержанных на элементах задержки 22 и 23 соответственно, в результате чего устанавливается в «единицу триггер блокировки 19, а в шину 20 выдается сигнал блокировки обраш,ения, запреш,ающий повторное обращение до появления сигналов на входах дешифратора адреса 2, узлов управления формирователей разрядных токов 3 и дешифратора признаков операции 8. После появления этих сигналов триггер блокировки 19 сигналом с другого выхода распределителя 13 устанавливается в «нуль, разрешая изменение состояния триггера пуска 15. За счет связи прямых выходов элементов «И 9 с одними из входов элементов ИЛИ 10 и выходов узлов управления формирователей разрядных токов 3 с третьими г.ходами элементов «И-ИЛИ 5 сигналы на входах дешифраторов 2 и 8 и узлов 3 присутствуЕот до тех пор, пока на другие входы вторых элементов «И 9 и узла управления формирователей разрядных токов 3 не начнут поступать синхросигналы от блока управления 7. Если до конца цикла повторного обращения не происходит, то сигналом с другого выхода распределителя 13 триггер пуска 15 устанавливается в «нуль за счет совпадения сигналов на входах вентиля 16, в результате чего происходит останов устройства. Если же повторное обращение производится, то после записи информации в регистры 6, 11 и 12, триггер блокировки 19 устанавливается в «единицу, запрещая изменение состояния триггера пуска 15, т. е. останов устройства.

После окончания предыдущего цикла производится смена информации на входах дещнфратора адреса 2, узлов управления формирователей разрядных токов 3 и дешифратора признаков операции 8 путем снятия на необходимое время синхросигнала с других входов элементов «И 9 и узлов управления формирователей разрядных токов 3.

Фор м J) л а изобретения

Запоминающее устройство, содержащее накопитель, выходы которого соединены со входами усилителей воспроизведения, а также регистры адреса и числа, регистр признаков операции, дешифратор адреса, выходы которого подключены к первым входам накопителя, вторые входы которого подсоединены к выходам узлов управления формирователей разрядных токов, к одним входам которых подключен первый выход блока управления, к одному из входов блока управления подсоединен первый выход распределителя, ко входу которого подсоединен выход генератора, а ко входу генератора подключен выход триггера пуска, к другим входам блока управления подключены выходы дещифратора признаков операции, отличающееся тем,

что, с целью повышения быстродействия устройства, в него введены логические элементы «И, «ИЛИ, «И-ИЛИ, элементы задержки, триггер блокировки и вентили, при этом выходы элементов «И-ИЛИ соединены с другими входами узлов управления формирователей разрядных токов, выходы которых подсоединены к первым входам элементов «И-ИЛИ, вторые входы которых соединены с выходами усилителей воспроизведения, третьи входы логических элементов «И-ИЛИ соединены с выходами регистра числа, четвертые входы элементов «И-ИЛИ соединены со вторым выходом блока управления, третий выход которого соединен с одним из входов элементов «И, к другим входам которых соответственно подключены выходы элементов «ИЛИ, инверсные и прямые выходы элементов «И подключены ко входам дешифратора адреса и дешифратора признаков операции, прямые выходы элементов «И соединены с первыми входами элементов «ИЛИ, вторые входы которых подключены к выходам регистра адреса и регистра признаков

операции, а нулевой выход триггера блокировки подсоединен к первым входам двух вентилей, ко второму входу одного из которых подсоединен второй выход распределителя, второй вход другого вентиля соединен с

шиной пуска, а выходы этих вентилей соответственно соединены с единичным и нулевым входами триггера пуска, выход которого через первый элемент задержки соединен с одним из входов третьего вентиля, к другому

входу которого подсоединена через второй элемент задержки шина пуска, выход третьего вентиля соединен с единичным входом триггера блокировки, к нулевому входу которого подсоединен третий выход распределителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| УСТРОЙСТВО ДЛЯ МОДИФИКАЦИИ АДРЕСА В ЦИФРОВОЙ СЕТИ | 1995 |

|

RU2084950C1 |

Авторы

Даты

1976-06-15—Публикация

1973-12-29—Подача