1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля и диагностики цифровых устройств, например БИС ОЗУ.

Цель изобретения - повышение достоверности контроля за счет исключения влияния задаваемых тестов на результат контроля

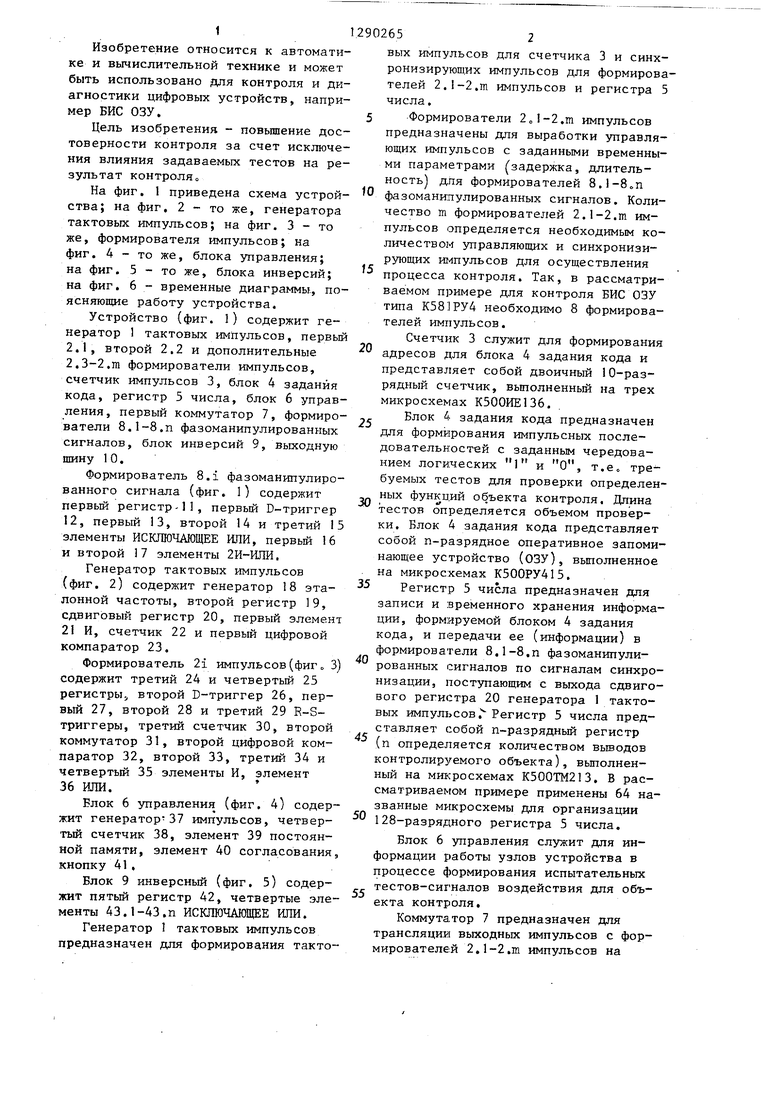

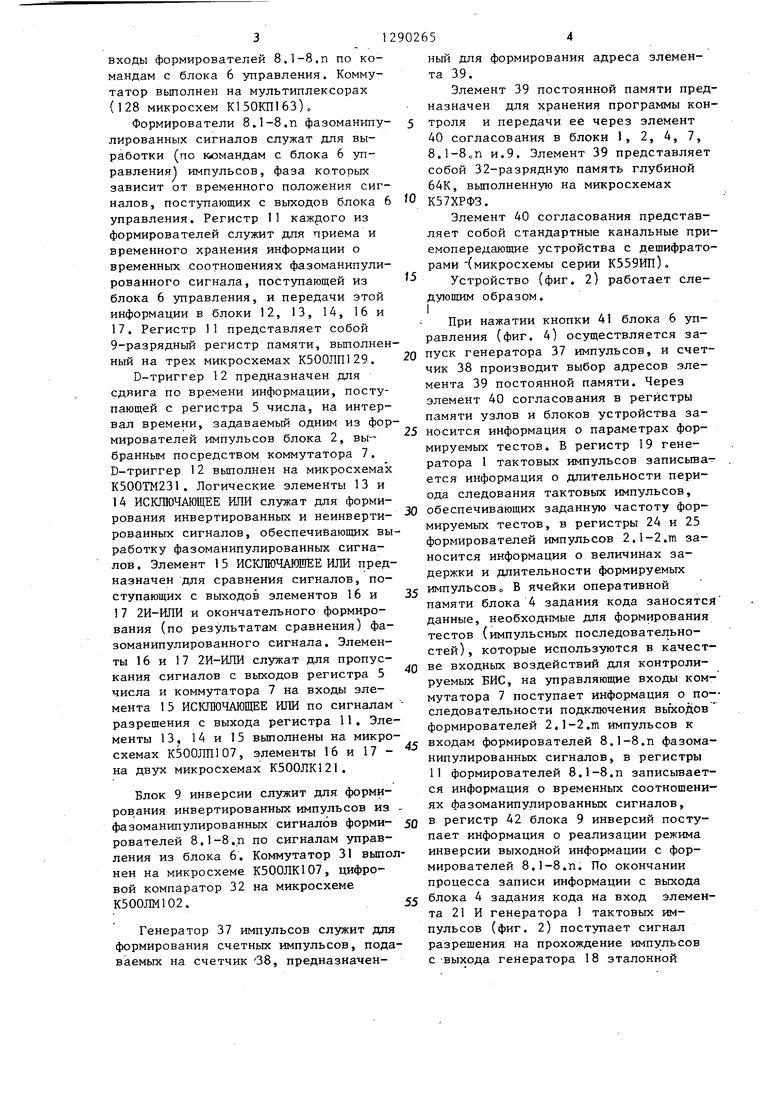

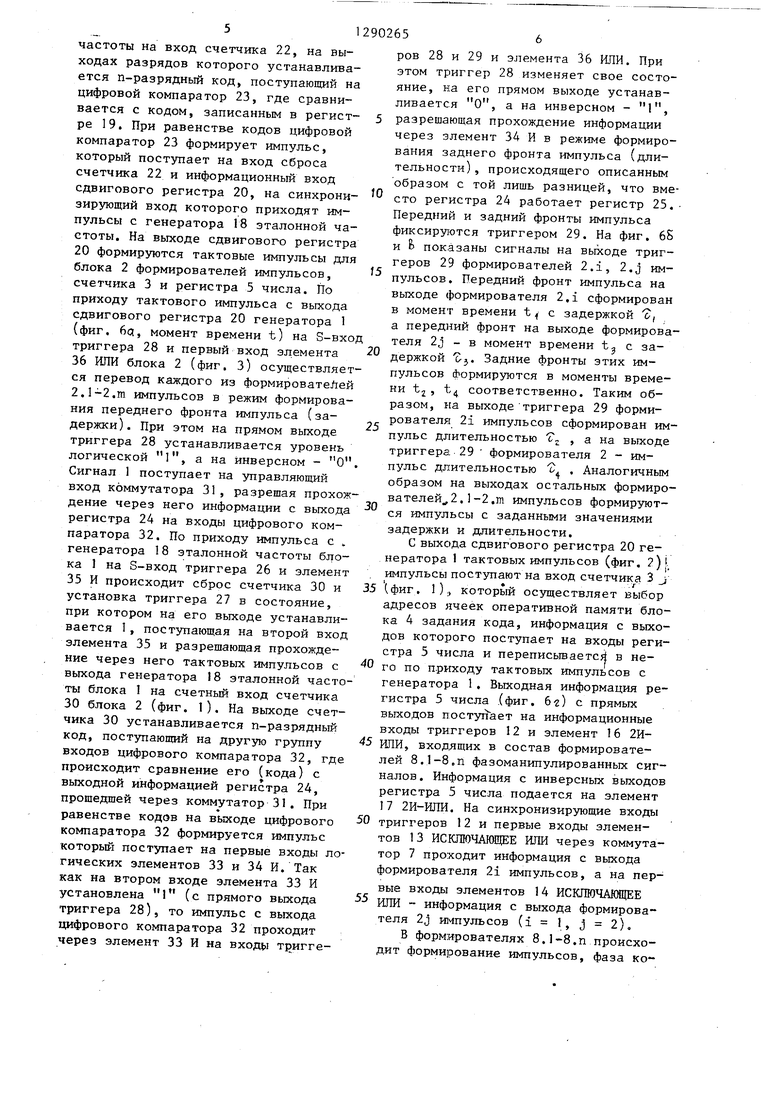

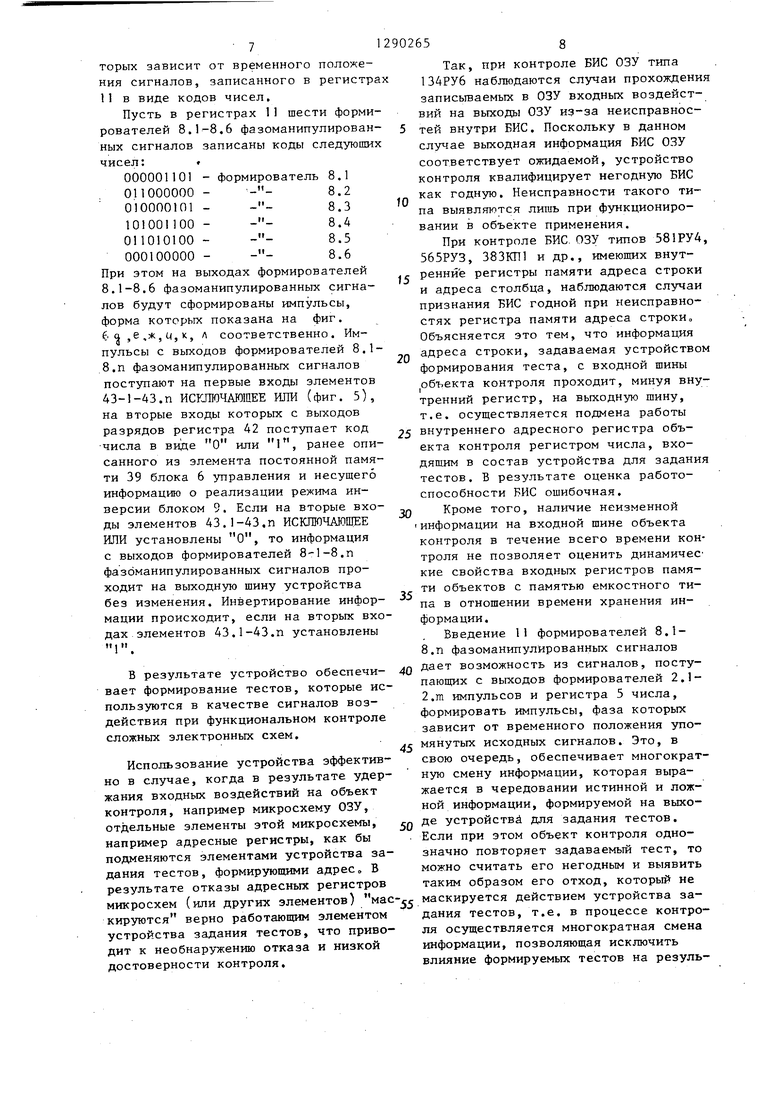

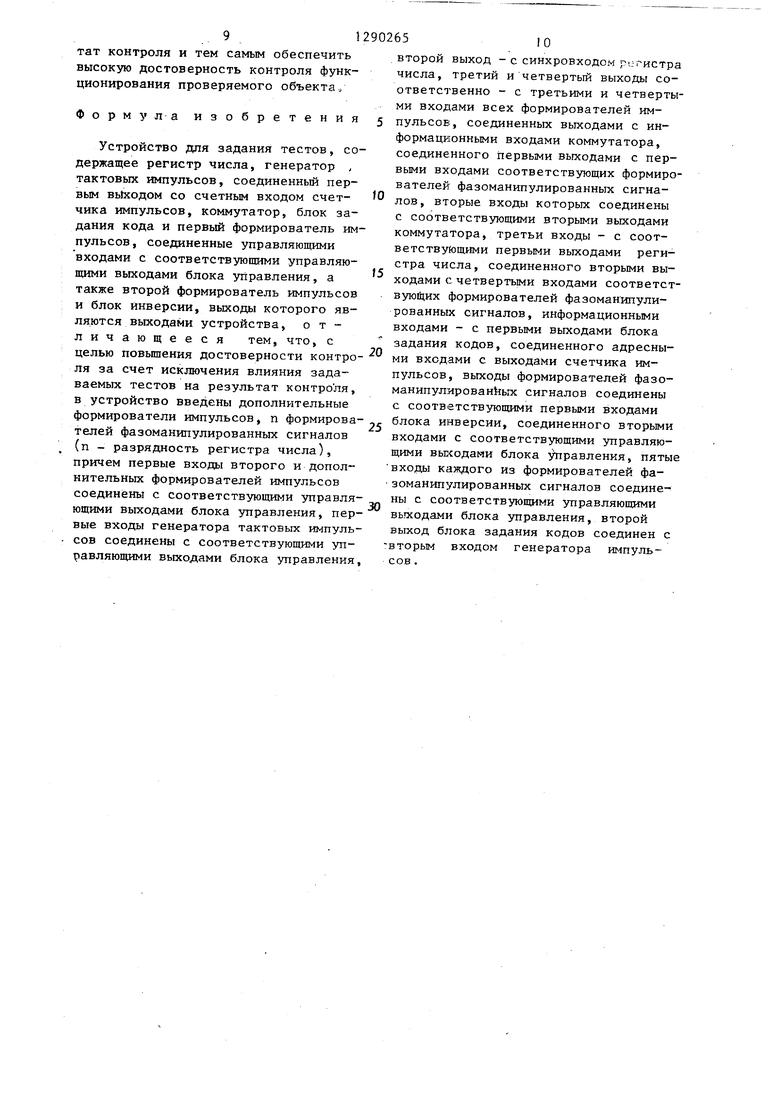

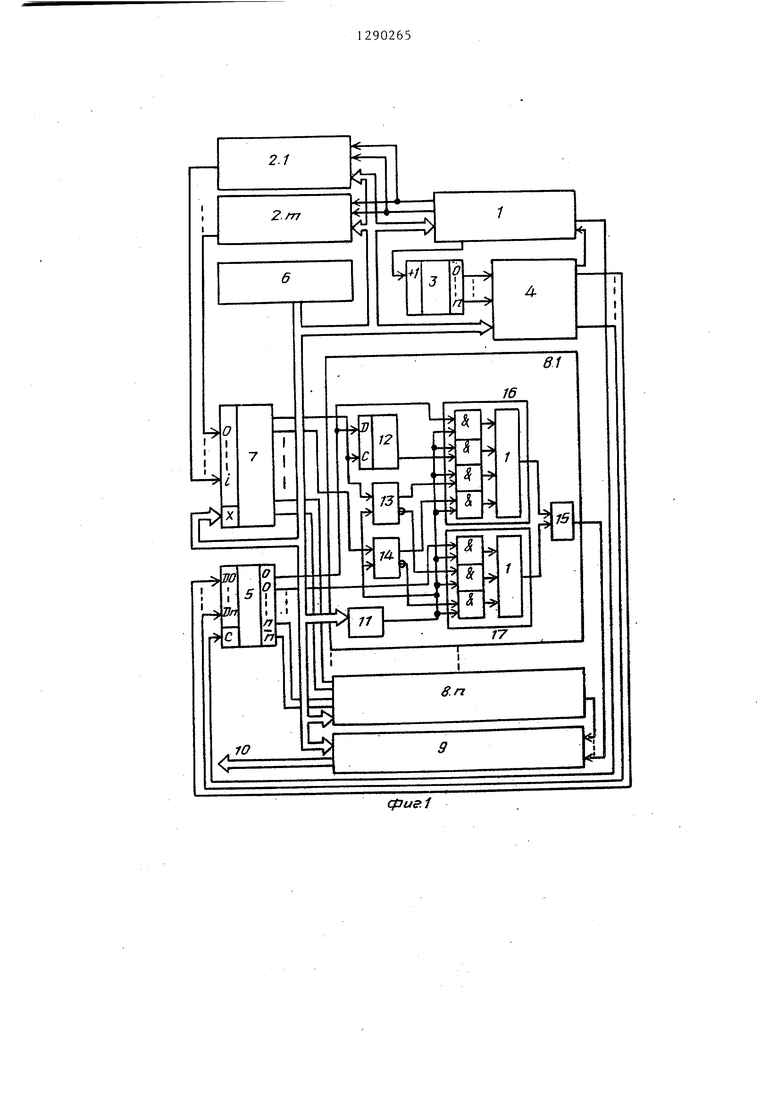

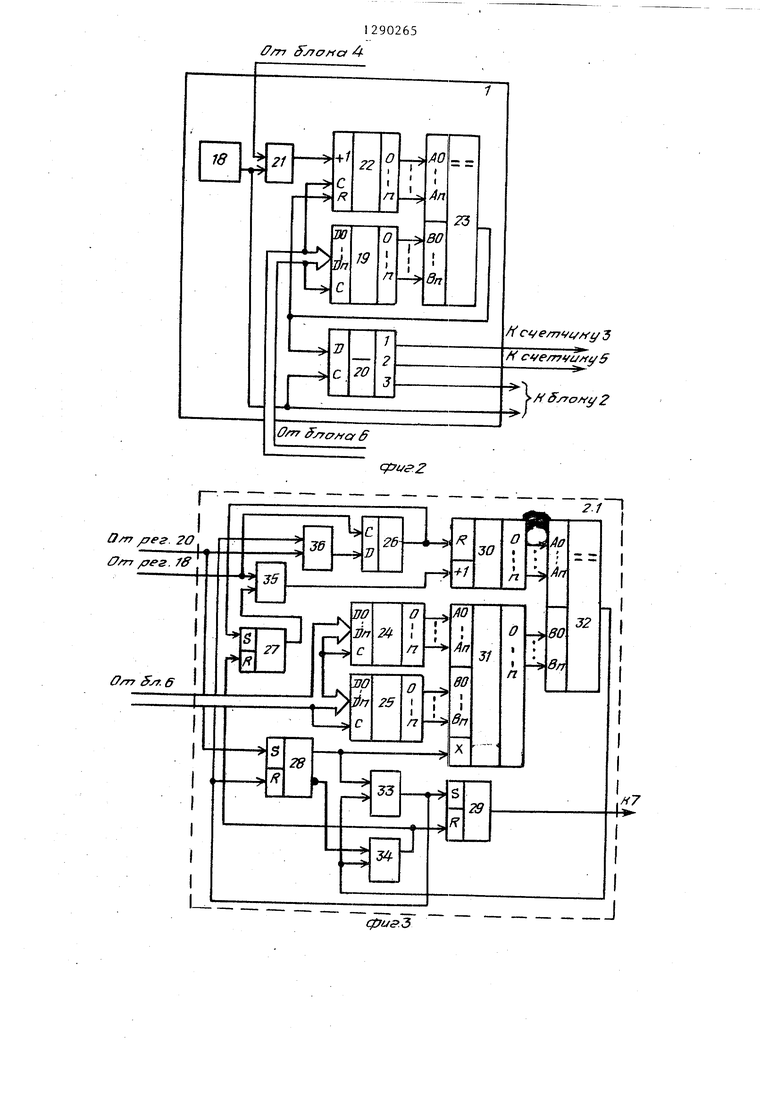

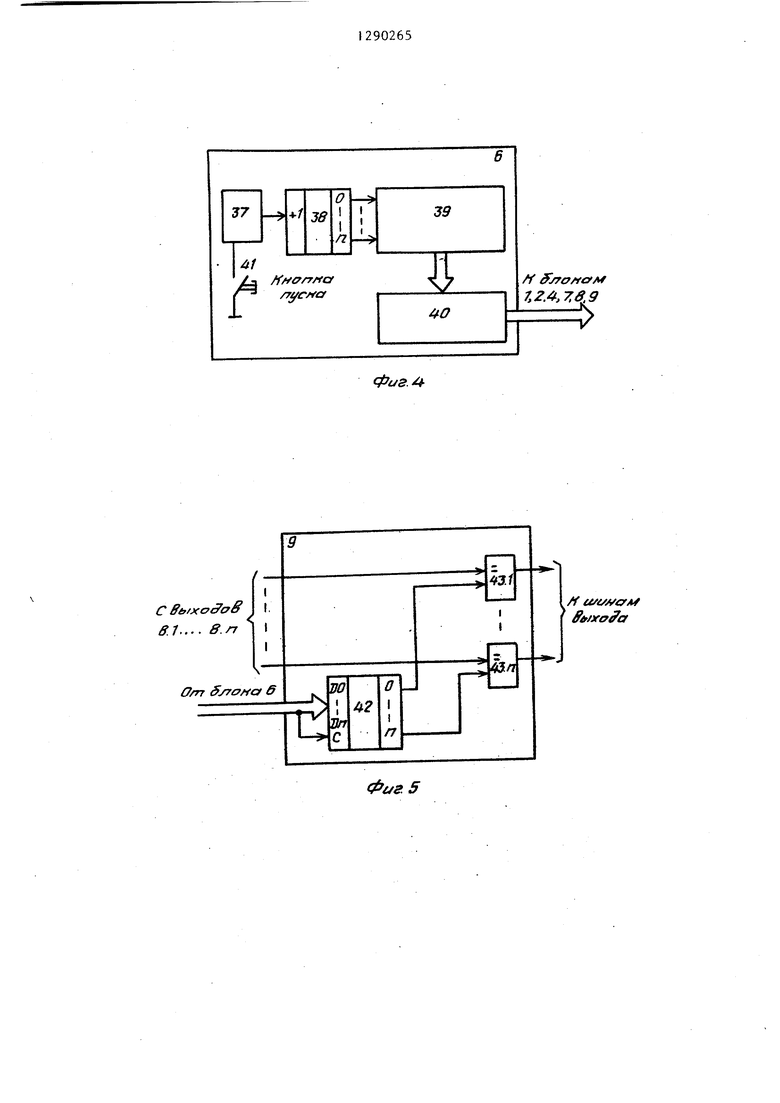

На фиг. 1 приведена схема устройства; на фиг, 2 - то же, генератора тактовых импульсов; на фиг. 3 - то же, формирователя импульсов; на фиг. 4 - то же, блока управления; на фиг. 5 - то же, блока инверсий; на фиг. 6 - временные диаграммы., поясняющие работу устройства.

Устройство {фиг. 1) содержит генератор 1 тактовых импульсов, первый 2.1, второй 2.2 и дополнительные 2.3-2.га формирователи импульсов, счетчик импульсов 3, блок 4 задания кода, регистр 5 числа, блок 6 управления, первый коммутатор 7, формирователи 8.1-8.П фазоманипулированных сигналов, блок инверсий 9, выходную шину 10.

Формирователь 8.1 фазоманипулиро- ванного сигнала (фиг. 1) содержит первьш регистр-11, первый D-триггер 12, первый 13, второй 14 и третий 15 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первьй 16 и второй 17 элементы 2И-ИЛИ.

Генератор тактовых импульсов (фиг. 2) содержит генератор 18 эталонной частоты, второй регистр 19, сдвиговый регистр 20, первый элемент 21 И, счетчик 22 и первый цифровой компаратор 23.

Формирователь 21 импульсов(фиг„ 3) содержит третий 24 и четвертый 25 регистры, второй D-триггер 26, первый 27, второй 28 и третий 29 R-S- триггеры, третий счетчик 30, второй коммутатор 31, второй цифровой компаратор 32, второй 33, третий 34 и четвертый 35 элементы И, элемент 36 ИЛИ.

Блок 6 управления (фиг. 4) содержит генератор-37 импульсов, четвертый счетчик 38, элемент 39 постоянной памяти, элемент 40 согласования кнопку 41.

Блок 9 инверсный (фиг. 5) содержит пятый регистр 42, четвертые элементы 43.1-43.П ИСКЛЮЧАЮЩЕЕ ИЛИ.

Генератор 1 тактовых импульсов предназначен для формирования такто™

25

902652

вых импульсов для счетчика 3 и синх- ронизируищих импульсов для формирователей 2.1-2.т импульсов и регистра 5 числа.

5 Формирователи .т импульсов предназначены для выработки управляющих импульсов с заданными временными параметрами (задержка, длительность Д.ПЯ формирователей 8.1-8„п

О фазоманипулированных сигналов. Количество m формирователей 2.1-2.т импульсов определяется необходимым количеством управляющих и синхронизирующих ш пульсов для осуществления

процесса контроля. Так, в рассматриваемом примере для контроля БИС ОЗУ типа К581РУ4 необходимо 8 формирователей импульсов.

Счетчик 3 служит для формирования

адресов для блока 4 задания кода и представляет собой двоичньш 10-разрядный счетчик, выполненный на трех микросхемах K500PiE136.

Блок 4 задания кода предназначен для формирования импульсных последовательностей с заданным чередованием логических 1 и О, т.е требуемых тестов для проверки определен- ных функций объекта контроля. Длина тестов определяется объемом проверки. Блок 4 задания кода представляет собой п-разрядное оперативное запоминающее устройство (ОЗУ), выполненное на микросхемах К500РУ415.

3-5 Регистр 5 числа предназначен для записи и временного хранения информации, формируемой блоком 4 задания кода, и передачи ее (информации) в формирователи 8.1-8.П фазоманипулированных сигналов по сигналам синхронизации, постзшающим с выхода сдвигового регистра 20 генератора 1 тактовых импульсов. Регистр 5 числа представляет собой п-разрядный регистр (п определяется количеством вьшодов контролируемого объекта), выполненный на микросхемах К500та213. В рассматриваемом примере применены 64 названные микросхемы для организации

128-разрядного регистра 5 числа.

Блок 6 управления служит для информации работы узлов устройства в процессе формирования испытательных тестов-сигналов воздействия для объ40

55

екта контроля.

Коммутатор 7 предназначен для трансляции выходных импульсов с формирователей 2.1-2.т импульсов на

312902

входы формирователей 8,1-8.п по командам с блока 6 управления. Коммутатор вьшолиеи на мультиплексорах (128 микросхем К150КП163)о

Формирователи 8.1-8.П фазоманршу- лированных сигналов служат для выработки (по командам с блока 6 уп

равления импульсов, фаза которых зависит от временного положения сигналов, поступающих с выходов блока 6 управления. Регистр 11 каждого из формирователей служит для приема и временного хранения информации о временных соотношениях фазоманипули- рованного сигнала, поступающей из блока 6 управления, и передачи этой информации в блоки 12, 13, 14, 16 и 17, Регистр 11 представляет собой 9-разрядный регистр памяти, выполненный на трех микросхемах К500ЛП129.

D-триггер 12 предназначен для сдвига по времени информации, поступающей с регистра 5 числа, на интервал времени, задаваемый одним из формирователей импульсов блока 2, выбранным посредством коммутатора 7. D-триггер 12 выполнен на микросхемах К500ТМ231, Логические элементы 13 и 14 ИСКЛЮЧАЮЩЕЕ ИЛИ служат для формирования инвертированных и неинвертированных сигналов, обеспечивающих выработку фазоманипулированных сигналов. Элемент 15 ИСКЛЮЧАЮЩЕЕ ИЛИ предназначен для сравнения сигналов, поступающих с выходов элементов 16 и 17 2И-ИЛИ и окончательного формирования (по результатам сравнения) фа- зоманипулированного сигнала. Элементы 16 и 17 2И-Ш1И служат для пропускания сигналов с выходов регистра 5 числа и коммутатора 7 на входы элемента 15 ИСКЛЮЧАЮЩЕЕ ИЛИ по сигналам разрешения с выхода регистра 11. Элементы 13, 14 и 15 вьтолнены на микросхемах К500ЛП107, элементы 16 и 17 - на двух микросхемах К500ЛК121.

Блок 9 инверсии служит для формирования инвертированных импульсов из фазоманипулированных сигналов форми- рователей 8.1-8,п по сигналам управления из блока 6. Коммутатор 31 выполнен на микросхеме К500ЛК107, цифровой компаратор 32 на микросхеме К500ЛМ102.

Генератор 37 импульсов служит для формирования счетных импульсов, подаваемых на счетчик 38, предназначенW

(5

0

ньш для формирования адреса элемента 39.

Элемент 39 постоянной памяти предназначен для хранения программы контроля и передачи ее через элемент 40 согласования в блоки 1, 2, 4, 7, 8.1-8,п и.9, Элемент 39 представляет собой 32-разрядную память глубиной 64К, выполненную на микросхемах К57ХРФЗ.

Элемент 40 согласования представляет собой стандартные канальные приемопередающие устройства с дешифраторами (микросхемы серии К559И11)о

Устройство (фиг. 2) работает следующим образом, I

При нажатии кнопки 41 блока 6 управления (фиг. 4) осуществляется за- 0 пуск генератора 37 импульсов, и счетчик 38 производит выбор адресов элемента 39 постоянной памяти. Через элемент 40 согласования в регистры памяти узлов и блоков устройства за- 5 носится информация о параметрах формируемых тестов. В регистр 19 генератора 1 тактовых импульсов записьгоа- ется информация о длительности периода следования тактовых импульсов, 0 обеспечивающих заданную частоту формируемых тестов, в регистры 24 и 25 формирователей импульсов 2.1-2.т заносится информация о величинах задержки и длительности формируемых с импульсов о В ячейки оперативной

памяти блока 4 задания кода заносятся данные, необходимые для формирования тестов (импульсных последовательностей), которые используются в качесто ве входных воздействий для контролируемых БИС, на управляющие входы коммутатора 7 поступает информация о по- следовательности подключения вькодов формирователей 2.1-2.т импульсов к 5 входам формирователей 8.1-8.П фазоманипулированных сигналов, в регистры 11 формирователей 8.1-8.П записывается информация о временных соотношениях фазоманипулированных сигналов, в регистр 42 блока 9 инверсий поступает информация о реализации режима инверсии выходной информации с формирователей 8.1-8.п. По окончании процесса записи информации с выхода блока 4 задания кода на вход элемента 21 И генератора 1 тактовых импульсов (фиг. 2) поступает сигнал разрешения на прохождение импульсов с -выхода генератора 18 эталонной

5

частоты на вход счетчика 22, на выходах разрядов которого устанавливается п-разрядный код, поступающий на цифровой компаратор 23, где сравнивается с кодом, записанным в регистре 19. При равенстве кодов цифровой компаратор 23 формирует импульс, который поступает на вход сброса счетчика 22 и информационный вход сдвигового регистра 20, на синхронизирующий вход которого приходят импульсы с генератора 18 эталонной частоты. На выходе сдвигового регистра 20 формируются тактовые импульсы для блока 2 формирователей импульсов, счетчика 3 и регистра 5 числа. По приходу тактового импульса с выхода сдвигового регистра 20 генератора 1 (фиг. 6q, момент времени t) на S-вхо триггера 28 и первый вход элемента 36 ИЛИ блока 2 (фиг. З) осуществляется перевод каждого из формирователей 2.1-2.т импульсов в режим формирования переднего фронта импульса (задержки). При этом на прямом выходе триггера 28 устанавливается уровень логической I, а на инверсном - О Сигнал 1 поступает на управляющий

вход коммутатора 31, разрешая прохождение через него информации с выхода регистра 24 на входы цифрового компаратора 32. По приходу импульса с генератора 18 эталонной частоты блока 1 на S-вход триггера 26 и элемент 35 И происходит сброс счетчика 30 и установка триггера 27 в состояние, при котором на его выходе устанавливается 1, поступающая на второй вход элемента 35 и разрещающая прохождение через него тактовых импульсов с выхода генератора 18 эталонной частоты блока I на счетный вход счетчика 30 блока 2 (фиг. 1). На выходе счетчика 30 устанавливается п-разрядный код, поступающий на другую группу входов цифрового компаратора 32, где происходит сравнение его (кода) с выходной информацией регистра 24, прошедщей через коммутатор 31. При

равенстве кодов на выходе цифрового компаратора 32 формируется импульс который поступает на первые входы логических элементов 33 и 34 И. Так как На втором входе элемента 33 И установлена 1 (с прямого выхода триггера 28), то импульс с выхода цифрового компаратора 32 проходит через элемент 33 И на входу тригге

0

5

ров 28 и 29 и элемента 36 ИЛИ. При этом триггер 28 изменяет свое состояние, на его прямом выходе устанавливается О, а на инверсном - 1, разрешающая прохождение информации через элемент 34 И в режиме формирования заднего фронта импульса (длительности) , происходящего описанным образом с той лищь разницей, что вместо регистра 24 работает регистр 25.- Передний и задний фронты импульса фиксируются триггером 29. На фиг. 65 и В показаны сигналы на выходе триггеров 29 формирователей 2.1, 2.J импульсов. Передний фронт импульса на выходе формирователя 2.i сформирован в момент времени t с задержкой с, а передний фронт на выходе формирователя 2j - в момент времени tj с задержкой o-j. Задние фронты этих импульсов формируются в моменты времени t, t соответственно. Таким об5

0

0

разом, на выходе триггера 29 формирователя 21 импульсов сформирован импульс длительностью Г я на выходе триггера 29 формирователя 2 - импульс длительностью С, . Аналогичным образом на выходах остальных формирователей 2. 1-2 .т импульсов формируются импульсы с заданными значениями задержки и длительности.

С выхода сдвигового регистра 20 генератора I тактовых импульсов (фиг. 2)|. импульсы поступают на вход счетчика 3 j

5 (фиг. 1)., который осуществляет выбор адресов ячеек оперативной памяти блока 4 задания кода, информация с выходов которого поступает на входы регистра 5 числа и переписьюaeTCji в него по приходу тактовых импульсов с генератора 1. Выходная информация регистра 5 числа .(фиг. 6) с прямых выходов поступает на информационные входы триггеров 12 и элемент 16 2И5 ИЛИ, входящих в состав формирователей 8.1-8,п фазоманипулированных сигналов . Информация с инверсных выходов регистра 5 числа подается на элемент 17 2И-ИЛИ. На синхронизирующие входы

0 триггеров 12 и первые входы элементов 13 ИС:КШ)ЧА1(ЩЕЕ ИЛИ через коммутатор 7 проходит информация с выхода формирователя 21 импульсов, а на первые входы элементов 14 ИСКЛЮЧАЮЩЕЕ

ИЛИ - информация с выхода формирователя 2j И1чпульсов (1 1, j 2).

В формирователях 8.1-8.п происходит формирование импульсов, фаза коформирователь 8,

.

торых зависит от временного положения сигналов, записанного в регистрах 11 в виде кодов чисел.

Пусть в регистрах 11 шести формирователей 8.1-8,6 фазоманипулирован- ных сигналов записаны коды следующих чисел:

000001101

011000000

010000101

101001100

011010100

000100000 При этом на выходах формирователей 8.1-8.6 фазоманипулированных сигналов будут сформированы импульсы, форма которых показана на фиг. 6 ,,Ц,, л соответственно. Импульсы с выходов формирователей 8.1- 8.П фазоманипулированных сигналов поступают на первые входы элементов 43-1-43.П ИСКЛЮЧАЮЩЕЕ ИЛИ (фиг. 5), на вторые входы которых с выходов разрядов регистра 42 поступает код числа в виде О или I, ранее описанного из элемента постоянной памяти 39 блока 6 управления и несущего информацию о реализации режима инверсии блоком 9. Если на вторые входы элементов 43.1-43,п ИСКЛЮЧАЮЩЕЕ ИЛИ установлены О, то информация с выходов формирователей 8-1-8.П фазоманипулированных сигналов проходит на выходную шину устройства без изменения. Инвертирование информации происходит, если на вторых входах элементов 43,1-43,п установлены IIIII

В результате устройство обеспечивает формирование тестов, которые используются в качестве сигналов воздействия при функциональном контроле сложных электронных схем.

Использование устройства эффективно в случае, когда в результате удержания входных воздействий на объект контроля, например микросхему ОЗУ, ,ельные элементы этой микросхемы, например адресные регистры, как бы подменяются элементами устройства задания тестов, формирующими адрес, В результате отказы адресных регистров

Ю

15

20

Так, при контроле БИС ОЗУ типа 134РУ6 наблюдаются случаи прохождени записываемых в ОЗУ входных воздействий на выходы ОЗУ из-за неисправностей внутри БИС, Поскольку в данном случае выходная информация БИС ОЗУ соответствует ожидаемой, устройство контроля квалифицирует негодную БИС как годную. Неисправности такого типа выявляются лишь при функционировании в объекте применения.

При контроле БИС. ОЗУ типов 581РУ4 565РУЗ, 383КП и др., имеющих внутренние регистры памяти адреса строки и адреса столбца, наблюдаются случаи признания БИС годной при неисправностях регистра памяти адреса строки о Объясняется это тем, что информация адреса строки, задаваемая устройство формирования теста, с входной шины объекта контроля проходит, минуя вну тренний регистр, на выходную шину, т.е. осуществляется подмена работы 25 внутреннего адресного регистра объекта контроля регистром числа, входящим в состав устройства для задани тестов. В результате оценка работоспособности БИС ошибочная.

Кроме того, наличие неизменной информации на входной шине объекта контроля в течение всего времени кон троля не позволяет оценить динамичес кие свойства входных регистров памяти объектов с памятью емкостного типа в отношении времени хранения информации.

Введение 11 формирователей 8,1- 8,п фазоманипулированных сигналов дает возможность из сигналов, посту- паюших с выходов формирователей 2,1- 2.т импульсов и регистра 5 числа, формировать импульсы, фаза которых зависит от временного положения упо- мянутых исходных сигналов. Это, в

свою очередь, обеспечивает многократную смену информации, которая выражается в чередовании истинной и ложной информации, формируемой на выходе устройств для задания тестов. Если при этом объект контроля однозначно повторяет задаваемый тест, то можно считать его негодным и выявить таким образом его отход, который ие

30

35

40

50

микросхем (или других элементов) мас- маскируется действием устройства закируются верно работающим элементом устройства задания тестов, что приводит к необнаружению отказа и низкой достоверности контроля.

Дания тестов, т,е, в процессе контроля осуществляется многократная смена информации, позволяющая исключить влияние формируемых тестов на резульЮ

5

0

Так, при контроле БИС ОЗУ типа 134РУ6 наблюдаются случаи прохождения записываемых в ОЗУ входных воздействий на выходы ОЗУ из-за неисправностей внутри БИС, Поскольку в данном случае выходная информация БИС ОЗУ соответствует ожидаемой, устройство контроля квалифицирует негодную БИС как годную. Неисправности такого типа выявляются лишь при функционировании в объекте применения.

При контроле БИС. ОЗУ типов 581РУ4, 565РУЗ, 383КП и др., имеющих внутренние регистры памяти адреса строки и адреса столбца, наблюдаются случаи признания БИС годной при неисправностях регистра памяти адреса строки о Объясняется это тем, что информация адреса строки, задаваемая устройством формирования теста, с входной шины объекта контроля проходит, минуя внутренний регистр, на выходную шину, т.е. осуществляется подмена работы 5 внутреннего адресного регистра объекта контроля регистром числа, входящим в состав устройства для задания тестов. В результате оценка работоспособности БИС ошибочная.

Кроме того, наличие неизменной информации на входной шине объекта контроля в течение всего времени контроля не позволяет оценить динамичес кие свойства входных регистров памяти объектов с памятью емкостного типа в отношении времени хранения информации.

Введение 11 формирователей 8,1- 8,п фазоманипулированных сигналов дает возможность из сигналов, посту- паюших с выходов формирователей 2,1- 2.т импульсов и регистра 5 числа, формировать импульсы, фаза которых зависит от временного положения упо- мянутых исходных сигналов. Это, в

свою очередь, обеспечивает многократную смену информации, которая выражается в чередовании истинной и ложной информации, формируемой на выходе устройств для задания тестов. Если при этом объект контроля однозначно повторяет задаваемый тест, то можно считать его негодным и выявить таким образом его отход, который ие

0

5

0

0

Дания тестов, т,е, в процессе контроля осуществляется многократная смена информации, позволяющая исключить влияние формируемых тестов на результат контроля и тем самым обеспечить высокую достоверность контроля функционирования проверяемого объекта/

Формула изобретения 5

Устройство для задания тестов, содержащее регистр числа, генератор , тактовых импульсов, соединенный первым вь1ходом со счетным входом счетчика импульсов, коммутатор, блок задания кода и первый формирователь импульсов , соединенные управляющими входами с соответствующими управляющими выходами блока управления, а также второй формирователь импульсов и блок инверсии, выходы которого являются выходами устройства, отличающееся тем, что, с целью повышения достоверности контро ля за счет исключения влияния задаваемых тестов на результат контроля.

второй выход - с синхровходом регистра числа, третий и четвертый выходы соответственно - с третьими и четвертыми входами всех формирователей импульсов, соединенных выходами с информационными входами коммутатора, соединенного первыми выходами с первыми входами соответствующих формирователей фазоманипулированных сигналов, вторые входы которых соединены с соответствующими вторыми выходами коммутатора, третьи входы - с соответствующими первыми выходами регистра числа, соединенного вторыми выходами с четвертьми входами соответствующих формирователей фазоманипулированных сигналов, информационными входами - с первыми выходами блока задания кодов, соединенного адресными входами с выходами счетчика импульсов, выходы формирователей фазо- манипулированЬых сигналов соедршены с соответствующими первыми входами

в устройство введены дополнительные формирователи импульсов, п формирова-- блока инверсии, соединенного вторыми телей фазоманипулированных сигналов входами с соответствующими управляю- (п - разрядность регистра числа), щими вькодами блока управления, пятые причем первые входь второго и дополнительных формирователей импульсов соединены с соответствующими управляющими выходами блока управления, первые входы генератора тактовых импульсов соединены с соответствующими управляющими выходами блока управления.

X

входы каждого из формирователей фа- зоманипулированных сигналов соедине- ны с соответствующими управляющими выходами блока управления, второй выход блока задания кодов соединен с вторым входом генератора импульсов .

Ю

5

15

20

второй выход - с синхровходом регистра числа, третий и четвертый выходы соответственно - с третьими и четвертыми входами всех формирователей импульсов, соединенных выходами с информационными входами коммутатора, соединенного первыми выходами с первыми входами соответствующих формирователей фазоманипулированных сигналов, вторые входы которых соединены с соответствующими вторыми выходами коммутатора, третьи входы - с соответствующими первыми выходами регистра числа, соединенного вторыми выходами с четвертьми входами соответствующих формирователей фазоманипулированных сигналов, информационными входами - с первыми выходами блока задания кодов, соединенного адресными входами с выходами счетчика импульсов, выходы формирователей фазо- манипулированЬых сигналов соедршены с соответствующими первыми входами

- блока инверсии, соединенного вторыми входами с соответствующими управляю- щими вькодами блока управления, пятые

блока инверсии, соединенного вторыми входами с соответствующими управляю- щими вькодами блока управления, пятые

входы каждого из формирователей фа- зоманипулированных сигналов соедине- ны с соответствующими управляющими выходами блока управления, второй выход блока задания кодов соединен с вторым входом генератора импульсов .

сриг.1

Л 5

/У c e/r7ViJ/ft/5

}

Г

дуиг2

фис.3

I

Cffb/xot aS .

8.1.... 8.ГГ I I

O/rr Syrey/ a 6

JN V

w

mn

Фиг.

4J.1

/f u/t///ar4f ffit/3fo a

45/

Фиг 5

г в

ж

3

и н л

Составитель Н, Главизнина Редактор А, Гулько Техред Л. Сердюкова Корректоре. Шекмар

Заказ 7899/44 Тираж 864Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

фс/е.6

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1981 |

|

SU957279A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для контроля цифровыхОб'ЕКТОВ | 1978 |

|

SU798844A1 |

| Устройство для задания тестов | 1982 |

|

SU1096612A2 |

| Устройство для автоматического контроля больших интегральных схем | 1984 |

|

SU1205083A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для ввода информации | 1988 |

|

SU1580339A1 |

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля и диагностики цифровых устройств, на;пример БИС ОЗУ. Цель изобретения - повышение достоверности контроля за счет исключения влияния задаваемых тестов на результат контроля. Устройство содержит генератор тактовых импульсов, формирователи импульсов, счетчик, блок задания кодов, регистр числа, блок управления, коммутатор, формирователи фазоманипулированных сигналов За счет введения дополнительных формирователей импульсов и формирователей фазоманипулированных сигналов устройство обеспечивает многократную смену информации на тестируемом объекте, что позволяет исключить влияние задаваемых тестов на результат контроля и тем самым обеспечить более высокую достоверность контроля. 6 ил. i (Л С

| Устройство для задания тестов | 1981 |

|

SU1038926A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для задания тестов | 1982 |

|

SU1096612A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-02-15—Публикация

1985-08-13—Подача