1098036

2. Устройство по П.1, о т л и- вторые входы элементов ИСКЛЮЧАЮЩЕЕ

чающееся тем, что блок группы соединены через регистр

Iобразования адреса содержит регистрс группой управляющих входов блока,

и группу элементов ИСКЛЮЧАКЯЦЕЕ ИЛИ,выходы элементов ИСКЛЮЧАЮЩЕЕ ШТИ

первые входы которых соединены с груп-образуют группу вькодов блопой информационных входов блока,ка«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для взаимного установления подлинности абонентов | 1986 |

|

SU1442993A1 |

| Устройство для контроля программ | 1983 |

|

SU1136172A1 |

| Устройство для считывания и отображения графической информации | 1986 |

|

SU1506459A1 |

| Оперативное запоминающее устройство с защитной информации | 1976 |

|

SU590833A1 |

| Устройство для параллельного формирования адресов | 1987 |

|

SU1418711A1 |

| Устройство для защиты памяти | 1988 |

|

SU1509910A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1287156A1 |

| УСТРОЙСТВО ОБРАБОТКИ ДВУХМЕРНЫХ И ТРЕХМЕРНЫХ ИЗОБРАЖЕНИЙ | 2005 |

|

RU2289161C1 |

| Многомерный статистический анализатор | 1984 |

|

SU1241259A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

1. УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ, содержащее два регистра, два сумматора и элемент ИЛИ, первый и второй входы которого соединены соответственно с выходами переноса первого и второго сумматоров, первые группы информационньЕХ входов первого и второго сумматоров соединены соответственно с группами выходов первого и второго регистров, группы входов которых соединены соответственно с первыми и вторыми группами информационных входов устройства, выход элемента ИЛИ соединен с выходом устройства, отличающеес я тем, что, с целью сокращения оборудования, в него введен блок преобразования адреса, группа информационных входов которого соединена с третьей группой информационных входов устройства, группа ynfJaBkn ляющих входов блока преобразования адреса соединена с группой управляющих входов устройства, группа выходов блока преобразования адреса соединена со вторыми группами информационных входов первого и второго сумматоров. со эо о со О5

Изобретение относится к запоминающим устройствам и может быть использовано, в частности, в информационно-управлякнцих системах, работающих в реальном масштабе времени.

Известно устройство для запщты памяти, содержащее граничные регистры и компараторы для сравнения кода исполнительного адреса с кодами адресов, установленными в этих регистрах П ,1.

Недостатками этого устройства являются высокая сложность реализации и низкое быстродействие при одновременной защите нескольких несмежных областей памяти, так как в этом случ-ае требуется. установка дополнительных пар регистров по числу защищаемых областей памяти и время на запись в них граничных адресов.

Наиболее близким техническим решением к предлагаемому является устройство для защиты памяти, содержащее регистры верхней и нижней границ, первый и второй сумматоры, элемент ИЛИ, причем выход регистра верхней границы соединен с первым входом первого сумматора, второй вход которого соедииен с вторым входом второго сумматора и с первым входом устрой ства, выход регистра нижней границы соединен с первым входом второго сумматора, выход которого соединен с вторым входом элемента ИЛИ, первый вход которого соединен с выходом первого сумматора, а выход является выходом устройства, выходы регистров верхней и нижней границ являются соответствен но вторым и третьим входами устройства 2.

Недостатком известного устройства является большое количество оборудования, требующееся при защите одиовременно нескольких несмежных областей памяти, так как в этом случае требуется несколько пар граничньпс регистров.

Цель изобретения - сокращение оборудования .

Указанная цель достигается тем, что в устройство для защиты памяти, содержащее два регистра, два сумматора и элемент ИЛИ, первый и второй входы которого соединены соответственно с выходами переноса первого и второго сумматоров, первые группы информационных входов первого и второго сумматоров соединены соответственно с группами выходов первого и второго регистров, группы входов которых соединены соответственно с первыми и вторыми группами информационных входов устройства, выход элемента ИЛИ соединен с выходом устройства, введен блок преобразования адреса, группа информационных входов которого соединена с третьей группой информационных входов устройства, группа управляющих входов блока преобразования адреса соединена с группой управляющих входов устройства, группа выходов блока преобразования адреса соединена с вторыми группами информационных входов первого и второго сумматоров.

Кроме того, блок преобразования адреса содержит регистр и группу элементов ИСКПЮЧАКЯЦЕЕ ИЛИ, первые входы которых соединены с группой информационных входов блока, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЖ группы соединены через регистр с группой управляющих входов блока, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ образуют группу выходов блока.

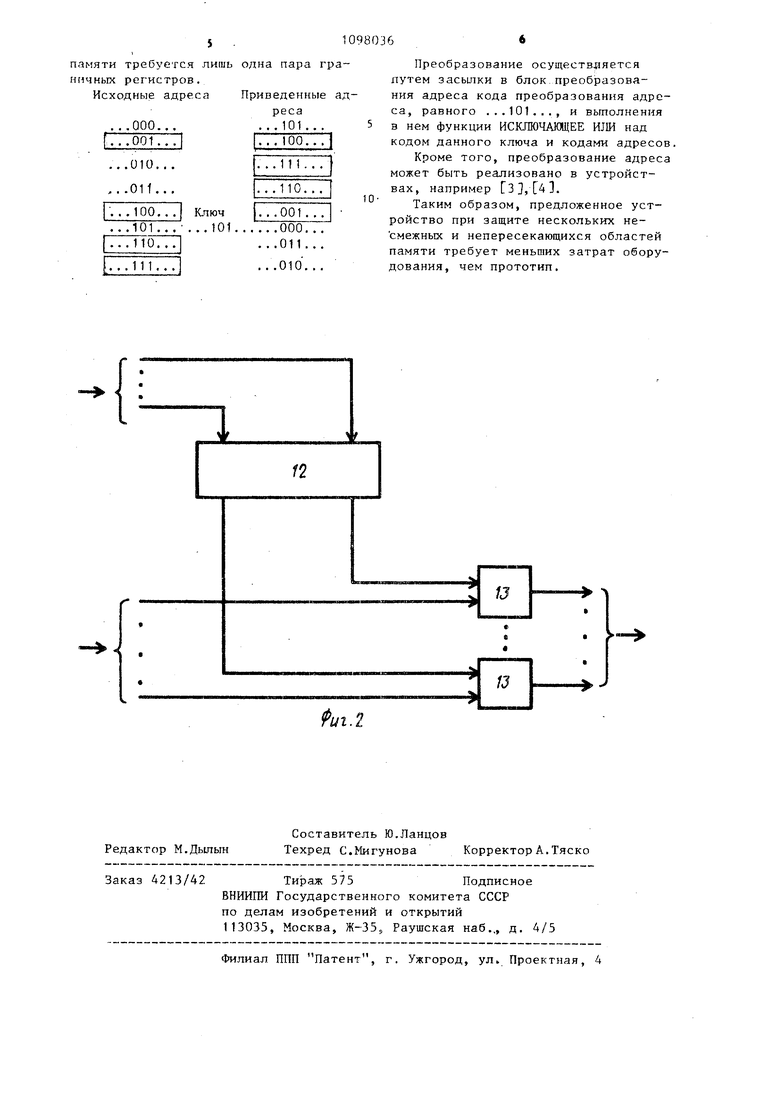

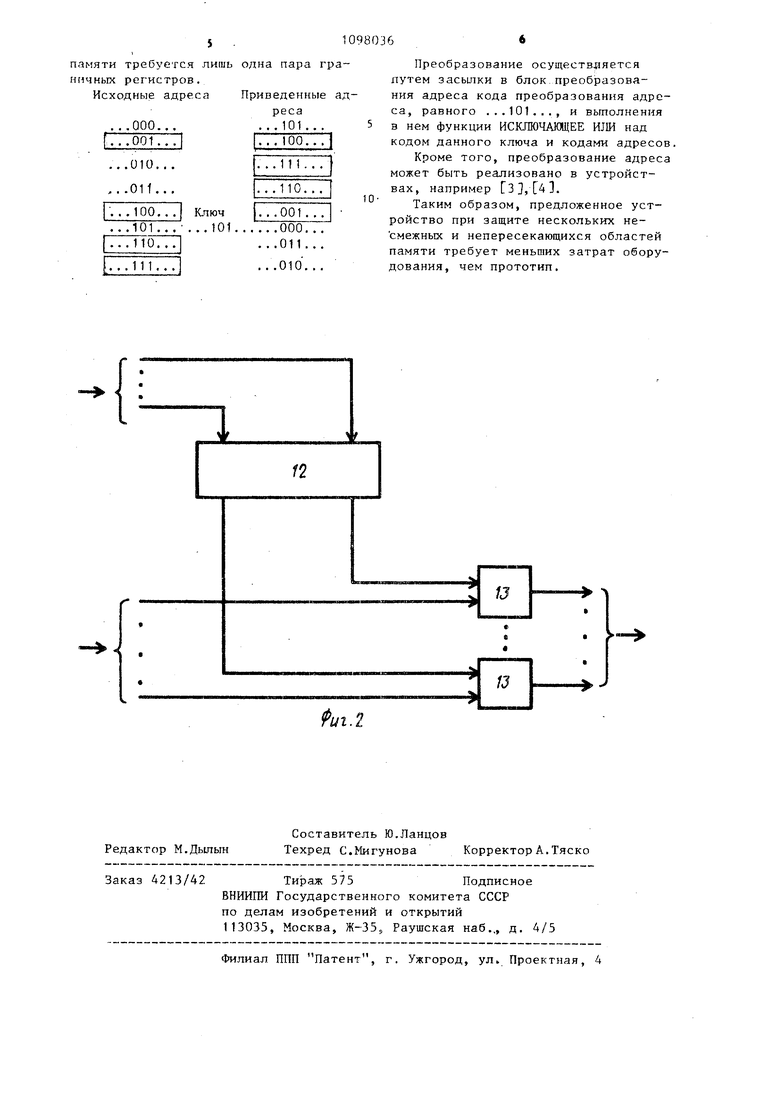

В результате преобразования адресов несмежных и непересекающихся областей памяти в адреса смежных ил пересекающихся областей памяти суще вует возможность приведения несколь ких несмежных и непересекающихся областей памяти к одной области, им ющей две границы - верхнюю и нижнюю позволяя тем самым использовать для защиты одновременно нескольких несмежных и непересекающихся участков памяти одну пару граничных регистров. На фиг.1 изображена структурная схема предложенного устройства для защиты памяти, на фиг.2 - функциональная схема блока преобразования адреса. Устройство содержит (фиг.1) блок преобразования адреса 1, первьш 2 и второй 3 регистры, первый 4 и вто рой 5 сумматоры, элемент ИЛИ 6,первую группу 7 информационных входов, группу 8 управляющих входов, третью 9 и вторую 10 группы информационных входов и выход 11. в качестве блока преобразования адреса 1 может быть применено устройство,, содержащее (фиг.2) регистр 12 и группу элементов ИСКЛЮЧАЩЕЕ ИЛИ 13. Устройство работает следующим об разом. В исходном состоянии устройства регистры 2 и 3, а также регистр 12 находятся в нулевом состоянии. Пере началом выполнения некоторой программы в регистр 12 через группу 8 управляющих входов устройства заносится код ключа преобразования адре са, а в регистры 2 и 3 соответствен через группу входов 7 и группу вхо.дов 10 устройства - коды верхней и нижней границ приведенной области защиты яамяти. Приведенная область защиты памяти образуется всеми теми и только теми преобразованными в блоке 1 адресами, по которым разрешено обращение к памятидля данной программы. Образование приведенной области защиты памяти достигается тем, что адреса, по которым данной программе разрешено обращение в память и которые могут представлять собой несмежные и непересекающиеся области адресного пространства, при водятся к одной области путем преоб зования на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 13 в соответствии с ключом, записанным в регистре 12. При, выполне нии адрес обращения к пам ти поступает через .группу входов 9 устройства в блок преобразования адреса 1 напервые входы элементов ИСКЛЮЧАЮЩЕЕ ИЖ 13. Преобразованный в соответствии с алгоритмом преобразования и ключом преобразования адрес обращения с выхода блока преобразования адреса 1 поступает на вторые группы входов первого сумматора 4 и второго сумматора 5. Одновременно с этим с группы выходов регистра 2 на первую группу входов сумматора 4 поступает код верхней границы приведенной области защиты памяти, а с группы выходов регистра 3 на первую группу вkoдoв сумматора 5 - код нижней границы. Если адрес обращения больше верхней границы, с выхода переноса сумматора 4 на первый вход элемента ИЛИ 6 поступает сигнал переноса. Аналогично, если адрес обращения меньше нижней границы, с выхода переноса сумматора 5 на второй вход элемента ИЛИ 6 тоже поступает сигнал переноса. Появление одного из этих сигналов на входе элемента ИЛИ 6 вызывает появление сигнала на его выходе и, следовательно, на выходе 11 устройства, что свидетельствует о несанкционированном обращении в память по данному адресу. В противном случае сигнал на выходе 11 устройства отсутствует, что является свидетельством правильного обращения в память. Так, например, пусть некоторой программе разрешено обращение к участкам памяти с адресами ...00К,. ...100... ...110... ...111 ... Для исходного адресного пространства только два из этих участков являются смежными. Для защиты памятей с помощью «звестных устройств защит±1 по граничным регистрам потребовалось бы наличия трех пар граничных регистров или ограничения области памяти от адреса ...001... до адреса ...111..., куда вопши бы и запретные участки ...010.......011..., ,..101... С помощью предлагаемого устройства исходное адресное пространство может быть преобразовано, например, в следующее приведенное адресное пространство, где данные участки памяти являются смежными, а для защиты памяти требуется лишь одна пара г ничных регистров. Исходные адреса Приведенные реса ...000... oob..J ...000. .. ...011... ...010...

иг.2

0

13 Преобразование осуществ-ияется путем засылки в блок преобразования адреса кода преобразования адреса, равного ...101..., и выполнения в нем функции ИСКЛЮЧАЮЩЕЕ ИЛИ над кодом данного ключа и кодами адресов. Кроме того, преобразование адреса может быть реализовано в устройствах, например Г3),4. Таким образом, предложенное устройство при защите нескольких несмежных и непересекающихся областей памяти требует меньших затрат оборудования, чем прототип.

Авторы

Даты

1984-06-15—Публикация

1982-07-05—Подача