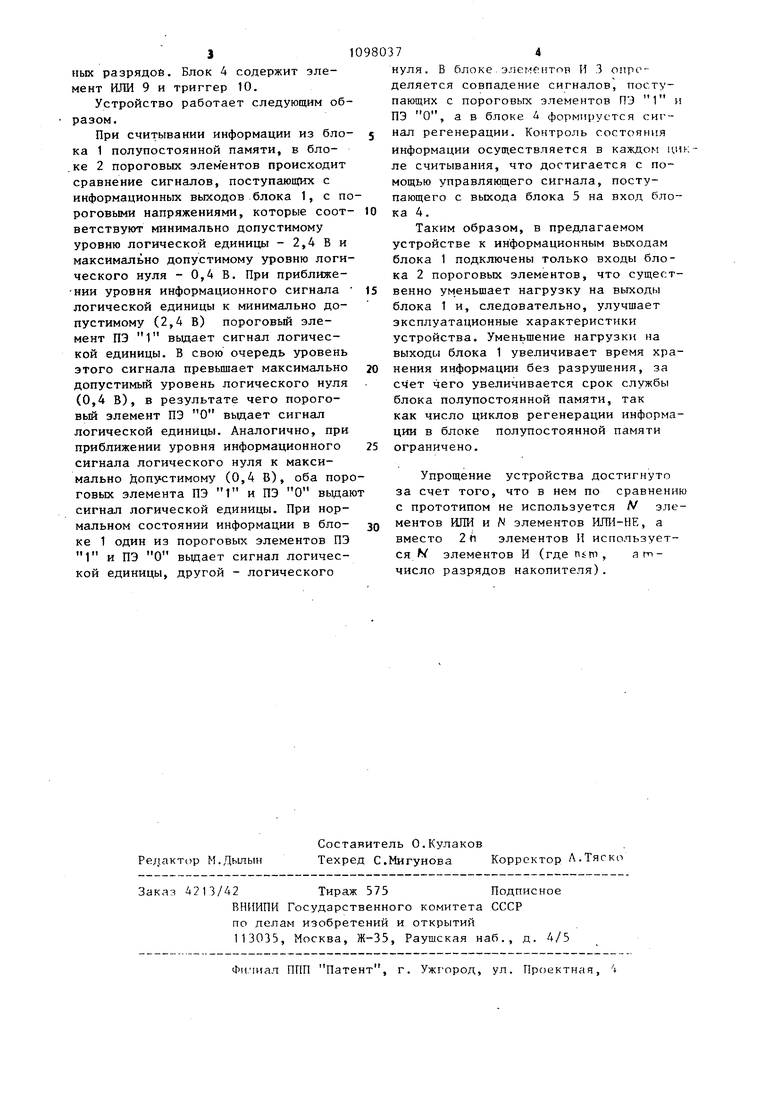

Изобретение oTiuictircfl к запоми-. нающим устройствам и предназначено для использования в вычислительной т нике . Известно запоминающее устройство с. регенерацией информации, содержаще счетчик, блок полупостоянной памяти подключенный к блоку управления и блоку коммутации напряжения питания В этом устройсЧве для формирования сигнала регенерации используется счетчик, максимальный результат счета которого соответствует максимальному интервалу времени хранения информации без ра рушения J. Однако это устройство характеризуется большим количеством оборудования, необходимого для выдачи сиг нала регенерации. Кроме того, при пропадании питания счетчик может терять свое состояние. Известно также запоминающее устройство, содержащее блок полупостоянной памяти, блок формирования сигнала регенерации, который состоит из датчика контрольного сигнала и по рогового элемента, блок управления, блок коммутации напряжения питания и источник питанияС2. В качестве датчика контрольного сигнала в этом устройстве используется контрольная ячейка памяти, аналогичная ячейкам, из которых сос тоит блок полупостоянной- памяти. Об ращение к контрольной ячейке происходит чаще, чем к любой из ячеек йлока полупостоянной памяти. За сче этого информация в контрольной ячейке должна разрушаться быстрее. По мере разрушения информации в кон рольной ячейке выдается сигнал регенерации. При этом состояние инфор мации в ячейках самого блока полупостоянной памяти не контролируется Это заведомо увеличивает частоту циклов регенерации.В случае более быстрого разрушения информации .в ка кой-либо из ячеек блока полупостоян ной памяти по сравнению с контрольной ячейкой может произойти потеря информации. Наиболее близким к изобретению является запоминающее устройство с регенерацией информации, содержащее накопитель, блок формирования сигнала регенерации, блок управления, подключенный к накопителю и блоку формирования сигнала регенерации, б пороговых элементов, входы которого подключены к выходам накопителя, блок анализа информации, входы которого подключены к выходам накопителя, а выходы - к входам блока формирования сигнала регенерацииГЗ. Известнй)е устройство характеризуется большим объемом оборудования, так как блок анализа информации содержит Г1 элементов ИЛИ и п элементов ИЛИ-НЕ (гдепгт , а m - число разрядов накопителя), а в блок формирования сигнала регенерации входят 2м элементов И. Кроме того, в этом устройстве увеличена нагрузка на информационные выходы накопителя, так как к ним подключены входы блока анализа и входы группы пороговых элементов, что ухудшает эксплуатационные характеристики устройства. Целью изобретения является упрощение устройства. Поставленная цель достигается тем, что в запоминающее устройство с регенерацией информации, содержащее накопитель, блок формирования сигнала регенерации, блок управления, подключенный к накопителю и блоку формирования сигнала регенерации, блок пороговых элементов, входы которого подключены к выходам накопителя, введен блок элементов И, входы которого подключены к выходам блока пороговых элементов, а выходы блока элементов И соединены с входами блока формирования сигнала регенерации. На чертеже изображена структурная схема предложенного устройства. Устройство содержит накопитель 1, например блок полупостоянной памяти, блок 2 пороговых элементов, блок элементов И 3, блок 4 формирования сигнала регенерации и блок 5 управления. Блок 2 составляют пороговые элементы ПЭ Г6иПЭ 0 7, предназначенные для сравнения сигналов, поступающих с информацирнньк выходов блока 1 , с пороговыми напряжениями, которые соответствуют минимально допустимому уровню логической единицы 2,4В и максимально допустимому уровню логического нуля - 0,4 В. Количесвто N пороговых элементов определяется количеством контролируемьгх информационных разрядов блока 1 . Блок 3 содержит логические элементы, например элементы И 8. Количество Т, таких элементов определяется количеством контролируемых информационных разрядов. Блок 4 содержит элемент ИЛИ 9 и триггер 10.

Устройство работает следую цим образом.

При считывании информации из блока 1 полупостоянной памяти, в блоке 2 пороговых элементов происходит сравнение сигналов, поступающих с информационных выходов блока 1, с пороговыми напряжениями, которые соответствуют минимально допустимому уровню логической единицы - 2,4 В и максимально допустимому уровню логического нуля - 0,4 В. При приближении уровня информационного сигнала логической единицы к минимально допустимому (2,4 В) пороговьй элемент ПЭ 1 выдает сигнал логической единицы. В свою очередь уровень этого сигнала превьппает максимально допустимый уровень логического нуля (0,4 В), в результате чего пороговый элемент ПЭ О вьщает сигнал логической единицы. Аналогично, при приближении уровня информационного сигнала логического нуля к максимально допустимому (0,4 В), оба пороговых элемента ПЭ 1 и ПЭ О выдаю сигнал логической единицы. При нормальном состоянии информации в блоке 1 один из пороговых элементов ПЭ 1 и ПЭ О вьщает сигнал логической единицы, другой - логического

нуля, в блоке. И 3 определяется совпадение сигналов, поступающих с пороговых элементов ПЭ 1 и ПЭ О, а в блоке 4 формируется сш-нал регенерации. Контроль состояния информации осуществляется в каждом ци ле считывания, что достигается с помощью управляющего сигнала, поступающего с выхода блока 5 на вход блока 4.

Таким образом, в предлагаемом устройстве к информационным выходам блока 1 подключены только входы блока 2 пороговых элементов, что существенно уменьшает нагрузку на выходы блока 1 и, следовательно, улучшает эксплуатационные характеристики устройства. Уменьшение нагрузки на выходы блока 1 увеличивает время хранения информации без разрушения, за счет чего увеличивается срок службы блока полупостоянной памяти, так как число циклов регенерации информации в блоке полупостоянной памяти ограничено.

Упрощение устройства достигнуто за счет того, что в нем по сравнени с прототипом не используется Л/ элементов ИЛИ и N элементов ИЛИ-НЕ, а вместо 2 fi элементов И используется Ь элементов И (где nitn , amчисло разрядов накопителя).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с регенерацией информации | 1980 |

|

SU924757A1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Долговременное запоминающее устройствоСО ВСТРОЕННыМ КОНТРОлЕМ | 1979 |

|

SU830588A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1325569A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство | 1985 |

|

SU1288759A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕГЕНЕРАЦИЕЙ ИНФОРМАЦИИ, содержащее накопитель, блок формирования сигнала регенерации, блок управления, подключенный к накопителю и блоку формирования сигнала регенерации, блок пороговых элементов,, входы которого подключены к выходам накопителя, о тличающееся тем, что, с целью упрощения устройства, в него введен блок элементов И, входы которого подключены к выходам блока пороговых элементов, a выходы блока элементов И соединены с входами блока формирования сигнала регенерации. (Л со 00 о 00

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 3737879, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-06-15—Публикация

1983-03-31—Подача