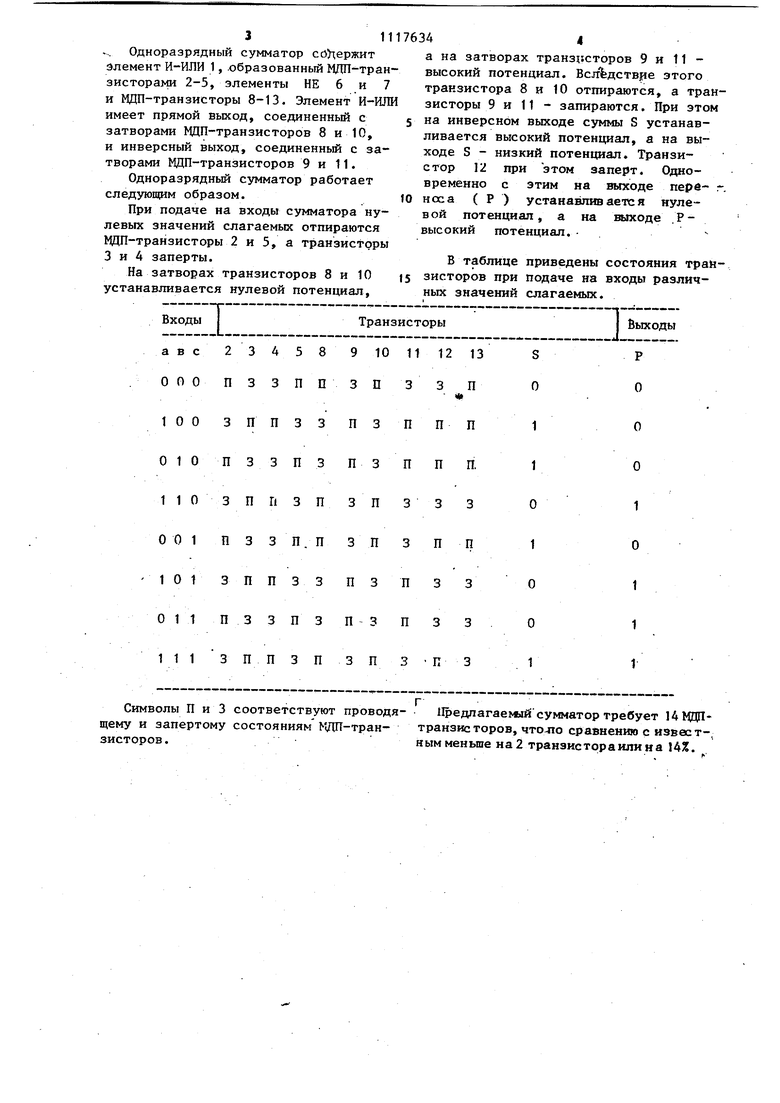

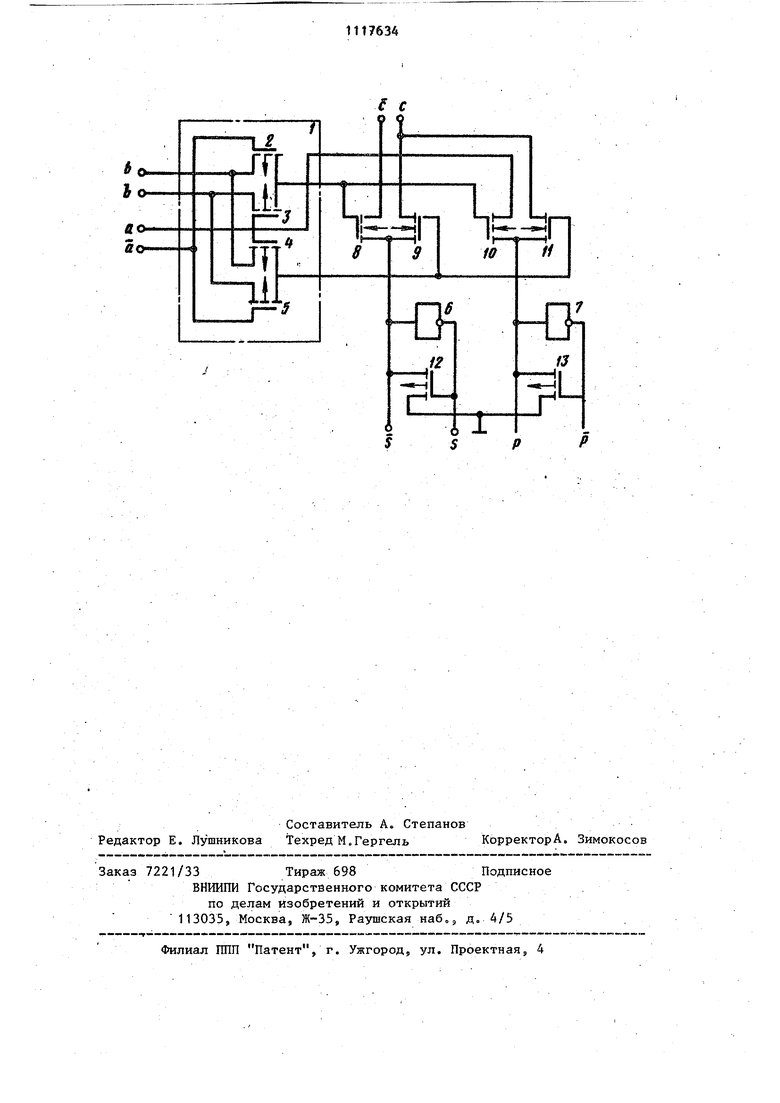

Изобретение относится к вычислительной технике и может быть использовано в больших интегральных: схемах обработки цифровой информации. Известен одноразрядный сумматор на дополняющих МДП-транзисторах, содержащий двадцать ВДП-транзисторов lj Недостатком сумматора является сложность конструкции. Известен одноразрядный сумматор на ВДП-транзисторах, содержащий элемент И-ИЛИ с прямым и инверсным выходами, узел формирования суммы, .содержащий три ВДП-транзистора и 3jgмент НЕ, и узел формирования переноса, содержащий три МДП-транзистора и эле мент НЕ, причем шины прямого и инвер ного значений первого слагаемого сум матора соединены с первыми входами с ответствующих элементов И элемента И-ИЛИ, а шины прямого и инверсного значений второго слагаемого сумматора соединены с вторыми входами соответствующих элементов И элемента И-ИЛИ, прямой выход элемента И-ИЛИ соединен с затворами первых МДП-тран зисторов узлов формирования суммы и переноса, а инверсный выход - с затворами вторьпс ВДП-транзисторов узло формирования суммы и переноса, исток первого МДП-транзистора узла формирования сум1-1Ы соединен с шиной инверсного значения третьего слагаемог сумматора, а сток соединен со стоком второго МДП-транзистора того же узла и с входом элемента НЕ того же узла, выход которого соединен с выходной шиной суммы сумматора, исток второго МДП-транзистора узла формирования суммы соединен с шиной прямого значения третьего слагаемого сумматора, исток второго 1ЩП-транзистора узла формирования суммы соединен с шиной прямого значения третьего слагаемого сумматора, сток первого МДП-транзистора узла формирования переноса соединен со стоком второго МДП-транзистора того же узла и с входом элемента НЕ того же узла. Кроме того, .каждый из узлов содержит четвертый МДП-транзистор 2J . Недостатком известного сумматора является сложность конструкции. Целью изобретения является упрощение одноразрядного сумматора. Поставленная цель достигается тем что одноразрядный сумматор, содержащими элемент И-ИЛИ с прямым и инверсным выходами, узел формирования суммы, содержащий три ВДП-транзистора и элемент НЕ, и узел формирования переноса, содержащий три ЩП-транзистрра и элемент НЕ, причем шины прямого и инверсного значений первого слагаемого сз мматора соединены с первыми входами соответствующих элементов И элемента И-ИЛИ, а шины прямого и инверсного значений второго слагаемого сумматора.соединены с вторыми входами соответствующих, элементов И элемента И-ИЛИ, прямой выход элемента И-ИЛИ соединен с затворами первых ОДП-транзисторов узлов формиро- вания суммы и переноса, а инверсный выход - с затворами вторых МДП-транзисторов узлов формирования суммы и переноса, исток первого МДП-транзистора узла формирования суммы соединен с шиной инверсного значения третьего слагаемого сумматора, а сток соединен со стоком второго МДП-транзистора того же узла и с входом элемента НЕ того же узла, выход которого соединен с вькодящей шиной суммы сумматора, исток второго МДП-транзистора узла формирования суммь соединен с шиной прямого значения третьего слагаемого, сумматора, сток первого МДП-транзистора узла формирования переноса соединен со стоком второго МДП-транзистора того же узла и с входом элемента НЕ того же узла, истоки первого и второго МДП-транзисторов узла формирования переноса соединены соответственно с шиной прямого значения первого слагаемого и с шиной прямого значения третьего слагаемого сумматора, сток первого МДП-транзистора узла формирования суммы соединен с выходной шиной инверсного значения суммы сумматора и со стоком третьего МДП-транзистора того же узла, затвор которого подключен к выходу элемента НЕ того же узла, а истОк соединен с шиной нулевого потенциала, : сток первого МДП-транзистора узла формирования переноса соединен с выходной шиной переноса сумматора со стоком третьего ЬЩП-транзистора того же узла, затвор которого соединен с выходом элемента НЕ того же узла и с выходной шиной инверсного значения переноса сумматора, а исток соединен с шиной нулевого потенциала. На чертеже представлена принципиальная схема одноразрядного сумматора. 3111763 -.. Одноразрядный сумматор сй)т;ержит элемент И-ИЛИ 1, .образованный МДП-транзистора ш 2-5, элементы НЕ 6 и 7 и МДП-транзисторы 8-13. Элемент И-ИЛИ имеет прямой выход, соединенный с j затворами МЦП-транзисторов 8 и 10, и инверсный выход, соединенный с затворами МДП-транзисторов 9 и 11. Одноразрядный сумматор работает следующим образом.fO При подаче на входы сумматора нулевых значений слагаемых отпираются ВДП-транзисторы 2 и 5, а транзисторы 3 и 4 заперты. На затворах транзисторов 8 и 10 15 устанавливается нулевой потенциал, 44 а на затворах транзисторов 9 и 11 высокий потенциал. ВслЙЬдствре этого транзистора 8 и 10 отпираются, а транзисторы 9 и 11 - запираются. При этом на инверсном выходе суммы S устанавливается высокий потенциал, а на выходе S - низкий потенциал. Транзистор 12 при этом заперт. Одновременно с этим на выходе пере- г носа ( Р ) устанавливается нулевой потенциал, а на галходе .Рвысокий потенциал. В таблице приведены состояния трайзисторов при подаче на входы различных значений слагаемых.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1287147A1 |

| Одноразрядный двоичный сумматор | 1987 |

|

SU1575170A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1291969A1 |

| Сумматор по модулю два | 1984 |

|

SU1191906A1 |

| Одноразрядный двоичный сумматор | 1980 |

|

SU943712A1 |

| Сумматор | 1983 |

|

SU1101863A1 |

| Формирователь переноса | 1984 |

|

SU1223223A1 |

| Блок формирования сквозного переноса в сумматоре | 1979 |

|

SU1042012A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР НА МОП ТРАНЗИСТОРАХ | 1996 |

|

RU2152641C1 |

ОДНОРАЗРЯДНЫЙ СУММАТОР, содержащий элемент И-ИЛИ с прямым и инверсным выходами, узел формировання суммы, содержащий три МДП-транзистора и элемент НЕ, и узел формирования переноса, содержащий три МДПтранзистора и .элемент НЕ, причем шины прямого и инверсного значений первого слагаемого сумматора соединены с первыми входами соответствующих элементов И элемента И-ИЛИ, а шины прямого и инверсного значений второго слагаемого сумматора соединены с вторыми входами соответствующих .элементов И элемента И-ИЛИ, прямой . выход элемента И-ИЛИ соединен с затворами первых ЩЩ-транзисторов узлов формирования суммы и переносу, а инверсный выход - с затворами вторых ВДП-транзисторов узлов формирования суммы и переноса, исток первого 1ЩП-транзистора узла формирования соединен с шиной инверсного значения третьего слагаемогр сумматора, а сток соединен со стоком второго МДП-транзистора того же узла и с входом элемента НЕ того же узла, выход которого соединен, с выходной шиной суммы сумматора, исток второго ; ЩП-транзистора узла формирования суммы соединен с пшной прямого значения третьего слагаемого сумматора, сток первого МДП-транзистора узла формирования переноса соединен со стоком второго МДП-транзистора того же узла и с входом элемента НЕ того же : узла, отличающийся тем что, с целью упрощения, истоки первого и- второго МЦП-транзистрров узла S формирования переноса соединены со- , ответственно с шиной прямого значе ния первого слагаемого и с шиной прямого значения третьего слагаемого сумматора, сток первого МДП-транзи§ стора узла формирования суммы сое- динен с выходной шиной инверсного значения суммы сумматора и со стоком третьего МДП-транзистора того же узла, затвор которого подключен к 1Ч| выходу элементаНЕ того же узла, а г 9д исток соединен с шиной нулевого потен&0 циала, сток первого МДП-транзистора узла формирования переноса соединен с выходной шиной переноса сумматора и со стоком третьего МДП-транзистора того же узла, затвор которого,соеди : йене 8ыз$рдом элемента НЕ того же уэла . и с выходной шиной инверсного, значе шя переноса сумматора, а исток соеТЩнен с шийой нулевого потенциала.

Символы П и 3 соответствуют проводящему и запертому состояниям МДП-транзисторов. Предлагаемыйсумматор требует 14ОДПтранзисторов,чтоло сравнению с извест-, кымменьше иа2 транзистораилина 14%.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Одноразрядный двоичный сумматор | 1980 |

|

SU943712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-07—Публикация

1983-01-06—Подача