Изобретение относится к вычисли-, тельной технике, в частности к устройствам обмена данными и может быть использовано в качестве буфера данных в каналах ввода-вывода ЭВМ.

Цель изобретения - повышение быстродействия устройства за счет обеспечения возможности выполнения обмена с оперативной памятью форматом, равным формату оперативной памяти, и возможности увеличения используемого обмена блока памяти для буферизации данных при цепочке данных.

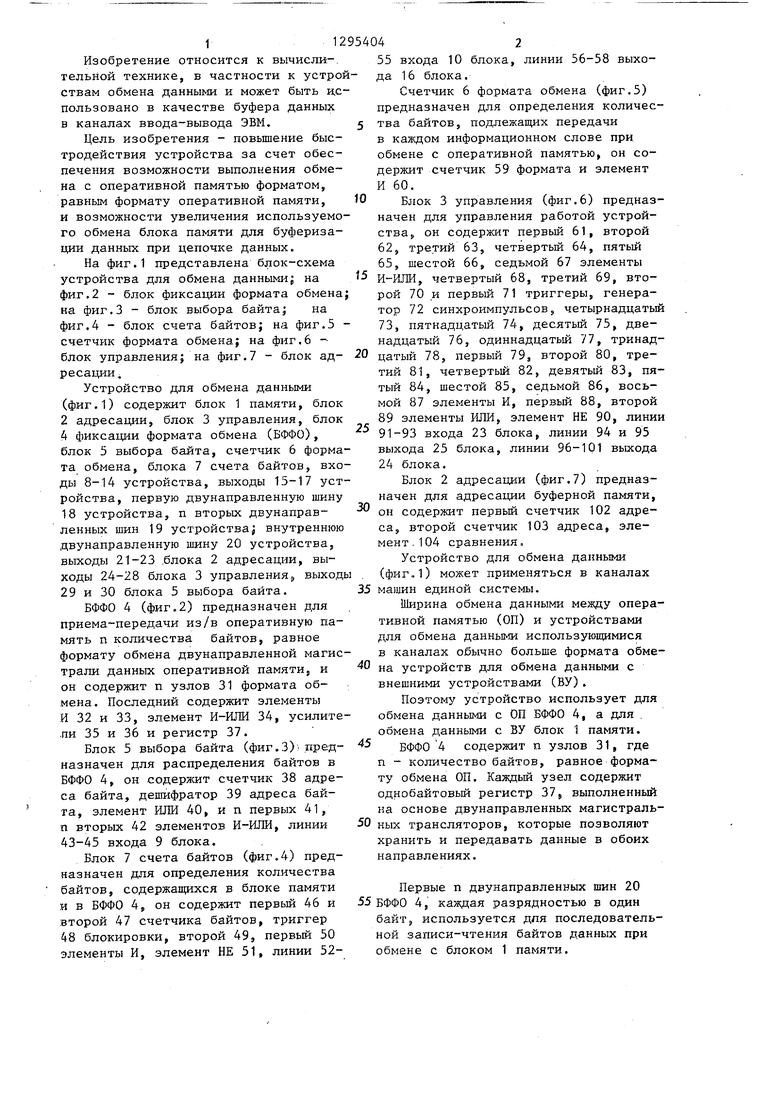

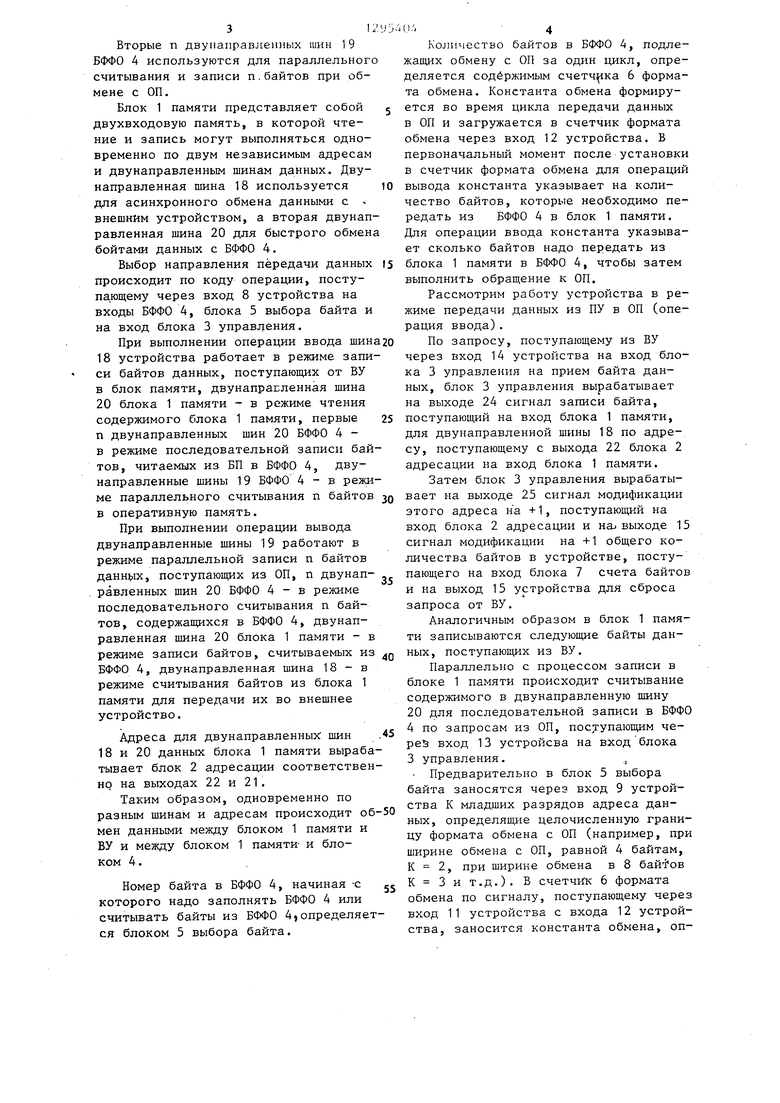

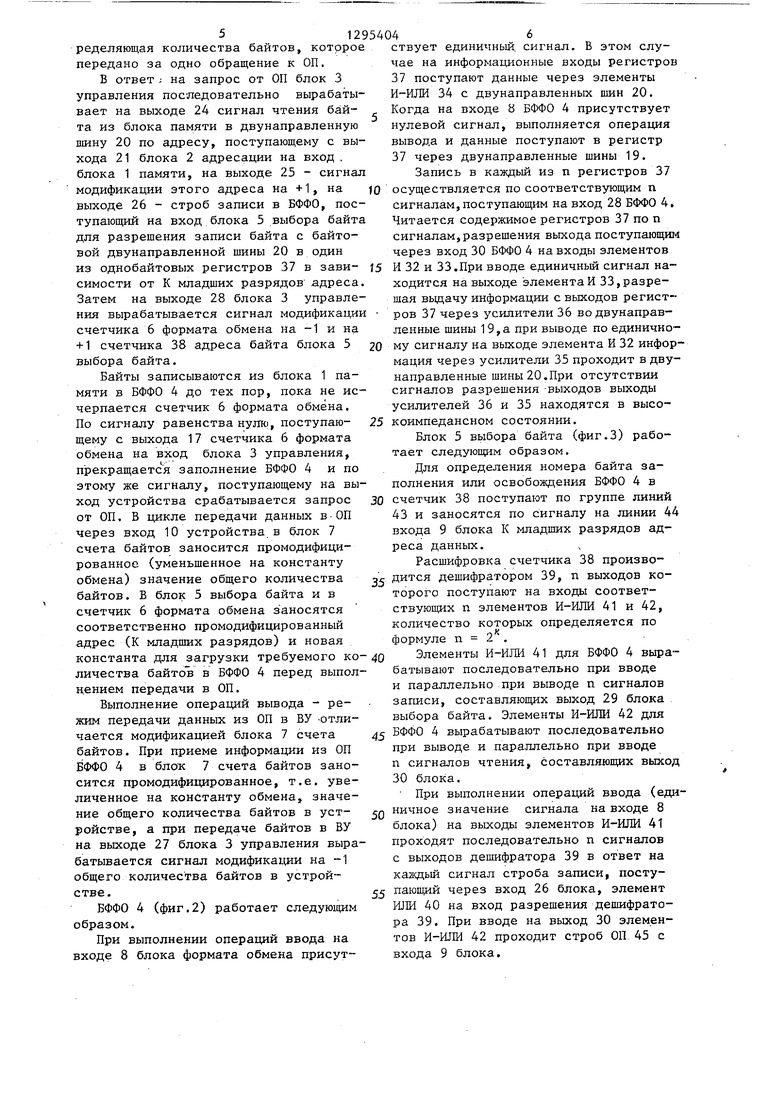

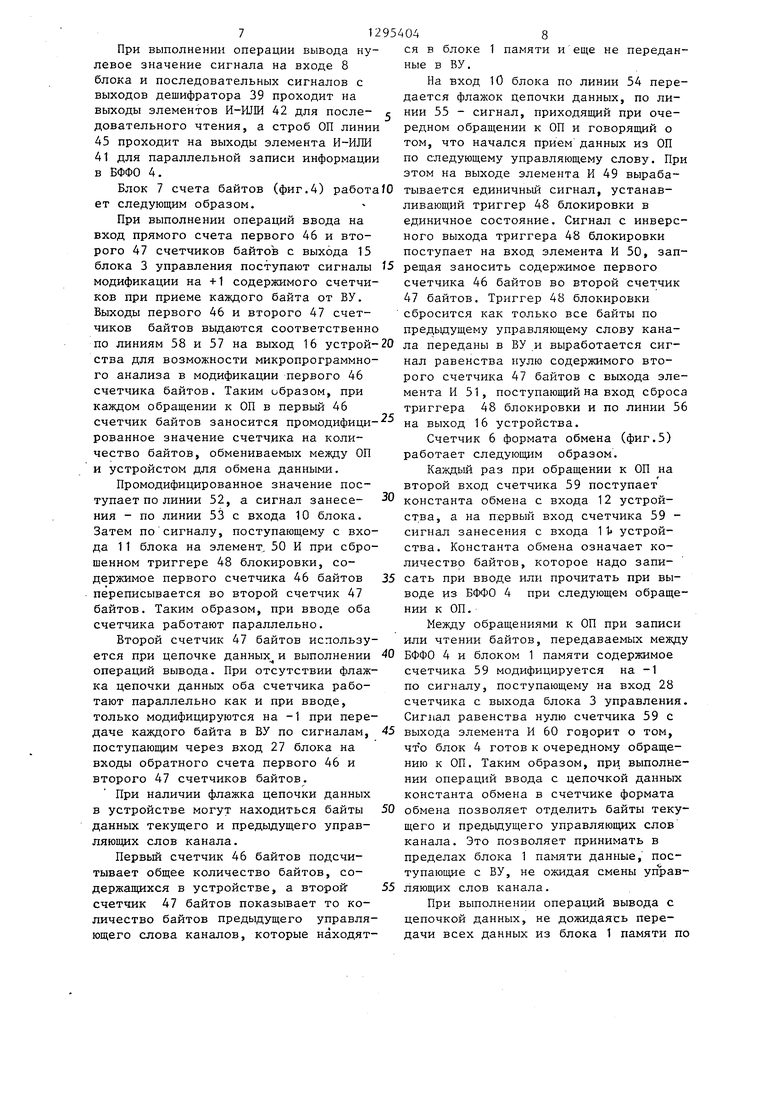

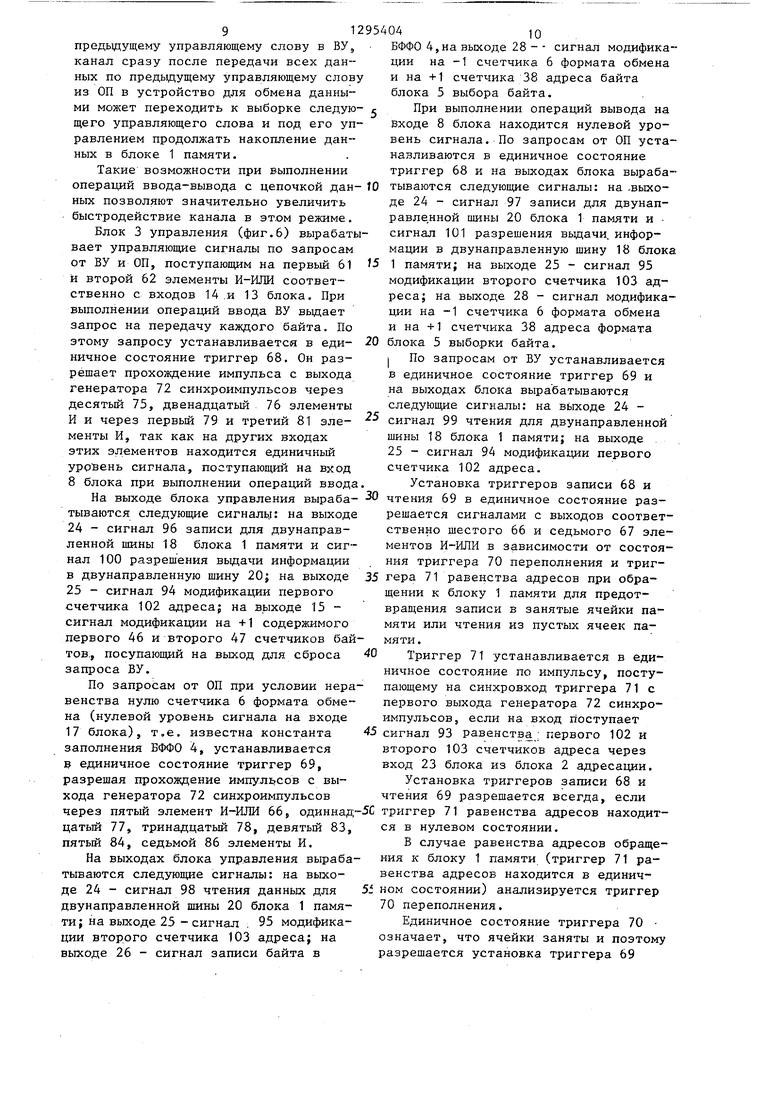

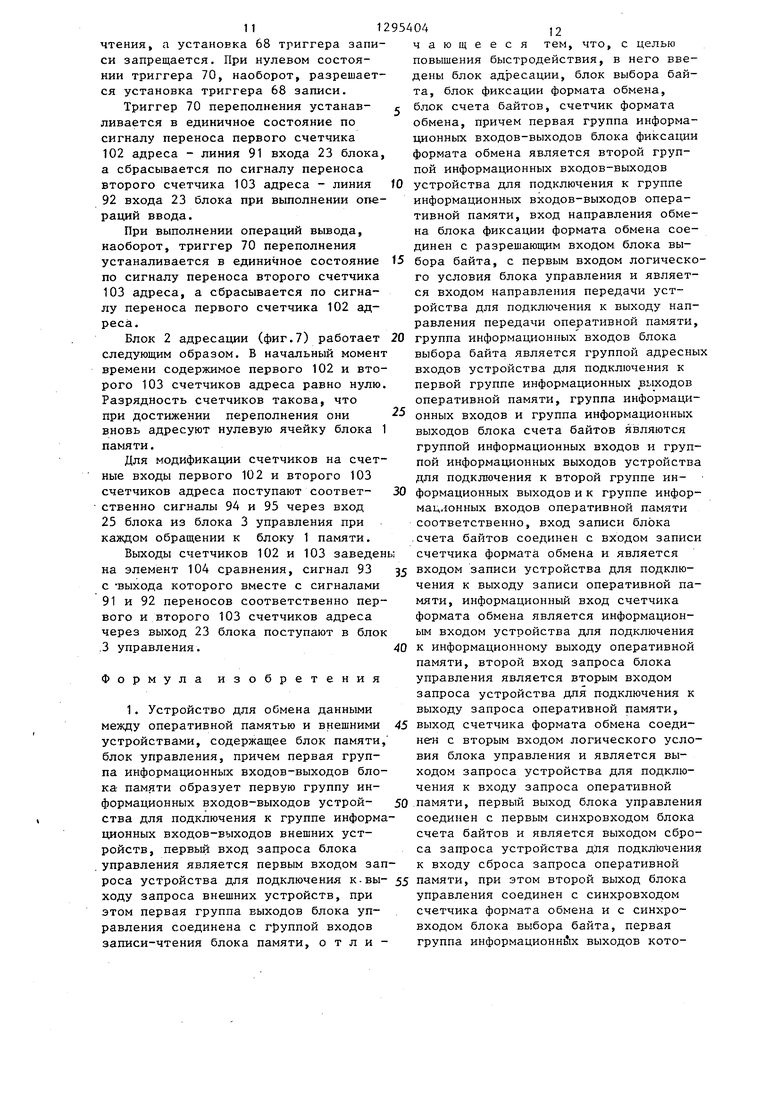

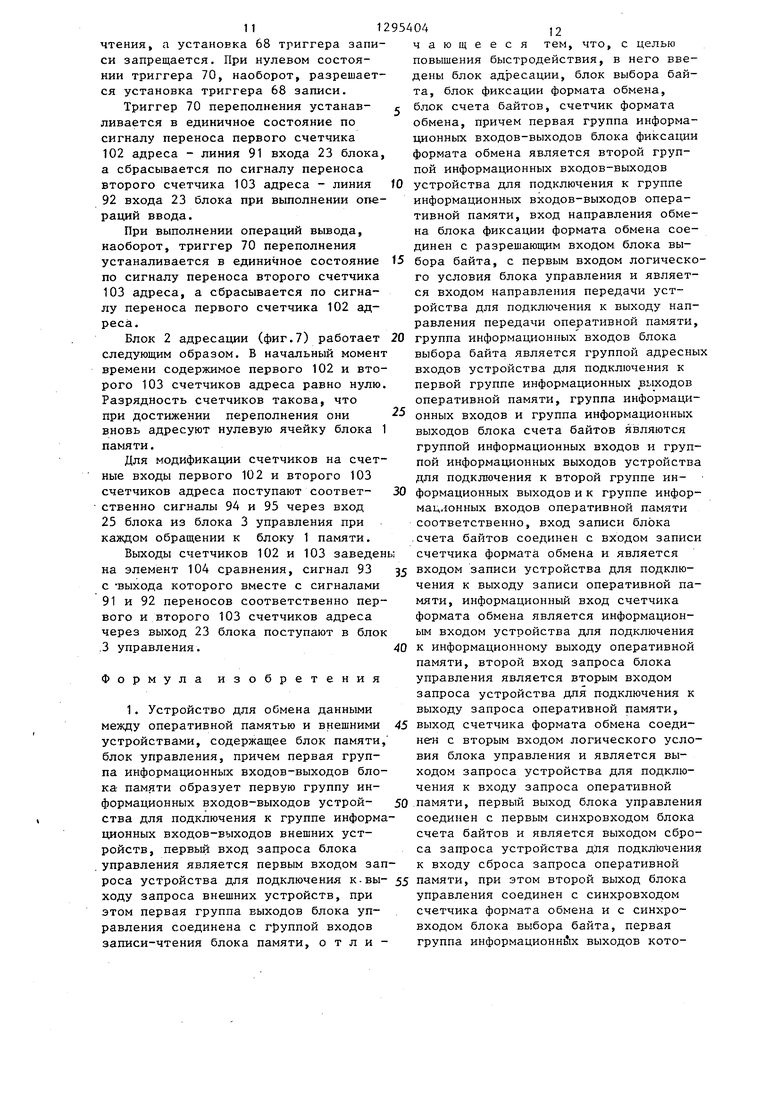

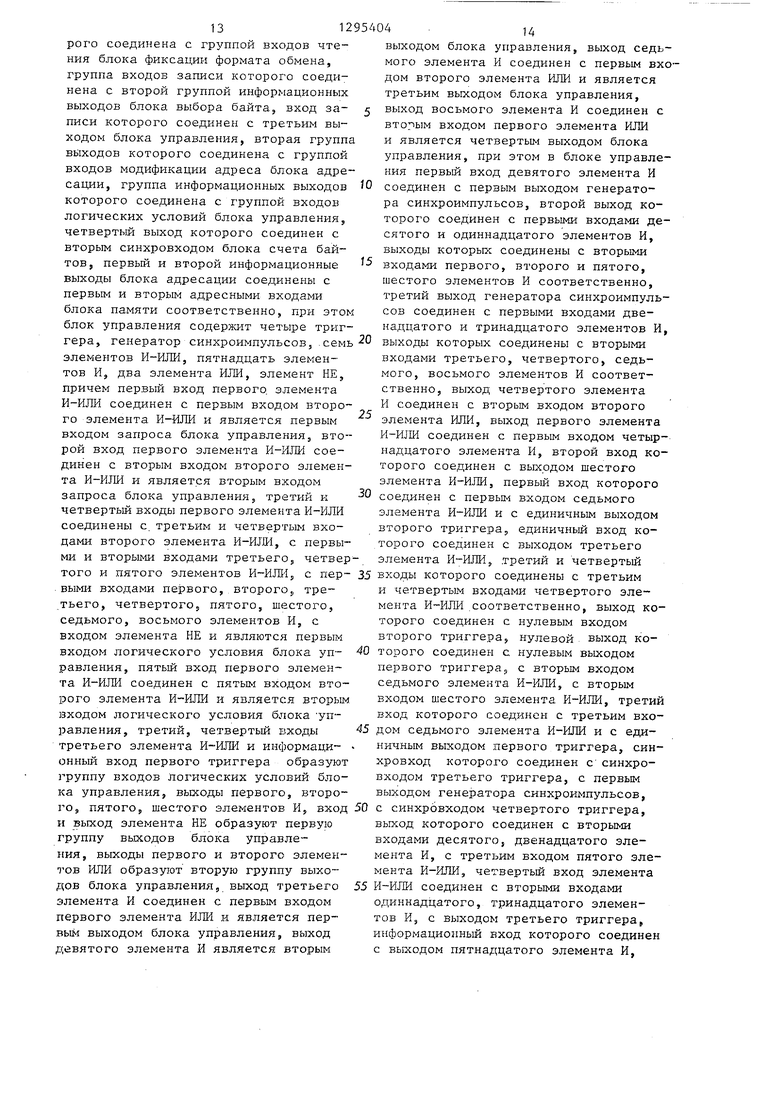

На фиг.1 представлена блок-схема устройства для обмена данными; на фиг,2 - блок фиксации формата обменаj на фиг.З - блок выбора байта; на фиг.4 - блок счета байтов; на фиг.З - счетчик формата обмена; на фиг.6 - блок управления; на фиг.7 - блок адресации.

Устройство для обмена данными (фиг.1) содержит блок 1 памяти, блок

2 адресации, блок 3 управления, блок 4 фиксаищи формата обмена (БФФО), блок 5 выбора байта, счетчик 6 формата обмена, блока 7 счета байтов, входы 8-14 устройства, выходы 15-17 устройства, первую двунаправленную шину

он содержит первьй счетчик 102 адреса, второй счетчик 103 адреса, эле18 устройства, п вторых двунаправленных шин 19 устройстваJ внутреннюю двунаправленную шину 20 устройства, мент.104 сравнения, выходы 21-23 .блока 2 адресации, вы- Устройство для обмена данными ходы 24-28 блока 3 управления выходы . (фиг,. 1) может применяться в каналах 29 и 30 блока 5 выбора байта. 35 машин единой системы.

БФФО 4 (фиг.2) предназначен для , Ширина обмена данными между опера- приема-передачи из/в оперативную память п количества байтов, равное формату обмена двунаправленной магистрали данньпс оперативной памяти, и он содержит п узлов 31 формата обмена. Последний содержит элементы И 32 и 33, злемент И-ИЛИ 34, усилители 35 и 36 и регистр 37.

Блок 5 выбора байта (фиг.3): пред- назначен для распределения байтов в БФФО 4, он содержит счетчик 38 адреса байта, дешифратор 39 адреса байта, элемент ИЛИ АО, и п первых 41, п вторых 42 элементов И-ШШ, линии 43-45 входа 9 блока.

Блок 7 счета байтов (фиг.4) предназначен для определения количества

байтов, содержащихся в блоке памяти Первые п двунаправленных шин 20 и в БФФО 4, он содержит первый 46 и 55 БФФО 4, каждая разрядностью в один второй 47 счетчика байтов, триггер байт, используется для последователь- 48 блокировки, второй 49, первый 50 ной записи-чтения байтов данных при элементы И, элемент НЕ 51, линии 52- обмене с блоком 1 памяти.

тивной памятью (ОП) и устройствами для обмена данными использующимися в каналах обычно больше формата обме на устройств для обмена данными с внешними устройствами (ВУ).

Поэтому устройство использует для обмена данными с ОП БФФО 4, а для . обмена данными с ВУ блок 1 памяти.

БФФО 4 содержит п узлов 31, где п - количество байтов, равное формату обмена ОП. Каждый узел содержит однобайтовый регистр 37, выполненный на основе двунаправленных магистраль50 ных трансляторов, которые позволяют хранить и передавать данные в обоих направлениях.

55 входа 10 блока, линии 56-58 выхода 16 блока.

Счетчик 6 формата обмена (фиг.5) предназначен для определения количества байтов, подлежапщх передачи в каждом информационном слове при обмене с оперативной памятью, он содержит счетчик 59 формата и злемент И 60.

Блок 3 управления (фиг.6) предназначен для управления работой устройства, он содержит первый 61, второй 62, третий 63, четвертый 64, пятый 65, шестой 66, седьмой 67 элементы

И-ИЛИ, четвертый 68, третий 69, второй 70 и первый 71 триггеры, генератор 72 синхроимпульсов 5 четырнадцатый 73, пятнадцатый 74, десятый 75, двенадцатый 76, одиннадцатый 77, тринадцатый 78, первый 79, второй 80, третий 81, четвертый 82, девятый 83, пятый 84, шестой 85, седьмой 86, восьмой 87 элементы И, первый 88, второй 89 элементы ИЛИ, элемент НЕ 90, линии 91-93 входа 23 блока, линии 94 и 95 выхода 25 блока, линии 96-101 выхода 24 блока.

Блок 2 адресации (фиг.7) предназначен для адресации буферной памяти,

он содержит первьй счетчик 102 адре

мент.104 сравнения, Устройство для обмена данными (фиг,. 1) может применяться в каналах машин единой системы.

са, второй счетчик 103 адреса, элемент.104 сравнения, Устройство для обмена данными (фиг,. 1) может применяться в каналах машин единой системы.

Ширина обмена данными между опера-

тивной памятью (ОП) и устройствами для обмена данными использующимися в каналах обычно больше формата обме на устройств для обмена данными с внешними устройствами (ВУ).

Поэтому устройство использует для обмена данными с ОП БФФО 4, а для . обмена данными с ВУ блок 1 памяти.

БФФО 4 содержит п узлов 31, где п - количество байтов, равное формату обмена ОП. Каждый узел содержит однобайтовый регистр 37, выполненный на основе двунаправленных магистраль50 ных трансляторов, которые позволяют хранить и передавать данные в обоих направлениях.

31

Вторые п двунаправленных шин 19 БФФО 4 используются для параллельного считывания и записи п.байтов при обмене с ОП.

Блок 1 памяти представляет собой двухвходовую память, в которой чтение и запись могут выполняться одновременно по двум независимым адресам и двунаправленным шинам данных. Двунаправленная шина 18 используется для асинхронного обмена данными с внешним устройством, а вторая двунаправленная шина 20 для быстрого обмена бойтами данных с БФФО 4,

Выбор направления передачи данных происходит по коду операции, поступающему через вход 8 устройства на входы БФФО 4, блока 5 выбора байта и на вход блока 3 управления.

При выполнении операции ввода шина 18 устройства работает в режиме записи байтов данных, поступающих от ВУ в блок памяти, двунапрасленная шина 20 блока 1 памяти - в режиме чтения содержимого блока 1 памяти, первые п двунаправленных шин 20 БФФО 4 - в режиме последовательной записи байтов, читаемых из БП в БФФО 4, двунаправленные шины 19 БФФО 4 - в режиме параллельного считывания п байтов в оперативную память.

При выполнении операции вывода двунаправленные шины 19 работают в режиме параллельной записи п байтов данн{)1х, поступаюш 1х из ОП, п двунап- равленных шин 20 БФФО 4 - в режиме последовательного считывания п байтов, содержащихся в БФФО 4, двунаправленная шина 20 блока 1 памяти - в режиме записи байтов, считываемых из БФФО 4, двунаправленная шина 18 - в режиме считывания байтов из блока 1 памяти для передачи их во внешнее устройство.

Адреса для двунаправленных шин 18 и 20 данных блока 1 памяти вырабатывает блок 2 адресации соответственно на выходах 22 и 21.

Таким образом, одновременно по разным шинам и адресам происходит обмен данными между блоком 1 памяти и ВУ и между блоком 1 памяти- и блоком 4.

Номер байта в БФФО 4, начиная -с jj которого надо заполнять БФФО 4 или считывать байты из БФФО 4)определяется блоком 5 выбора байта.

(,).( 4

Количество байтов в БФФО 4, подлежащих обмену с ОП за один цикл, определяется содержимым счетчика 6 формата обмена. Константа обмена формируется во время цикла передачи данных в ОП и загружается в счетчик формата обмена через вход 12 устройства. В первоначальный момент после установки в счетчик формата обмена для операций вывода константа указывает на количество байтов, которые необходимо передать из БФФО 4 в блок 1 памяти. Для операции ввода константа указывает сколько байтов надо передать из блока 1 памяти в БФФО 4, чтобы затем выполнить обращение к ОП.

Рассмотрим работу устройства в режиме передачи данных из ПУ в ОП (операция ввода).

По запросу, поступающему из ВУ через вход 14 устройства на вход блока 3 управления на прием байта данных, блок 3 управления вырабатывает на выходе 24 сигнал записи байта, поступающий на вход блока 1 памяти, для двунаправленной шины 18 по адресу, поступающему с выхода 22 блока 2 адресации на вход блока 1 памяти.

Затем блок 3 управления вырабатывает на выходе 25 сигнал модификации этого адреса н а +1, поступающий на вход блока 2 адресации и на выходе 15 сигнал модификации на +1 общего количества байтов в устройстве, поступающего на вход блока 7 счета байтов и на выход 15 устройства для сброса запроса от ВУ.

Аналогичным образом в блок 1 памяти записываются следующие байты данных, поступающих из ВУ.

Параллельно с процессом записи в блоке 1 памяти происходит считывание содержимого в двунаправленную шину 20 для последовательной записи в БФФО 4 по запросам из ОП, поступающим че- eS вход 13 устройсва на вход блока 3 управления.„

Предварительно в блок 5 выбора байта заносятся через вход 9 устройства К младших разрядов адреса данных, определящие целочисленную граниу формата обмена с ОП (например, при ширине обмена с ОП, равной 4 байтам, К 2, при ширине обмена в 8 байт ов .д.). В счетчик 6 формата обмена по сигналу, поступающему через вход 11 устройства с входа 12 устройства, заносится константа обмена, оп512954046

ределяющая количества байтов, которое ствует единичный, сигнал. В этом слу- передано за одно обращение к ОП. чае на информационные входы регистров

В ответ ; на запрос от ОП блок 3 управления последовательно вырабатывает на выходе 24 сигнал чтения байта из блока памяти в двунаправленную шину 20 по адресу, поступающему с выхода 21 блока 2 адресации на вход . блока 1 памяти, на выходе 25 - сигнал модификации этого адреса на +1, на ю выходе 26 - строб записи в БФФО, поступающий на вход блока 5 выбора байта для разрешения записи байта с байтовой двунаправленной шины 20 в один из однобайтовых регистров 37 в зави- 15 И 32 и ЗЗ.При вводе единичньй сигнал на- симости от К младших разрядов адреса. ходится на выходе элементам 33,разре- Затем на выходе 28 блока 3 управле- шая выдачу информации с выходов регист- ния вырабатывается сигнал модификации ров 37 через усилители 36 во двунаправ- счетчика 6 формата обмена на -1 и на ленные шины 19,а при выводе по единично- + 1 счетчика 38 адреса байта блока 5 20 му сигналу на выходе элемента И 32 инфор- выбора байта.мация через усилители 35 проходит в двуБайты записываются из блока 1 па- направленные шины 20.При отсутствии мяти в БФФО 4 до тех пор, пока не ис- сигналов разрешения -выходов выходы черпается счетчик 6 формата обмена. усилителей 36 и 35 находятся в высо25 коимпедансном состоянии.

Блок 5 выбора байта (фиг.З) рабо- тае.т следующим образом.

Для определения номера байта заполнения или освобождения БФФО 4 в

37 поступают данные через элементы И-ИЛИ 34 с двунаправленных шин 20. Когда на входе 8 БФФО 4 присутствует нулевой сигнал, выполняется операция вывода и данные поступают в регистр 37 через двунаправленные шины 19.

Запись в каждый из п регистров 37 осуществляется по соответствующим п сигналам,поступающим на вход 28 БФФО 4, Читается содержимое регистров 37 по п сигналам, разрешения выхода поступающш 1 через вход 30 БФФО 4 на входы элементов

По сигналу равенства нулю, поступающему с выхода 17 счетчика 6 формата обмена на вход блока 3 управления, прекращается заполнение БФФО 4 и по этому же сигналу, поступающему на выход устройства срабатывается запрос от ОП, В цикле передачи данных в-ОП через вход 10 устройства.в блок 7 счета байтов заносится промодифици- рованное (уменьшенное на константу обмена) значение общего количества байтов. В блок 5 выбора байта и в счетчик 6 формата обмена з аносятся соответственно промодифицированный адрес (К младших разрядов) и новая константа для загрузки требуемого ко личества байтоЪ в БФФО 4 перед выпол дением передачи в ОП.

Выполнение операций вывода - режим передачи данных из ОП в ВУ -отличается модификацией блока 7 счета байтов. При приеме информации из ОП БФФО 4 в блок 7 счета байтов заносится промодифицированное, т.е. увеличенное на константу обмена, значение общего количества байтов в устройстве, а при передаче байтов в ВУ на выходе 27 блока 3 управления вырабатывается сигнал модификагдаи на -1 общего количества байтов в устройстве.

БФФО 4 (фиг.2) работает следующим образом.

При выполнении операций ввода на входе 8 блока формата обмена присут

И 32 и ЗЗ.При вводе единичньй сигнал на- ходится на выходе элементам 33,разре- шая выдачу информации с выходов регист- ров 37 через усилители 36 во двунаправ- ленные шины 19,а при выводе по единично- му сигналу на выходе элемента И 32 инфор- мация через усилители 35 проходит в дву37 поступают данные через элементы И-ИЛИ 34 с двунаправленных шин 20. Когда на входе 8 БФФО 4 присутствует нулевой сигнал, выполняется операция вывода и данные поступают в регистр 37 через двунаправленные шины 19.

Запись в каждый из п регистров 37 осуществляется по соответствующим п сигналам,поступающим на вход 28 БФФО 4, Читается содержимое регистров 37 по п сигналам, разрешения выхода поступающш 1 через вход 30 БФФО 4 на входы элементов

40

30 счетчик 38 поступают по группе линий 43 и заносятся по сигналу на линии 44 входа 9 блока К младших разрядов адреса данных.

Расшифровка счетчика 38 произво25 дится дешифратором 39, п выходов которого поступают на входы соответствующих п элементов И-ИЛИ 41 и 42,

40

количество которых определяется по формуле п 2 .-

Элементы И-ИЛИ 41 для БФФО 4 вырабатывают последовательно при вводе и параллельно при выводе п сигналов загшси, составляющих выход 29 блока выбора байта Элементы И-ИЛИ 42 для

5 БФФО 4 вырабатывают последовательно при выводе и параллельно при вводе п сигналов чтения, составляющих выход 30 блока.

При выполнении операций ввода (единичное значение сигнала на входе 8 блока) на выходы элементов И-ИЛИ 41 проходят последовательно п сигналов с выходов деш:нфратора 39 в ответ на каждый сигнал строба записи, посту55 через вход 26 блока, элемент ШШ 40 на вход разрешения дешифратора 39. При вводе на выход 30 элементов И-ИЛИ 42 проходит строб ОП 45 с входа 9 блока.

50

При выполнении операции вывода нулевое значение сигнала на входе 8 блока и последовательных сигналов с выходов дешифратора 39 проходит на выходы элементов И-ШШ 42 для после- довательного чтения, а строб ОП линии 45 проходит на выходы элемента И-ИЛИ 41 для параллельной записи информации в БФФО 4.

Блок 7 счета байтов (фиг.4) работа ет следующим образом.

При выполнении операций ввода на вход прямого счета первого 46 и второго 47 счетчиков байтов с выхода 15 блока 3 управления поступают сигналы модификации на +1 содержимого счетчиков при приеме каждого байта от ВУ. Выходы первого 46 и второго 47 счетчиков байтов выдаются соответственно по линиям 58 и 57 на выход 16 устройства для возможности микропрограммного анализа в модификации первого 46 счетчика байтов. Таким образом, при каждом обращении к ОП в первый 46 счетчик байтов заносится промодифицированное значение счетчика на количество байтов, обмениваемых между ОП и устройстом для обмена данными.

Промодифицированное значение поступает по линии 52, а сигнал занесе- НИН - по линии 53 с входа 10 блока. Затем по сигналу, поступающему с входа 11 блока на элемент. 50 И при сброшенном триггере 48 блокировки, содержимое первого счетчика 46 байтов переписывается во второй счетчик 47 байтов. Таким образом, при вводе оба счетчика работают параллельно.

Второй счетчик 47 байтов используется при цепочке данных и выполнении операций вывода. При отсутствии флажка цепочки данных оба счетчика работают параллельно как и при вводе, только модифицируются на -1 при передаче каждого байта в ВУ по сигналам, поступающим через вход 27 блока на входы обратного счета первого 46 и второго 47 счетчиков байтов.

При наличии флажка цепочки данных в устройстве могут находиться байты данных текущего и предыдущего управляющих слов канала.

Первьш счетчик 46 байтов подсчитывает общее количество байтов, содержащихся в устройстве, а второй счетчик 47 байтов показывает то количество байтов предьщущего управляющего слова каналов, которые находятся в блоке 1 памяти и еще не переданные в ВУ.

На вход 10 блока по линии 54 передается флажок цепочки данных, по линии 55 - сигнал, приходящий при очередном обращении к ОП и говорящий о том, что начался прием данных из ОП по следующему управляющему слову. При этом на выходе элемента И 49 вырабатывается единичный сигнал, устанавливающий триггер 48 блокировки в единичное состояние. Сигнал с инверсного выхода триггера 48 блокировки поступает на вход элемента И 50, запрещая заносить содержимое первого счетчика 46 байтов во второй счетчик 47 байтов. Триггер 48 блокировки сбросится как только все байты по предьщущему управляющему слову канала переданы в ВУ и выработается сигнал равенства нулю содержимого второго счетчика 47 байтов с выхода элемента И 51, поступающий на вход сброса триггера 48 блокировки и по линии 56 на выход 16 устройства.

Счетчик 6 формата обмена (фиг.5) работает следующим образом.

Каждьш раз при обращении к ОП на второй вход счетчика 59 поступает константа обмена с входа 12 устройства, а на п.срвый вход счетчика 59 - сигнал занесения с входа 1 1 устройства. Константа обмена означает количество байтов, которое надо записать при вводе или прочитать при выводе из БФФО 4 при следующем обращении к ОП.

Между обращениями к ОП при записи или чтении байтов, передаваемых между БФФО 4 и блоком 1 памяти содержимое счетчика 59 модифицируется на -1 по сигналу, поступающему на вход 28 счетчика с выхода блока 3 управления Сигнал равенства нулю счетчика 59 с выхода элемента И 60 го дорит о том, чт о блок 4 готов к очередному обращению к ОП. Таким образом, при выполнении операций ввода с цепочкой данных константа обмена в счетчике формата обмена позволяет отделить байты текущего и предьщущего управляющих слов канала. Это позволяет принимать в пределах блока 1 памяти данные, поступающие с ВУ, не ожидая смены ляющих слов канала.

При выполнении операций вывода с цепочкой данных, не дожидаясь передачи всех данных из блока 1 памяти по

предыдущему управляющему слову в ВУ, канал сразу после передачи всех данных по предыдущему управляющему слову из ОП в устройство для обмена данными может переходить к выборке следую- щего управляющего слова и под его управлением продолжать накопление данных в блоке 1 памяти.

Такие возможности при выполнении

операций ввода-вывода с цепочкой дан-JO тываются следующие сигналы: на -выхо- ных позволяют значительно увеличить де 24 - сигнал 97 записи для двунап- быстродействие канала в эт,ом режиме. равле,нной шины 20 блока 1 памяти и

Блок 3 управления (фиг.6) вырабатывает управляющие сигналы по запросам от ВУ и ОП, поступающим на первый 61 и второй 62 элементы И-ИЛИ соответственно с входов 14 .и 13 блока. При

выполнении операций ввода ВУ вьщает запрос на передачу каждого байта. По

этому запросу устанавливается в еди- 20 блока 5 выборки байта.

ничное состояние триггер 68. Он разрешает прохождение импульса с выхода генератора 72 синхроимпульсов через десятый 75, двенадцатый 76 элементы И и через первый 79 и третий 81 элементы И, так как на других входах этих элементов находится единичный уровень сигнала, поступающий на вход 8 блока при выполнении операций ввода

I По запросам от ВУ устанавливается Б единичное состояние триггер 69 и на выходах блока вырабатываются следующие сигналы: на выходе 24 - сигнал 99 чтения для двунаправленной шины 18 блока 1 памяти; на выходе 25 сигнал 94 модификации первого счетчика 102 адреса.

Установка триггеров записи 68 и

На выходе блока управления выраба- - чтения 69 в единичное состояние раз- тываются следующие сигналы: на выходе решается сигналами с выходов соответ- 24 - сигнал 96 записи для двунаправленной шины 18 блока 1 памяти и сигнал 100 разрешения выдачи информации в двунаправленную шину 20; на выходе

ственно шестого 66 и седьмого 67 элементов И-ИЛИ в зависимости от состояния триггера 70 переполнения и триг- 35 гера 71 равенства адресов при обра25 - сигнал 94 модификации первого счетчика 102 адреса; на выходе 15 - сигнал модификации на 1 содержимого первого 46 и второго 47 счетчиков байтов;, посупающий на выход для сброса 40 запроса ВУ.

По запросам от ОП при условии неравенства нулю счетчика 6 формата обмена (нулевой уровень сигнала на входе 17 блока), Тов. известна константа заполнения БФФО 4, устанавливается 3 единичное состояние триггер 69, разрешая прохождение импульсов с выхода генератора 72 синхроимпульсов

щении к блоку 1 памяти для предотвращения записи в занятые ячейки памяти или чтения из пустых ячеек памяти.

Триггер 71 устанавливается в единичное состояние по импульсу, поступающему на синхровход триггера 71с первого выхода генератора 72 синхроимпульсов, если на вход поступает 45 сигнал 93 равенства : первого 102 и второго 103 счетчиков адреса через вход 23 блока из блока 2 адресации.

Установка триггеров записи 68 и

чтения 69 разрешается всегда, если через пятый элемент И-ИЛИ 66, одиннад-5С триггер 71 равенства адресов находит- цатый 77, тринадцатый 78, девятый 83, ся в нулевом состоянии, пятый 84, седьмой 86 элементы И.В случае равенства адресов обращеНа выходах блока управления выраба- ния к блоку 1 памяти (триггер 71 ратываются следующие сигналы: на выховенства адресов находится в единячде 24 - сигнал 98 чтения данных для 5i ном состоянии) анализируется триггер двунаправленной щины 20 блока 1 памя- 70 переполнения, ти; на выходе 25 - сигнал ; 95 модификации второго счетчика 103 адреса; на выходе 26 - сигнал записи байта в

Единичное состояние триггера 70 означает, что ячейки заняты и поэтому разрешается установка триггера 69

БФФО 4,на выходе 28 - сигнал модификации на -1 счетчика 6 формата обмена и на +1 счетчика 38 адреса байта блока 5 выбора байта.

При выполнении операций вывода на входе 8 блока находится нулевой уровень сигнала. По запросам от ОП устанавливаются в единичное состояние триггер 68 и на выходах блока вырабасигнал 101 разрешения выдачи, информации в двунаправленную шину 18 блока 1 памяти; на выходе 25 - сигнал 95 модификации второго счетчика 103 адреса; на выходе 28 - сигнал модификации на -1 счетчика 6 формата обмена и на +1 счетчика 38 адреса формата

I По запросам от ВУ устанавливается Б единичное состояние триггер 69 и на выходах блока вырабатываются следующие сигналы: на выходе 24 - сигнал 99 чтения для двунаправленной шины 18 блока 1 памяти; на выходе 25 сигнал 94 модификации первого счетчика 102 адреса.

Установка триггеров записи 68 и

- чтения 69 в единичное состояние раз- решается сигналами с выходов соответ-

ственно шестого 66 и седьмого 67 элементов И-ИЛИ в зависимости от состояния триггера 70 переполнения и триг- 35 гера 71 равенства адресов при обра40

щении к блоку 1 памяти для предотвращения записи в занятые ячейки памяти или чтения из пустых ячеек памяти.

Триггер 71 устанавливается в единичное состояние по импульсу, поступающему на синхровход триггера 71с первого выхода генератора 72 синхроимпульсов, если на вход поступает 45 сигнал 93 равенства : первого 102 и второго 103 счетчиков адреса через вход 23 блока из блока 2 адресации.

Установка триггеров записи 68 и

венства адресов находится в единячном состоянии) анализируется триггер 70 переполнения,

Единичное состояние триггера 70 означает, что ячейки заняты и поэтому разрешается установка триггера 69

11

чтения, а установка 68 триггера зап си запрещается. При нулевом состоянии триггера 70, наоборот, разрешаеся установка триггера 68 записи.

Триггер 70 переполнения устанав- ливается в единичное состояние по сигналу переноса первого счетчика 102 адреса - линия 91 входа 23 блок а сбрасывается по сигналу переноса второго счетчика 103 адреса - линия 92 входа 23 блока при выполнении опраций ввода.

При выполнении операций вывода, наоборот, триггер 70 переполнения

устаналивается в единичное состояние 15 бора байта, с первым входом логическо- по сигналу переноса второго счетчика 103 адреса, а сбрасывается по сигналу переноса первого счетчика 102 адреса.

Блок 2 адресации (фиг.7) работает следующим образом. В начальный момент времени содержимое первого 102 и второго 103 счетчиков адреса равно нулю.

го условия блока управления и является входом направления передачи устройства для подключения к выходу направления передачи оперативной памяти, 20 группа информационных входов блока

выбора байта является группой адресных входов устройства для подключения к первой группе информационных выходов оперативной памяти, группа информацивыбора байта является группой адресных входов устройства для подключения к первой группе информационных выходов оперативной памяти, группа информациРазрядность счетчиков такова, что

при достижении переполнения они онных входов и группа информационных вновь адресуют нулевую ячейку блока 1 выходов блока счета байтов являются памяти.группой информационных входов и групДля модификации счетчиков на счет- пой информационных выходов устройства ные входы первого 102 и второго 103 для подключения к второй группе ин- счетчиков адреса поступают соответ- 30 формационных выходов и к группе инфор- ственно сигналы 94 и 95 через вход мацлонных входов оперативной памяти 25 блока из блока 3 управления при соответственно, вход записи блока каждом обращении к блоку 1 памяти. .счета байтов соединен с входом записи

Выходы счетчиков 102 и 103 заведены счетчика формата обмена и является на элемент 104 сравнения, сигнал 93 35 входом записи устройства для подклю- с выхода которого вместе с сигналами 91 и 92 переносов соответственно первого и второго 103 счетчиков адреса через выход 23 блока поступают в блок .3 управления.

чения к выходу записи оперативной памяти, информационный вход счетчика

формата обмена является информацион- ым входом устройства для подключения

40 к информационному выходу оперативной памяти, второй вход запроса блока управления является вторым входом запроса устройства для подключения к выходу запроса оперативной памяти,

Формула изобретения

1. Устройство для обмена данными между оперативной памятью и внешними устройствами, содержащее блок памяти, блок управления, причем первая группа информационных входов-выходов блока- памяти образует первую группу информационных входов-выходов устройства для подключения к группе информационных входов-выходов внешних устройств, первый вход запроса блока

управления является первым входом зап- к входу сброса запроса оперативной роса устройства для подключения к-вы- 55 памяти, при этом второй выход блока ходу запроса внешних устройств, при управления соединен с синхровходом этом первая группа выходов блока уп- счетчика формата обмена и с синхро- равления соединена с группой входов входом блока выбора байта, первая записи-чтения блока памяти, о т л и - группа информационней выходов кото04

чающееся

12 тем, что, с целью

повышения быстродействия, в него введены блок адресации, блок выбора байта, блок фиксации формата обмена, блок счета байтов, счетчик формата обмена, причем первая группа информационных входоввыходов блока фиксации формата обмена является второй группой информационных входов-выходов устройства для подключения к группе информационных входов-выходов оперативной памяти, вход направления обмена блока фиксации формата обмена соединен с разрешающим входом блока выбора байта, с первым входом логическо-

го условия блока управления и является входом направления передачи устройства для подключения к выходу направления передачи оперативной памяти, группа информационных входов блока

выбора байта является группой адресных входов устройства для подключения к первой группе информационных выходов оперативной памяти, группа информационных входов и группа информационных выходов блока счета байтов являются группой информационных входов и групсчетчика формата обмена и является входом записи устройства для подклю-

чения к выходу записи оперативной памяти, информационный вход счетчика

счетчика формата обмена и является 35 входом записи устройства для подклю-

формата обмена является информацион- ым входом устройства для подключения

40 к информационному выходу оперативной памяти, второй вход запроса блока управления является вторым входом запроса устройства для подключения к выходу запроса оперативной памяти,

45 выход счетчика формата обмена соединен с вторым входом логического условия блока управления и является выходом запроса устройства для подключения к входу запроса оперативной

50 памяти, первый выход блока управления соединен с первым синхровходом блока счета байтов и является выходом сброса запроса устройства для подключения

13129540414

рого соединена с группой входов чте- выходом блока управления, выход седь- ния блока фиксации формата обмена, мого элемента И соединен с первым вхо- группа входов записи которого соеди- дом второго элемента ИЛИ и является йена с второй группой информационных третьим выходом блока управления, выходов блока выбора байта, вход за- 5 выход восьмого элемента И соединен с писи которого соединен с третьим вы- вторым входом первого элемента ИЛИ ходом блока управления, вторая группа и является четвертым выходом блока выходов которого соединена с группой управления, при этом в блоке управле- входов модификации адреса блока адре- ния первый вход девятого элемента И сации, группа информационных выходов Ю соединен с первым выходом генерато- которого соединена с группой входов ра синхроимпульсов, второй выход ко- логических условий блока управления, торого соединен с первыми входами де- четвертый выход которого соединен с сятого и одиннадцатого элементов И, вторым синхровходом блока счета бай- выходы которых соединены с вторыми тов, первый и второй информационные входами первого, второго и пятого, выходы блока адресации соединены с шестого элементов И соответственно, первым и вторым адресными входами третий выход генератора синхроимпуль- блока памяти соответственно, при этом сов соединен с первыми входами две- блок управления содержит четыре триг- надцатого и тринадцатого элементов И, гера, генератор синхроимпульсов, -семь выходы которых соединены с вторыми элементов И-ИЛИ, пятнадцать элемен- входами третьего, четвертого, седь- тов И, два элемента ИЖ, элемент НЕ, мого, восьмого элементов И соответ- причем первый вход первого, элемента ственно, выход четвертого элемента И-ИЛИ соединен с первым входом второ- И соединен с вторым входом второго го элемента И-ИЛИ и является первым элемента ИЛИ, выход первого элемента входом запроса блока управления, вто- И-ИЛИ соединен с первым входом четыр- рой вход первого элемента И-ИЛИ сое- надцатого элемента И, второй вход ко- динен с вторым входом второго элемен- торого соединен с выходом шестого та И-ИШ и является вторым входом элемента И-ИЛИ, первый вход которого запроса блока управления, третий и соединен с первым входом седьмого четвертый входы первого элемента И-ИЛИ элемента И-ИЛИ и с единичным выходом соединены с. третьим и четвертым вхо- второго триггера, единичный вход кодами второго элемента И-ИЛИ, с первы- торого соединен с выходом третьего ми и вторыми входами третьего, четвер- элемента И-ИЖ, третий и четвертый того и пятого элементов И-ИШ, с пер- 35 входы которого соединены с третьим .выми входами первого, второго тре- и четвертым входами четвертого эле- тьего, четвертого, пятого, шестого, мента И-ИЛИ соответственно, выход ко- седьмого, восьмого элементов И, с торого соединен с нулевым входом входом элемента НЕ и являются первым второго триггера, нулевой выход ко- входом логического условия блока уп- 0 торого соединен с нулевым выходом равления, пятый вход первого элемен- первого триггера, с вторым входом та И-ЕЛИ соединен с пятым входом вто- седьмого элемента И-ИЛИ, с вторым рого элемента И-ИЛИ и является вторым входом шестого элемента И-ИЛИ, третий входом логического условия блока уп- вход которого соединен с третьим вхо- равления, третий, четвертьш входы дом седьмого элемента И-ИЛИ и с еди- третьего элемента И-ШШ и информаци- - ничным выходом первого триггера, синенный вход первого триггера образуют хровход которого соединен с синхрогруппу входов логических условий бло- входом третьего триггера, с первым ка управления, выходы первого, второ- выходом генератора синхроимпульсов, roj пятого, шестого элементов И, вход 50 с синхровходом четвертого триггера, и выход элемента НЕ образуют первую вькод которого соединен с вторыми группу выходов блока управле- входами десятого, двенадцатого эле- пия, выходы первого и второго элемен- мента И, с третьим входом пятого эле- гов ИЛИ образуют вторую группу выхо- мента И-ИЛИ, четвертый вход элемента ДОН блока управления, выход третьего 55 И-ИЛИ соединен с вторыми входами элемента И соединен с первым входом одиннадцатого, тринадцатого элемен- первого элемента ИЛИ и является пер- тов И, с выходом третьего триггера, вым выходом блока управления, выход информационный вход которого соединен девятого элемента И является вторым с выходом пятнадцатого элемента И,

первый и второй входы которого соединены с выходами второго и седьмого элемента И-ИЛИ соответственно, выход пятого элемента И-ИЛИ соединен с вторым входом девятого элемента И, вы- 5 ход четырнадцатого элемента И соединен с информационным входом четвертого триггера, вторая группа информационных

дом записи блока выбора байта соотве ственно, второй вход элемента ИЛИ соединен с вторыми и третьими входами элементов И-ИЛИ первой и второй групп и является разрешающим входом блока выбора байта, выходы элементов ИЛИ первой и второй групп образуют первую и вторую группы информационных выходов блока выбора байта соответственвходов-выходов блока фиксации формата соединена с второй группой информаци- Ш но, при этом в блоке выбора байта онных входов-выходов блока памяти,. информационный выход счетчика адреса 2. Устройство поп.1,отличабайта и выход элемента ИЛИ соединены с информационным входом и управляющи входом дешифратора адреса байта, группа разрядных выходов которого соединена с четвертыми входами соответствующих элементов И-ИЛИ первой и второй групп.

ю щ е е с я тем, что блок фиксации

формата обмена содержит группу узлов формата обмена, при этом каждый узел -5 формата обмена содержит два усилителя, регистр, элемент И-ШШ, два элемента И, причем информационный выход первого усилителя и первый вход элемента

И-ИЛИ каждого узла формата обмена об- 0 ю щ е е с я тем, что блок счета бай- разуют первую группу информационных тов содержит два счетчика байтов,

байта и выход элемента ИЛИ соединены с информационным входом и управляющим входом дешифратора адреса байта, группа разрядных выходов которого соединена с четвертыми входами соответствующих элементов И-ИЛИ первой и второй групп.

4. Устройство ПОП.1, отличавходов-выходов блока фиксации формата обмена, информационный выход второго усилителя и второй вход элемента И-ИЛИ каждого узла формата обмена образуют вторую группу информационных входов-выходов блока фиксации формата обмена, первые входы первого и второго элементов И каждого узла формата обмена образуют группу входов чтения блока фиксации формата обмена, синхровходы регистров каждого узла фор- ;мата обмена образуют группу входов записи блока фиксации формата обмена,вторые входы первого, второго элементов И, .третьи, четвертые входы элемента И-ИЛИ каждого узла формата обмена являются входом направления обмена блока фиксации формата обмена, при

25

30

триггер блокировки, два элемента И, элемент НЕ, причем первые и в.торые синхровходы первого и второго счетчиков байтов являются первым и вторым синхровходами блока счета байтов, первый вход первого элемента И является входом записи блока счета байтов, информационный вход и вход записи первого счетчика байтов, первый и. второй входы второго элемента И образуют группу информационных входов блока счета байтов, выходы первого, второго счетчиков байтов и выход элё- 35 мента ИЕ образуют группу информационных выходов блока счета байтов, причем в блоке счета байтов.выход первого счетчика байтов соединен с информационньтм входом второго счетэтом в каждом узле формата обмена вы- чика байтов, выход которого соединен

ходы первого и второго элементов Ис входом элемента НЕ, выход которого

соединены с управляющими входами пер-соединен с нулевым входом триггера

вого и второго усилителей соответ-блокировки, нулевой выход которого

;ственно, информационные входы которыхсоединен с вторым входом первого

соединены с выходами регистра, инфор- 45элемента И, выход которого соединен

мационньй вход которого соединен сс входом записи второго счетчика бай- выходами элемента И-ИЛИ.

3. Устройство по П.1, о т л и ч атов, выход второго элемента И соединен с единичным входом триггера блокировки .

ю щ е е с я тем, что блок выбора байта содержит счетчик адреса байта, 50 дешифратор адреса байта, элемент ИЛИ, две группы элементов И-ИЛИ, причем, информационный вход, вход записи счетчика адреса байта, первые входы

тов, выход второго элемента И соединен с единичным входом триггера блокировки .

5. Устройство по П.1, отличающееся тем, что блок адре сации содержит два счетчика и элемент сравнения, причем синхровходы элементов И-ИЛИ первой и второй групп 55 первого и второго счетчиков адреса образуют группу информационных входов образуют группу входов модификации блока выбора байта, синхровход счетчика адреса байта и первый вход элеадреса блока адресации, информацион ные выходы первого и второго счетчиков адреса являются первым и втомента ШШ являются синхровходом и входом записи блока выбора байта соответственно, второй вход элемента ИЛИ соединен с вторыми и третьими входами элементов И-ИЛИ первой и второй групп и является разрешающим входом блока выбора байта, выходы элементов ИЛИ первой и второй групп образуют первую и вторую группы информационных выходов блока выбора байта соответственно, при этом в блоке выбора байта информационный выход счетчика адреса

но, при этом в блоке выбора байта информационный выход счетчика адреса

ю щ е е с я тем, что блок счета бай- тов содержит два счетчика байтов,

байта и выход элемента ИЛИ соединены с информационным входом и управляющим входом дешифратора адреса байта, группа разрядных выходов которого соединена с четвертыми входами соответствующих элементов И-ИЛИ первой и второй групп.

4. Устройство ПОП.1, отлича5

0

триггер блокировки, два элемента И, элемент НЕ, причем первые и в.торые синхровходы первого и второго счетчиков байтов являются первым и вторым синхровходами блока счета байтов, первый вход первого элемента И является входом записи блока счета байтов, информационный вход и вход записи первого счетчика байтов, первый и. второй входы второго элемента И образуют группу информационных входов блока счета байтов, выходы первого, второго счетчиков байтов и выход элё- 5 мента ИЕ образуют группу информационных выходов блока счета байтов, причем в блоке счета байтов.выход первого счетчика байтов соединен с информационньтм входом второго счетс входом записи второго счетчика бай-

тов, выход второго элемента И соединен с единичным входом триггера блокировки .

5. Устройство по П.1, отличающееся тем, что блок адре сации содержит два счетчика и элемент сравнения, причем синхровходы первого и второго счетчиков адреса образуют группу входов модификации

адреса блока адресации, информационные выходы первого и второго счетчиков адреса являются первым и вторым информационными выходами блока адресации соответственно, выходы переноса первого и второго счетчиков адреса и выход элемента сравнения образуют группу информационных выходов

9 26

блока адресации,, при этом первый и второй входы элемента сравнения соединены с информационными выходами первого и второго счетчиков адреса соответственно.

29

W

Фиг.

Щ.

УЗ. 77If

60

{}

77

25

27 28

Составитель С.Пестмал Редактор Н.Рогулич Техред и.Попович Корректор Н.Король

619/56

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/3

Производственно-полиграфическое предприятие, г,5 жгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для обмена данными между оперативной памятью и внешним устройством | 1984 |

|

SU1180908A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1829038A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для сопряжения ЭВМ с селекторным каналом | 1986 |

|

SU1401472A1 |

| Устройство для обмена информацией | 1985 |

|

SU1339572A1 |

Изобретение относится к вычислительной технике, в частности к устройствам обмена данными. Оно может в 3 19 19 быть использовано в качестве буфера данных в каналах ввода-вывода ЭВМ. Целью изобретения является повышение быстродействия устройства за счет обеспечения возможности выполнения обмена с оперативной памятью форматом, равным формату оперативной памяти, и возможности увеличения используемого объема блока памяти для буферизации данных при цепочке данных. Устройство содержит блок 1 памяти, блок 3 управления, блок 2 адресации, блок 5 выбора байта, блок 4 фиксации формата обмена, блок 7 счета байтов, счетчик 6 формата обмена. 4 з.п. ф-лы, 7 ил. f9 15 161011 П 1713 а В сл ю (Х О1 4 О 4 « риг. 1 1

| Устройтво для обмена данными | 1977 |

|

SU691830A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена данными между оперативной памятью и внешним устройством | 1984 |

|

SU1180908A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1987-03-07—Публикация

1985-09-25—Подача