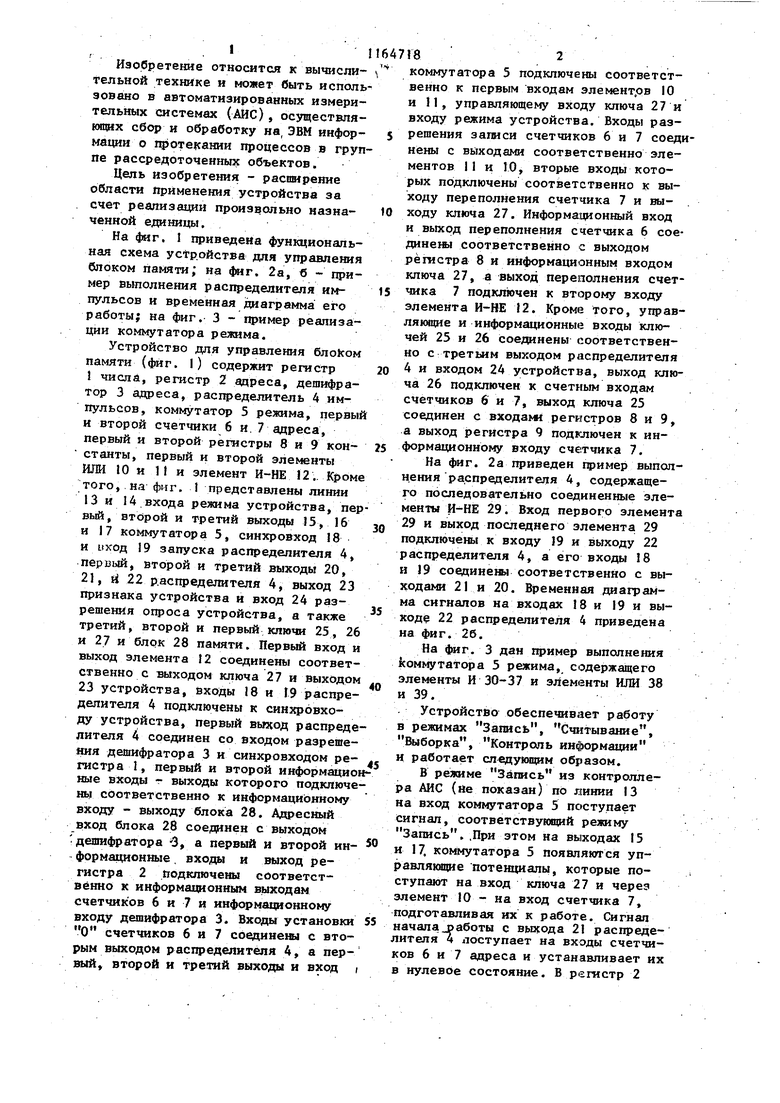

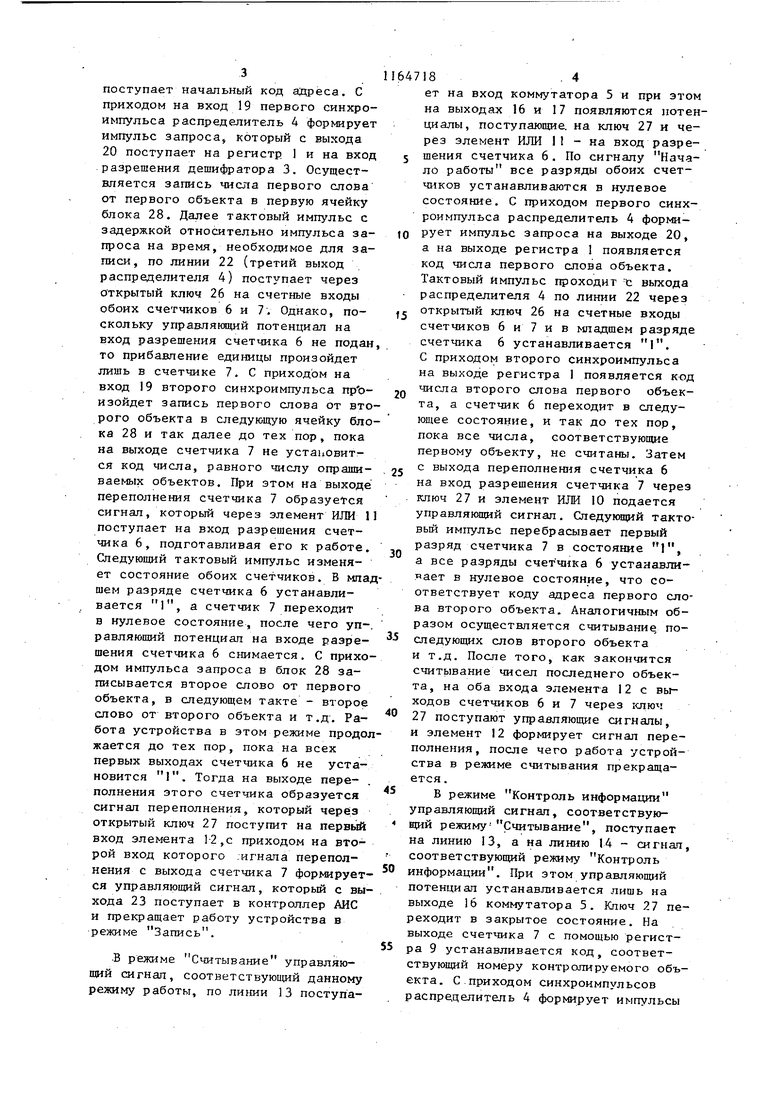

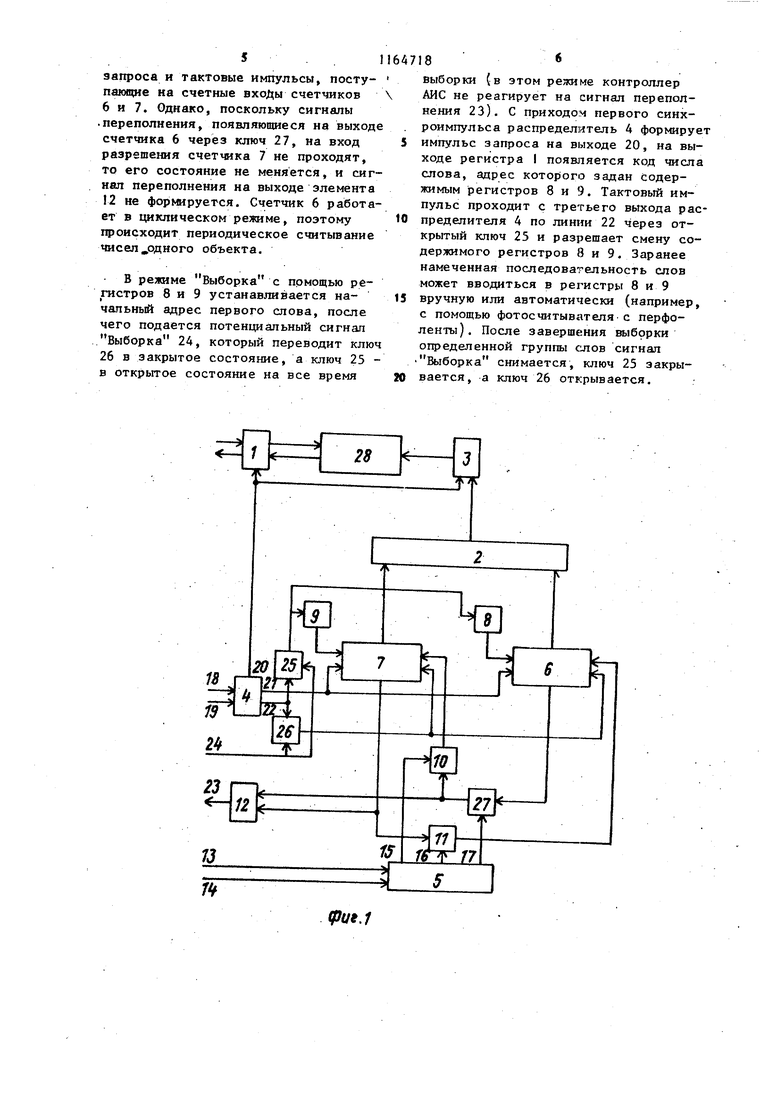

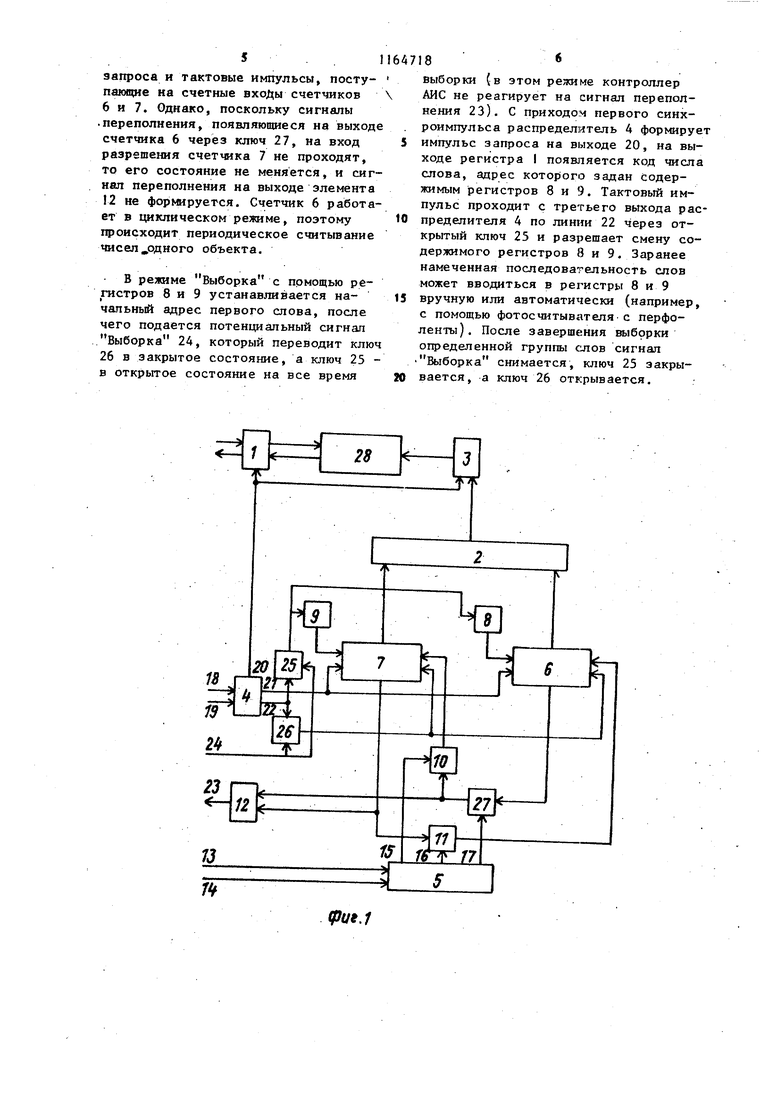

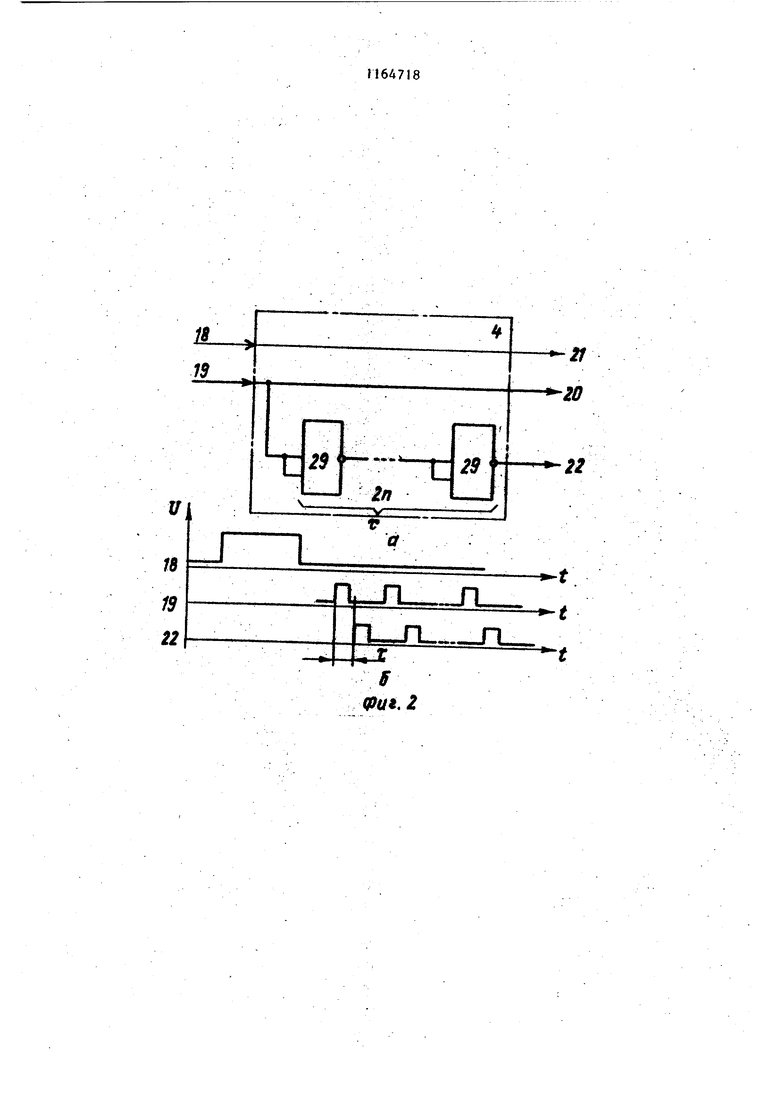

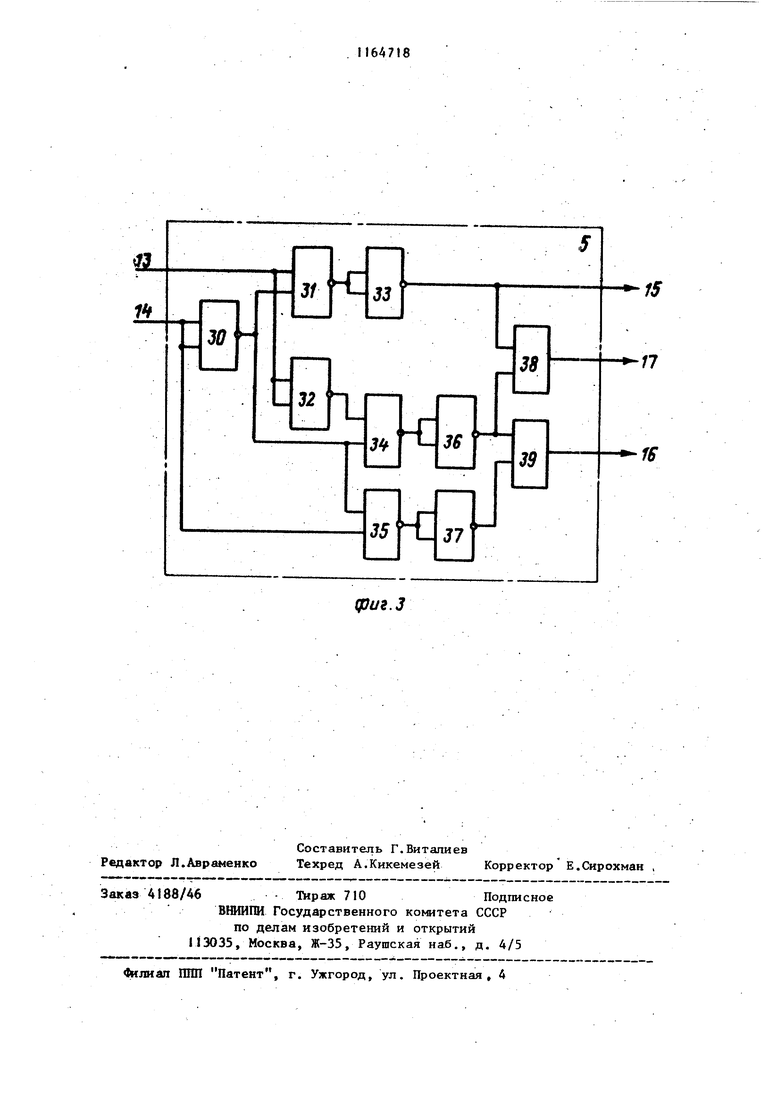

Изобретение относится к вычислительной технике и может быть исполь зовано в автоматизированных измерительных системах (АИС), осуществляющих сбор и обработку на, ЭВМ информации о щ оте|сании процессов в груп пе рассредоточенных объектов. Цель изобретения - pacnsfpemie области Применения устройства за счет реализации произвольно назначенной единицы. На фиг. I приведена функциональная схема yctp.oйcтвa для управления блоком памяти; на г. 2а, б - пример выполнения распределителя импульсов и временная диаграмма его работы; на фиг. 3 - пример реализации коммутатора режима. Устройство для управления блоком памяти (фиг. I) содержит релястр 1 числа, регистр 2 адреса, дешифратор 3 адреса, распределитель 4 импульсов, коммутатор 5 режима, первы и второй счетчики 6 и. 7 адреса, первый и второй регистры 8 и 9 константы, первый и второй элементы ИЛИ 10 и Пи элемент И-НЕ 12. Кром того, на фиг. I представлены линии 13 и 14 входа режима устройства, пер вый, второй и третий выходы 15, 16 и 17 коммутатора 5, синхровход 18 и икод 19 запуска распределителя 4, первый, второй и третий выходы 20, 21, ri 22 распределителя 4, выход 23 признака устройства и вход 24 разрешения опроса устройства, а также третий, второй и первый ключи 25, 26 и 27 и блок 28 памяти. Первый вход и выход элемента 12 соединены соответ ственно с выходом ключа 27 и выходо 23 устройства, входы 18 и Г9 распре делителя 4 подключены к синхровходу устройства, первый вьисод распред лителя 4 соединен со входом разрешеяия дешифратора 3 и синхровходом регистра 1, первый и второй информацио ные входы г выходы которого подключе нь1 соответственно к информациЬнному входу - выходу блока 28. Адресный вход блока 28 соединен с выходом дешифратора в, а первый и второй информационные . входы и выход регистра 2 подключены соответственно к информационным выходам счетчиков 6 и 7 и информационному входу дапифратора 3. Входы установки О счетчиков 6 и 7 соединены с вторым выходом распределителя 4, а первый, второй и третий выходы и вход коммутатора 5 подключены соответственно к первым входам элементов 10 и 11, управляющему входу ключа 27 и входу режима устройства. Входы разрешения записи счетчиков 6 и 7 соединены с выходами соответственно элементов II и 10, вторые входы которых подключены соответственно к выходу переполнения счетчика 7 и вы- . ходу ключа 27. Информа:1Д1онный вход и выход переполнения счетчика 6 соединенл соответственно с выходом регастра 8 и информационным входом ключа 27, а выход переполнения счетчика 7 подключен к второму входу элемента И-НЕ 12. того, управляющие и информационные входы ключей 25 и 26 соединены соответственно с третьим выходом распределителя 4 и входом 24 устройства, выход ключа 26 подключен к счетным входам счетчиков 6 и 7, выход ключа 25 соединен с входада регистров 8 и 9, а выход регистра 9 подключен к информационному входу счетчика 7. На фиг. 2а приведен пример выполнения распределителя 4, содержащего последовательно соединенные элементы И-НЕ 29. Вход первого элемента 29 и выход последнего элемента 29 подключен к входу 19 и выходу 22 распределителя 4, а его входы 18 и 19 соединены соответственно с выходами 21 и 20. Временная диаграмма сигналов на входах 18 и 19 и выходу 22 распределителя 4 приведена на фиг. 26. На фиг. 3 дан пример выполнения коммутатора 5 режима, содержащего элементы И 30-37 и элементы ИЛИ 38 и 39. Устройство обеспечивает работу в режимах Запись, Считывание, Выборка, Контроль информации и работает следующим образом. В режиме Запись из контроллера АИС (не показан) пО линии 13 на вход коммутатора 5 поступает сигнал, соответствующий режиму Запись. ,При этом на выходах 15 и 17. коммутатора 5 появляются управляющие потенциалы, которые поступают на вход ключа 27 и через элемент 10 - на вход счетчика 7, подготавливая их к работе. Сигнал начала оаботы с вьосода 21 распределителя 4 лоступает на входы счетчиков 6 и 7 адреса и устанавливает их в нулевое состояние. В регистр 2 3 поступает начальный код адреса. С приходом на вход 19 первого синхроимпульса распределитель 4 формирует импульс запроса, который с выхода 20 поступает на регистр 1 и на вход разрешения дешифратора 3. Осуществляется запись числа первого слова от первого объекта в первую ячейку блока 28. Далее тактовый импульс с задержкой относительно импульса запроса на время, необходимое для записи, по линии 22 (третий выход распределителя 4) поступает через открытый ключ 26 на счетные входы обоих счетчиков 6 и 7. Однако, поскольку управляющий потенциал на вход разрешения счетчика 6 не подан то прибавление единицы произойдет лишь в счетчике 7. С приходом на вход 19 второго синхроимпульса произойдет запись первого слова от вто рого объекта в следующую ячейку бло ка 28 и так далее до тех пор, пока на выходе счетчика 7 не установится код числа, равного числу опрашиваемых объектов. При этом на выходе переполнения счетчика 7 образуется сигнал, который через элемент ИЛИ 1 поступает на вход разрешения счетчика 6, подготавливая его к рабрте. Следующий тактовый импульс изменяет состояние обоих счетчиков. В мла шем разряде счетчика 6 устанавливается 1, а счетчик 7 переходит в нулевое состояние, после чего управляюший потенциал на входе разрешения счетчика 6 снимается. С прихо дом импульса запроса в блок 28 записывается второе слово от первого объекта, в следующем такте - второе слово от второго объекта и т.д. Работа устройства в этом режиме продо жается до тех пор, пока на всех первых выходах счетчика 6 не установится I. Тогда на выходе переполнеиия этого счетчика образуется сигнал переполнения, который через открытый ключ 27 поступит на первьй вход элемента 1-2,с приходом на второй вход которого .игнала переполнения с выхода счетчика 7 формирует ся управляющий сигнал, который с вы хода 23 поступает в контроллер АИС и прекращает работу устройства в режиме Запись. В режиме Считывание управляющий сигнал, соответствующий данному режиму работы, по линии 13 поступа18. 4 ет на вход коммутатора 5 и при этом на выходах 16 и 17 появляются потенциалы, поступающие, на ключ 27 и через элемент ИЛИ 11 - на вход разрещения счетчика 6. По сигналу Начало работы все разряды обоих счетчиков устанавливаются в нулевое состояние. С приходом первого синхроимпульса распределитель 4 форми- pysT импульс запроса на выходе 20, а на выходе регистра I появляется код числа первого слова объекта. Тактовый импульс проходит с выхода распределителя 4 по линии 22 через открытый ключ 26 на счетные входы счетчиков 6 и 7 и в младшем разряде счетчика 6 устанавливается 1. С приходом второго синхроимпульса на выходе регистра 1 появляется код числа второго слова первого объекта, а счетчик 6 переходит в следующее состояние, и так до тех пор, пока все числа, соответствуюпше первому объекту, не считаны. Затем с выхода переполнения счетчика 6 на вход разрешения счетчика 7 через ключ 27 и элемент ИЛИ 10 подается управляющий сигнал. Следующий тактовый импульс перебрасывает первый разряд счетчика 7 в состояние 1, а все разряды счетчика 6 устанавлирает в нулевое состояние, что соответствует коду адреса первого слова второго объекта. Аналогичным образом осуществляется считывание, последующих слов второго объекта и т.д. После того, как закончится считывание чисел последнего объекта, на оба входа элемента 12 с выходов счетчиков 6 и 7 через ключ 27 поступают управляющие сигналы, и элемент 12 формирует сигнал переполнения, после чего работа устройства в режиме считывания прекращается . В режиме Контроль информахуш управляющий сигнал, соответствующий режиму- Считывание, поступает на линию 13, а на линию 14 - сигнал, соответствующий режиму Контроль информации. При этом управляющий потенциал устанавливается лишь на выходе 16 коммутатора 5. Ключ 27 переходит в закрытое состояние. На выходе счетчика 7 с помощью регистра 9 устанавливается код, соответствующий номеру контролируемого объекта. С.приходом синхроимпульсов распределитель 4 формирует импульсы запроса и тактовые и пyльcы, поступаккцие на счетные входы счетчиков 6 и 7. Однако, поскольку сигналы переполнения, появляющиеся на выход счетчика 6 через ключ 27, на вход разрешения счетчика 7 не проходят, то его состояние не меняется, и сиг кал переполнения на выходе элемента 2 не формируется. Счетчик 6 работа ет в циклическом режиме, поэтому происходит периодическое считывание чисел .одного объекта. В режиме Выборка с помощью регистров 8 и 9 устанавливается начапьный адрес первого слова, после чего подается потенциальный сигнал Выборка 24, который переводит клю 26 в закрытое состояние, а ключ 25 в открытое состояние на все время 8 выборки (в этом режиме контроллер АИС не реагирует на сигнал переполнения 23). С приходом первого синхроимпульса распределитель 4 формирует импульс запроса на выходе 20, на выходе регистра I появляется код числа слова, адрес которого задан Содержимым регистров 8 и 9. Тактовый импульс проходит с третьего выхода распределителя 4 по линии 22 через открытый ключ 25 и разрешает смену содержимого регистров 8 и 9. Заранее намеченная последовательность слов может вводиться в регистры 8 и 9 вручную или автоматически (например, с помощью фотосчитывателя с перфоленты). После завершения выборки определенной группы слов сигнал Выборка снимается, ключ 25 закрывается, а ключ 26 открывается.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух асинхронных магистралей | 1986 |

|

SU1403083A1 |

| Устройство для управления блокомпАМяТи | 1978 |

|

SU809345A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для сопряжения абонентов с каналами связи | 1985 |

|

SU1262510A1 |

| Программируемый контроллер | 1989 |

|

SU1741100A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для контроля цифровых узлов | 1987 |

|

SU1571593A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1992 |

|

RU2032938C1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ БЛОКОМ ПАМЯТИ, содержащее регистр числа, регистр адресаj дешифратор адреса, распределитель импульсов, коммутатор режима, два счетчика адреса, первый регистр константы, первый ключ, два элемента ИЛИ и элемент И-НЕ, первый вход и выход которого соединены соответственно с выходом первого ключа и выходом признака устройства, синхровход и вход запуска распределителя импульсов подключены к синхровходу устройства, первый выход распределителя импульсов соединен с входом раэре-. шения дешифратора адреса и синхровходом регистра числа, первый и второй информационные входы-выходы которого подключены соответственно к информационному входу-выходу устройства и информационному входу-выходу блока памяти, адресный вход которого соединен с выходом дешифратора адреса, первый и второй информационные входы и выход регистра адреса подключены соответственно к информационным выходам первого и второго счетчиков адреса и информационному входу дешифратора адреса, входы установки нуля счётчиков адреса соединены с вторым выходом распределителя импульсов, первый, второй и третий выходы и вход коммутатора режима подключены соответственно к первым входам первого и второго элементов ИЛИ, управляющему входу первого ключа и входу режима устройства, входы разрешения записи первого и второго счетчиков адреса соединены с выхода соответственно второго и первого элементов ИЛИ, вторые входы которых подключены соответственно к выходу переполнения второго счетчика адре-. са и выходу первого ключа, информационный вход и выход переполнения (Л первого счетчика адреса соединены .соответственно с выходом первого регистра константы и информационным ;входом первого ключа, а выход пере-, полнения второго счетчика адреса подiключей к второму входу элемента ИНЕ, отличающееся тем, что, с целью расширения области приа менения устройства за счет реализации ts считывания произвольно назначенной единицы, оно содержит второй регистр константы, второй и третий ключи, Х управляющие и информационные входы которых соединены соответственно с третьим выходом распределителя импульсов и входом разрешения опроса устройства, выход второго ключа подключен к счетным входам первого и второго счетчиков адреса, выход третьего ключа соединен с входами первого и второго регистров константы, а выход второго регистра, константы подключен к информационно входу второго счетчика адреса.

fput.1

IB 19

гг

fU-ri -JI

П-П,..

t

s

(put, 2

j/ гС

30

и

15

3S

ч:

зв

39

-С

J7

(риг.З

| Устройство для управления оперативным накопителей | 1972 |

|

SU463145A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство | 1976 |

|

SU608197A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для управления блокомпАМяТи | 1978 |

|

SU809345A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-06-30—Публикация

1982-02-23—Подача