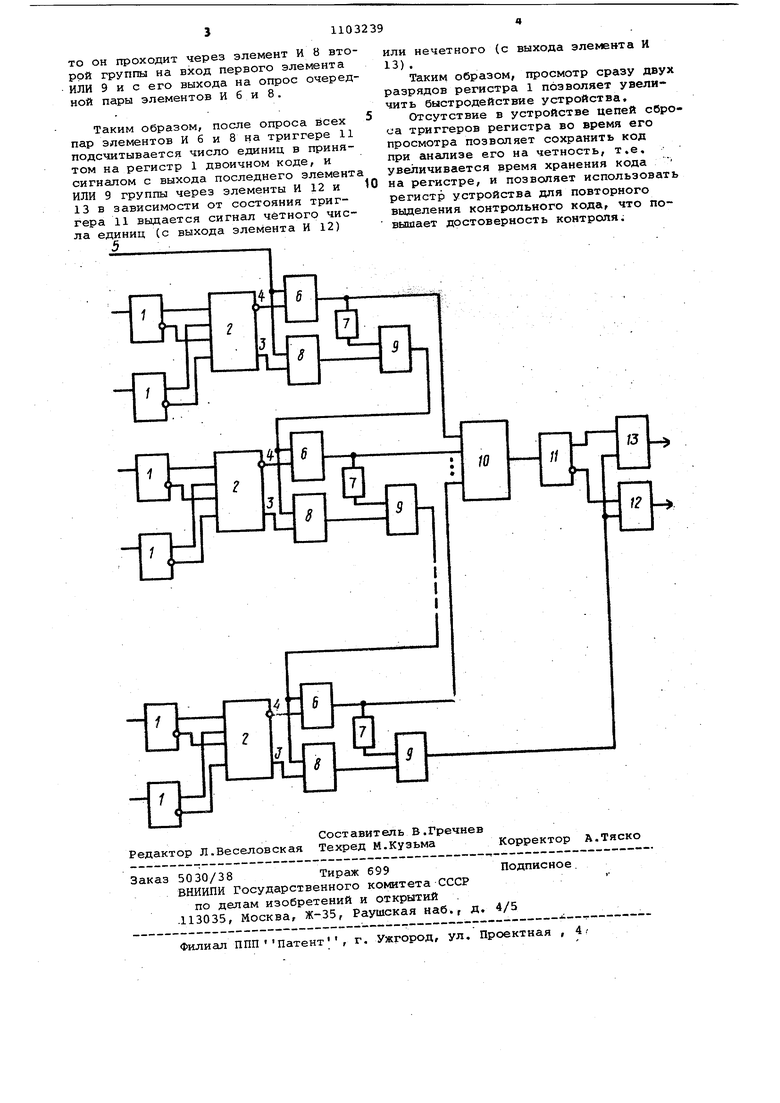

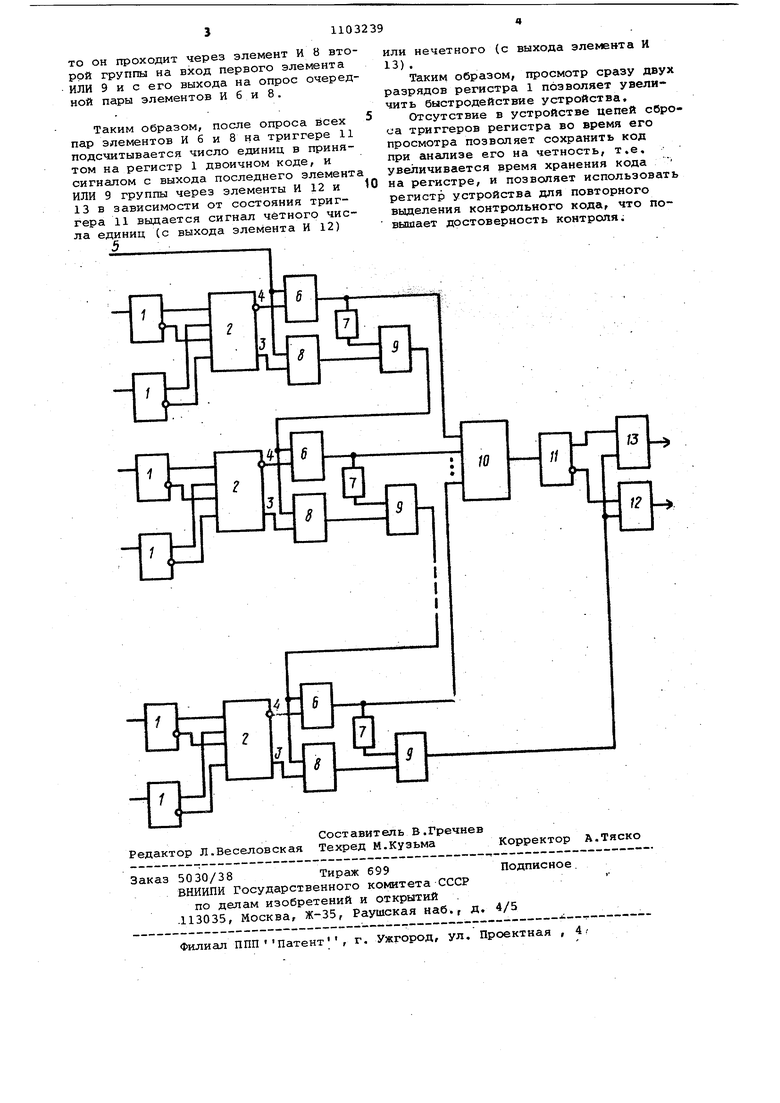

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в цифровы вычислительных устройствах для обна ружения ошибок при передаче информа ции в двоичном коде. Известно устройство дхйи контроля параллельного кода на четность, при цип работы которого основан на сдвиг контролируемого кода , содержащее сдв гающий регистра ,элемент И и триггер Нэвысокое быстродействие этого устройства обусловлено поразрядным сдвигом информации в регистре при анализе ее на четность. Наиболее близким по техническому решению к предлагаемому является устройство для определения четности информации) содержащее регистр, раз рядные входы которого являются первыми входами устройства, элемент за держки, три элемента И, элемент ИЛИ выход которого соединен со счетным входом триггера, выходы -которого соединены с первыми входами двух эл ментов И, выходы которых являются вы ходами устройства, единичные и нуле вые выходы регистра соединеныс пер выми входами соответствующих элемен тов И первой И второй группы, выхо ды элементов И первой группы соединены с нулевыми -входами соответствующих разрядов регистра и соответствующими входами элемента ИЛИ, вых каждого i-ro элемента И второй группы соединен с вторыми входами (i+1) -х элементов И первой и второй групп (1 1 i п, где п - разрядность регистра) 2. Недостатком устройства также явля ется недостаточное быстродействие и уничтожение информации на регистре при ее контроле. Цель изобретения - повышение достоверности контроля и быстродействия Поставленная цель достигается: .. тем, что в устройство для контроля параллельного кода на четность, содержащее регистр, две группы элементов И, элемент ИЛИ,-триггер и два элемента И, причем выходы элементов И первой группы соединены с соответствующими входами элемента ИЛИ, выход которого соединен со счетным входом триггера, единичный и нулевой выходы которого соединены с первыми входами соответственно первого и втО рого элементов И, вторые входа которых объединены, первый вход каждого i-ro элемента И первой группы (1 «: 1 h/2, где п -разрядность регистра) соединен с первым входом iго элемента И второй группы, информационные входы регистра являются информационными входами устройства, выходы первого и второго элементов И являютс выходами устройства, введены группа узлов свертки по модулю два, группа элементов ИЛИ и группа элементов задержки, причем выходы каждых (21-1) и 2i-ro разрядов регистра соединены Свходами i-ro узла свертки по модулю два группы (1 i i п/2 ) , выходы нечетности и четности каждого i-ro узла свертки по модулю два соединены с вторыми входами i-x элементо-в И первой и второй групп соответственно,, выход каждого i-ro Элемента И первой группы через соответствующий элемент задержки группы соединен с первым входом i-ro элемента ИЛИ группы, вттброй вход которого соединен с выходом i-ro элемента и второй группы, выход кажого j-ro элемента ИЛИ группы соединен с первым входом (j+.)-ro элемента И первой группы (1 j п/2 ), первый вход первого элемента И первой группы является входом запуска устройства, выход п/2 -го элемента ИЛИ группы соединен с вторым входом первого элемента И. На чертеже приведена функционгшьная схема устройства для контроля параллельного кода на-четность. Устройство содержит регистр I,группу 2 узлов свертки по модулю, два, выходы 3 четности и выходы 4 нечетности узлов свертки по модулю два группы 2, вход 5 запуска устрой, ства, первую группу б элементов И, группу 7 элементов задержки, вторую группу 8 элементов И, группу 9 элементов ИЛИ, элемент ИЛИ 10, триггер II,элементы И 12 и 13 Устройство работает следую1цим образом. На информационные входы регистра 1 поступает п-разрядный двоичный код. Узлы 2 свертки по модулю два группы для каждых двух разрядов регистра 1 формируют сигнал, соответствующий четному числу единиц, снимаемый с выхода 3, или нечетному чис лу единиц, снимаемый с выхода 4, По сигналу запуска, который поступает на вход 5 устройства, в зависимости от наличия сигнала с выхода 3 или 4 на выходе первых элементов и б или 8появляется сигнал. Если сигнал снимается с выхода 4, то с выхода первого элемента И б первой группы он поступает на вход элемента ИЛИ 10, а с его выхода-на счетный вход триггера 11. Одновременно этот сигнал с выхода первого элемента И б первой группы через элемент 7 задержки, обеспечивающий задержку сигнала на время переключения триггера 11, поступает через элемент ИЛИ 9группы на опрос очередной пары элементов И первой 6 и второй 8 групп. Если сигнал снимается с выхода 3 узла 2, принимающего сигналы от вух младших разрядов регистра 1,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для контроля 2-кода Фибоначчи | 1988 |

|

SU1662009A1 |

| Устройство для контроля дешифратора | 1987 |

|

SU1495801A1 |

| Устройство для контроля двухтактного двоичного счетчика | 1981 |

|

SU970375A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля двухтактного двоичного счетчика | 1975 |

|

SU607221A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Устройство для контроля передачи информации | 1987 |

|

SU1525702A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАЛЛЕЛЬНОГО КОДА НА ЧЕТНОСТЬ, содержашее регистр, две группы элементов И, элемент ИЛИ, триггер и два элемента И, причем выхоцы элементов И первой гругшы соединены с соответствующими вхсЗдами элемента ИЛИ, выход которого соединен со счетным входом триггера, единичный и нулевой выходы которого соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых объединены, первый вход каждого i-го элемента И первой группы

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1974 |

|

SU530332A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Асинхронное устройство для определения четности информации | 1973 |

|

SU552609A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-15—Публикация

1983-02-16—Подача