1

Изобретение относится к области вычислительной техники и может быть использовано для проверки на четность информании, принимаемой в параллельном виде.

Известны асинхронные устройства для онределения четности информации, принимаемой в параллельном виде, позволяющие обнаружить наличие любого нечетного числа ошибок в этой информации.

Одно из известных устройств содержит п задержанных мультивибраторов, каждый из которых имеет свою, отличную от других мультивибраторов, длительность нахождения в возбужденном состоянии. Запускаются только те мультивибраторы, на вход которых приходит символ «1. Далее выходы мультивибраторов через дифференцирующие цепи соединены с элементом ИЛИ. С элемента ИЛИ последовательность импульсов поступает на вход триггера, выходы которого соединены с элементами И. Для опроса элементов И и определения четности используется специальный генератор 1.

Наиболее близкое по техническому решению к изобретению асинхронное устройство для онределения четкости информации содержит регистр, разрядные входы которого служат входами устройства, элемент ИЛИ, выходом соединенный со счетным входом триггера, выходы которого подключены к первым

входам двух элементов И, выходы элементов И являются выходами устройства 2.

Однако известные устройства сложны, не обеснечивают возможности построния из интегральных микросхем и имеют больщое время декодирования, которое равно л т, где т - минимальное допустимый временной интервал между импульсами генератора, п - разрядность числа.

Цель изобретения - унрощение устройства и новыщение его быстродействия.

Это достигается тем, что устройство содержит второй и третий элементы ИЛИ, элементы И, второй триггер и элемент задержки. Входы устройства соединены с входами второог элемента ИЛИ, выходом связанного с входом элемента задержки и с входом установки в единицу второго триггера, выходы второго триггера и элемента задержки - с входами третьего элемента И, выход которого подключен к одному из входов второго элемента ИЛИ и к первым входам четвертого и пятого элементов И, вторые входы которых соединены с выходами первого разряда регистра. Выход пятого и последующих нечетных элементов И соединены с первыми входами двух следующих элементов И, вторые входы которых соединены с выходами следующего разряда регистра, выходы четвертого и последующих четных элементов И - с входами первого элемента ИЛИ и с входами установки в нуль соответствующего разряда регистра, выход последнего элемента И - с вторыми входами первых двух элементов И, выходы которых подключены к входам третьего элемента ИЛИ, а выход третьего элемента ИЛИ связан с входами установки в нуль первого и второго триггеров.

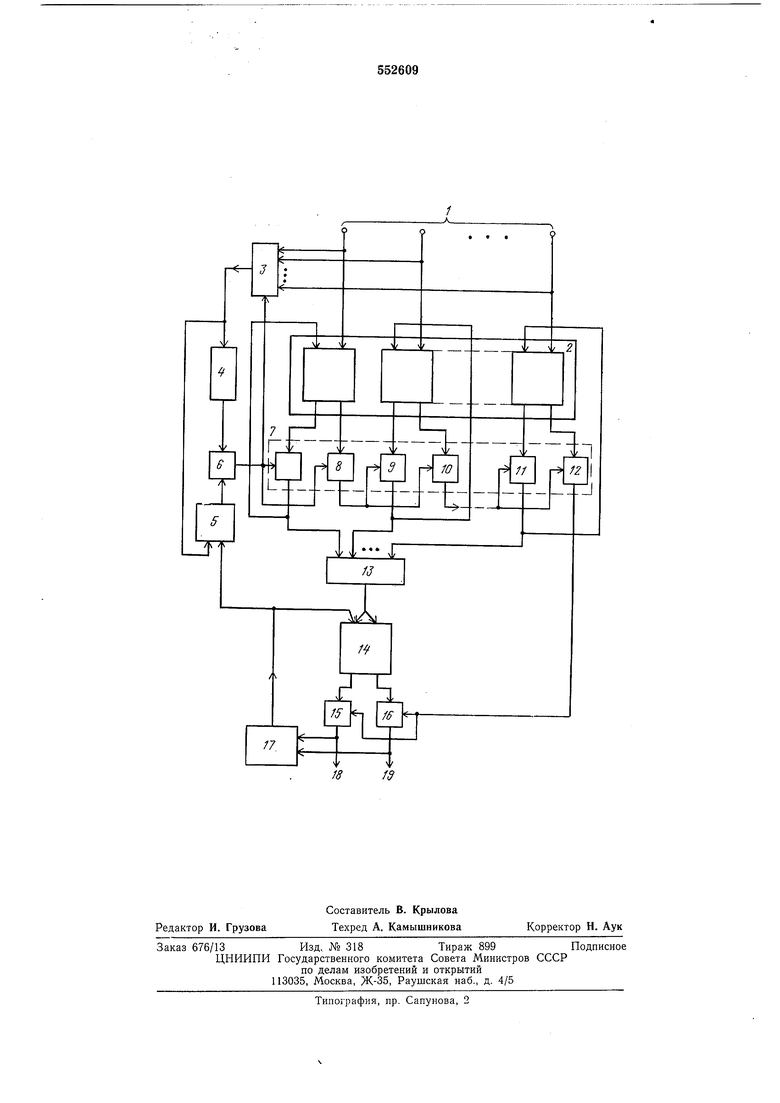

На чертеже представлена блок-схема предлагаемого устройства.

Входы 1 устройства соединены с входами регистра 2 и с входами элемента ИЛИ 3, выход элемента ИЛИ - с входом элемента 4 задержки и входом записи единицы триггера 5. Выход элемента 4 задержки подключен к одному входу элемента И 6, другой вход которого соединен с выходом триггера 5, выход элемента И 6 - к входу элемента ИЛИ 3 и к входам элементов И 7 и 8, вторые входы которых соединены соответственно с единичным и нулевым выходами первого разряда регистра 2. Выход элемента И 8 подключен к входам элементов И 9 и 10, вторые входы которых связаны соответственно с единичным и нулевым выходами второго разряда регистра 2. Входы элементов И 11 и 12 соединены аналогично входам элементов И 9 и 10. Выходы элементов И 7, 9, 11 подсоединены к входам элементам ИЛИ 13 и к входу установки в нуль своего разряда регистра 2, выход элемента ИЛИ 13 - к счетному входу триггера 14, выходы которого соединены с элементами И 15 и 16, вторыми входами связанными с выходом последнего элемента И 12. Выходы элементов И 15 и 16 соединены с входами элемента ИЛИ 17 и с выходами 18 (четность) и 19 (нечетность) устройства. Выход элемента ИЛИ 17 подключен к установке в нуль триггеров 5 и 14.

Входная информация, записанная в виде «-разрядного кода, поступает в параллельном виде на входы 1 устройства и записывается в регистр 2. Одновременно все входные импульсы подаются на элемент ИЛИ 3, с выхода которого импульс, соответствующий моменту записи, поступает на вход элемента 4 задержки и на единичный вход триггера 5.

Триггер 5 устанавливается в единичное состояние и открывает элемент И 6. Через время т, соответствующее времени задержки элемента 4, импульс через открытый элемент И 6 поступает на вход элемента ИЛИ 3 и входы элементов И 7 и 8. Элементы И 7,9, 11 подсоединены к таким выходам соответствующего разряда регистра 2, что импульс через них проходит лишь в том случае, когда в разряде записана «1. Наоборот, через элементы И 8, 10, 12 импульс проходит лищь тогда, когда в соответствующем разряде регистра 2 записан «О. Таким образом, если в первом разряде регистра 2 записана «1, то импульс с выхода элемента И 6 попадает через элемент И 7 на вход элемента ИЛИ 13. Одновременно с выхода элемента И 7 импульс поступает на вход установки в нуль первого разряда регистра 2.

Следующий импульс с выхода элемента 4 задержки вновь подается через элемент И 6 на входы элементов И 7 и 8, однако, теперь первый разряд регистра 2 находится в нулевом положении и этот импульс проходит через элемент И 8 на вход элементов И 9 и 10. Эти два элемента И работают соверщенно аналогично предыдущим двум элементам И, а определяется их работа положением второго разряда регистра 2. Если во втором разряде регистра 2 записана «1, то импульс проходит через элемент И 9 на элемент ИЛИ 13 и на установку в нуль второго разряда регистра 2, а следующий импульс - через элемент И 10. Если же во втором разряде регистра 2 записан «О, то импульс сразу проходит на элемент И 10, на следующие элементы И и т. д. С выхода элемента ИЛИ 13 импульсы, соответствующие символам «1 во входной информации, поступают на счетный вход триггера 14. С выхода последнего элемента И 12 импульс попадает на входы элементов И 15 и 16. Если число единиц в информации четное,

то импульс проходит через элемент И 15 на выход 18, что свидетельствует об отсутствии ощибок, если нечетное, то импульс проходит через элемент И 16 на выход 19, что свидетельствует о наличии ошибки. Через элемент

Р1ЛИ 17 любой из этих импульсов поступает на входы установки в нуль триггеров 5 и 14, это приводит схему в исходное состояние.

Легко показать, что среднее время декодирования здесь меньше, чем в прототипе. Действительно, время декодирования здесь опре деляется числом единиц в кодовом слове. По скольку все слова равновероятны, то

Гер (С°„,+ c2T-f ... + C(i+ l)t+

+ ...+С + (й+1)г)г|;(/+1)С,

(n + 2)-:

П7 Т 2

Нрэдлагаемое устройство проще прототипа, поскольку здесь отсутствуют генераторы, не требуется синхронизация генераторов с приходящим кодовым словом; схема обладает в среднем в два раза большим быстродействием. Кроме того, схема более технологична, поскольку все ее элементы могут быть выполнены на интегральных микросхемах. Заметим,

что величина т может быть выбрана достаточно малой (единицы или доли микросекунды) и определяется лишь быстродействием триггера 14. Кроме того, предлагаемое устройство при

сохранении практически всех его связей может быть использовано для обнаружения ошибок в параллельно принимаемой информации, если последняя закодирована кодом постоянного веса W. Для этого достаточно вместо

триггера 14 применить обычный двоичный

счетчик, фиксирующий наличие точно W единиц в принятой информации.

Формула изобретения

Асинхронное устройство для онределения четности информации, содержащее регистр, разрядные входы которого являются входами устройства, элемент ИЛИ, выходом соединенный со счетным входом триггера, выходы которого соединены с первыми входами двух элементов И, выходы элементов И являются выходами устройства, отличающееся тем, что, с целью упрощения и повышения быстродействия, устройство содержит второй и третий элементы ИЛИ, элементы И, второй триггер и элемент задержки, причем входы устройства соединены с входами второго элемента ИЛИ, выход которого соединен с входом элемента задержки и с входом установки в единицу второго триггера, выходы второго триггера и элемента задержки соединены с входами третьего элемента И, выход которого соединен с одним из входов второго элемента

ИЛИ и с первыми входами четвертого и пятого элементов И, вторые входы которых соединены с выходами первого разряда регистра, выход пятого и последующих нечетных

элементов И соединены с первыми входами двух следующих элементов И, вторые входы которых соединены с выходами следующего разряда регистра, выходы четвертого и последующих четных элементов И соединены с

входами первого элемента ИЛИ и с входами установки в нуль соответствующего разряда регистра, выход последнего элемента И соединен с вторыми входами первых двух элементов И, выходы которых соединены с входами третьего элемента ИЛИ, выход третьего элемента ИЛИ соедйпен с входами установки в нуль первого и второго триггеров.

Источники информации, принятые во внимание при экспертизе изобретения

1. Патент США № 3487363 кл. 340-146.1, 1967.

2. Патент США ДСо 2719959, кл. 340-146.1, 1955 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронное устройство для определения четности информации | 1978 |

|

SU767765A2 |

| Устройство для контроля двоичного кода на нечетность | 1981 |

|

SU1012261A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU997038A1 |

| Устройство для извлечения квадратного корня | 1972 |

|

SU439805A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля регистра сдвига | 1981 |

|

SU964646A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для формирования контрольного кода по четности | 1980 |

|

SU934477A1 |

Авторы

Даты

1977-03-30—Публикация

1973-12-04—Подача