. t12

Изобретение относится к вычислительной технике и может быть использовано в биполярных статических запоминающих устройствах.

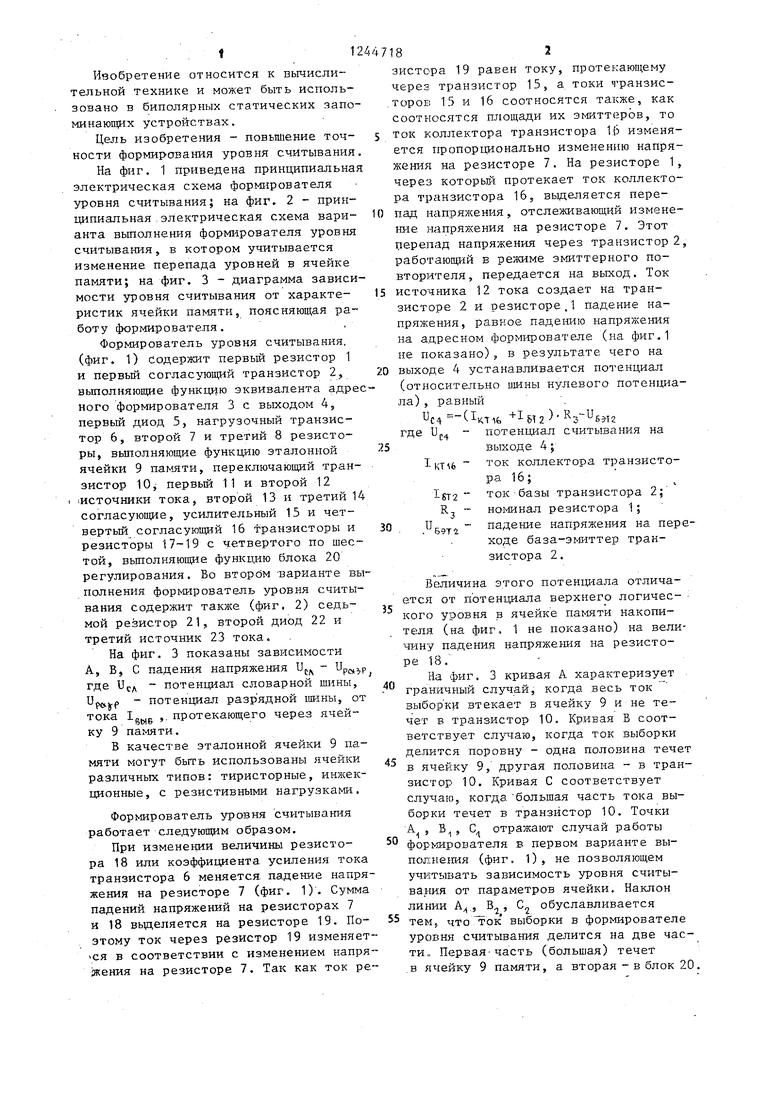

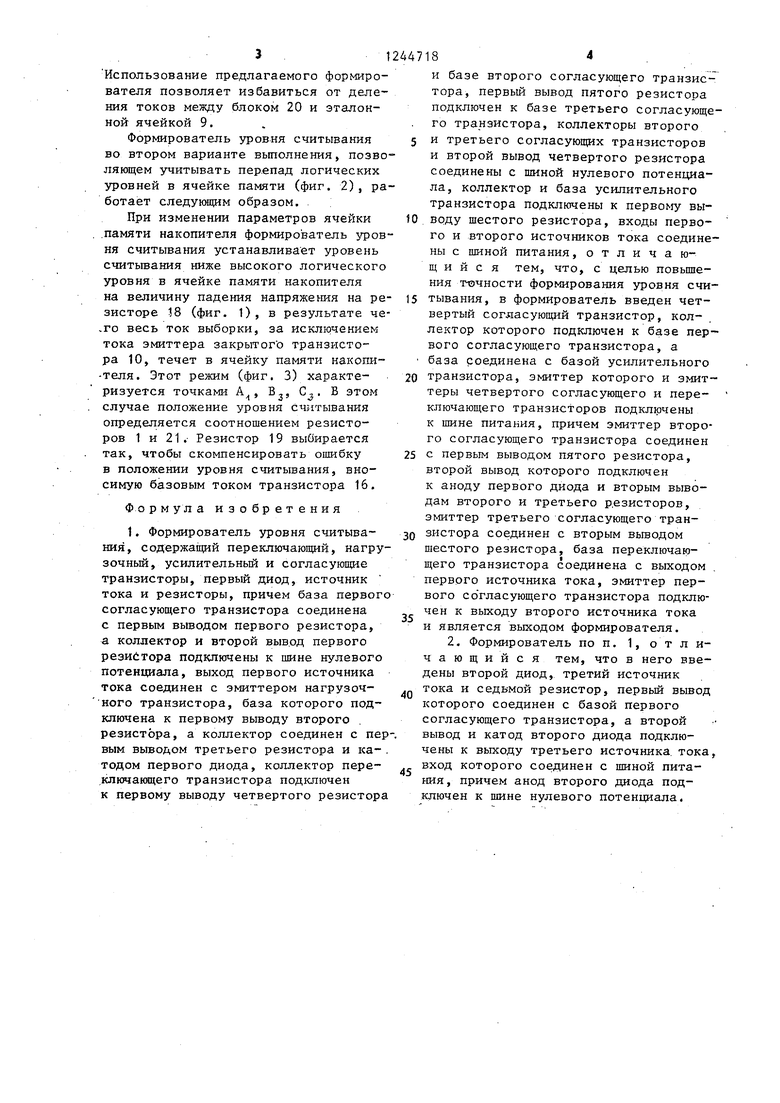

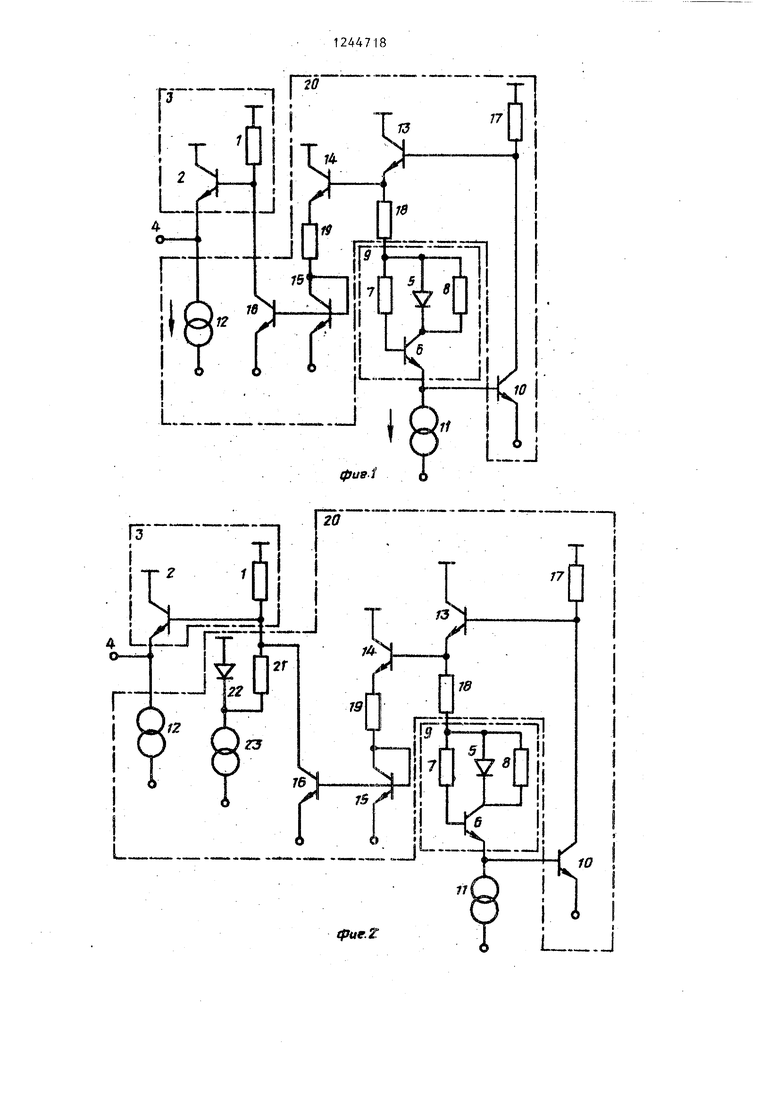

Цель изобретения - повышение точ ности формирования уровня считывания. На фиг. 1 приведена принципиальная электрическая схема формирователя уровня считывания; на фиг. 2 - принципиальная , электрическая схема вари- акта выполнения формирователя уровня считывания, в котором учитывается Изменение перепада уровней в ячейке памяти; на фиг. 3 - диаграмма зависимости уровня считывания от характе- ристик ячейки памяти, поясняющая работу формирователя.

Формирователь уровня считывания, (фиг. 1) Содержит первый резистор 1 и первый согласующий транзистор 2, вьшолняющие функ1щю эквивалента адресного формирователя 3 с выходом 4, первый диод 5, нагрузочный транзистор 6, второй 7 и третий 8 резисторы, вьшолняющие функцию эталонной ячейки 9 памяти, переключающий транзистор 10, первьй 11 и второй 12 (ИСТОЧНИКИ тока, второй 13 и третий 14 согласующие, усилительный 15 и четвертый согласующий 16 транзисторы и резисторы 17-19 с ч.етвертого по шестой, вьшолняющие функцию блока 20 регулирования. Во втором варианте выполнения формирователь уровня считывания содержит (фиг. 2) седь- мой резистор 21, второй диод 22 и третий источник 23 тока.

На фиг. 3 показаны зависимости А, В, С падения напряжения U - .p где - потенциал словарной шины, потенциал разрядной шины, от тока ,. протекающего через ячейку 9 памяти.

В качестве эталонной ячейки 9 памяти могут быть использованы ячейки различных типов: тиристорные, инжек- ционные, с резистивными нагрузками.

Формирователь уровня считывания работает следующим образом.

При измене ши величины резисто- ра 18 или коэффициента усиления тока транзистора 6 меняется падение напряжения на резисторе 7 (фиг, 1). Сумма падений напряжений на резисторах 7 и 18 выделяется на резисторе 19. По- этому ток через резистор 19 изменяет ся в соответствии с изменением напря жения на резисторе 7. Так как ток ре182

зистора 19 равен току, протеь;ающему через транзистор 15, а токи ч ранзис- торов 15 и 16 соотносятся также, как соотносятся площади их эмитт(5ров, то ток коллектора транзистора lii изменяется пропорционально изменению напряжения на резисторе 7. На резисторе 1, через которьй протекает ток коллектора транзистора 16, вьщеляется перепад напряжения, отслеживающий изменение напряжения на резисторе 7. Этот перепад напряжения через транзистор 2 работаюгций в релшме змиттерного повторителя, передается на вьгход. Ток источника 12 тока создает на транзисторе 2 и резисторе. 1 падение напряжения, равное падению напряжения на адресном формирователе (на фиг.1 не показано), в результате чего на выходе 4 устанавливается потенциал (относительно шины нулевого потенциала) , равный

Uc где Uj - потенциал считывания на

выходе 4;

ток коллектора транзистора 16; IsT2 ток базы транзистора 2;

-с KTib .-лг

R,

номнвап резистора 1;

&9Ti падение напряжения на переходе база-эмиттер транзистора 2.

Величина этого потенциала отличается от потенциала верхнего логичес- кого уровня в ячейке памяти накопителя (на фиг, 1 не показано) на величину падения напряжения на резисторе 18.

На фиг. 3 кривая А характеризует граничный случай, когда весь ток выборку втекает в ячейку 9 и не течет в транзистор 10, Кривая В соответствует случаю, когда ток выборки делится поровну - одна половина течет в ячейку 9, другая половина - в транзистор 10. Кривая С соответствует случаю, когда больщая часть тока выборки течет в транзистор 10. Точки А , В, С отражают случай работы формирователя в первом варианте выполнения (фиг. 1), не позволяющем учитывать зависимость уровня считывания от параметров ячейки. Наклон линии А., В, С„ обуславливается тем, выборки в формирователе уровня считывания делится на две части,, Первая-часть (большая) течет .в ячейку 9 памяти, а вторая - в блок 20

3 .1

Использование предлагаемого формирователя позволяет избавиться от деления токов между блоком 20 и эталонной ячейкой 9. .

Формирователь уровня считывания во втором варианте выполнения, позволяющем учитывать пер.епад логических уровней в ячейке памяти (фиг. 2), работает следующим образом.

При изменении параметров ячейки .памяти накопителя формирователь уровня считывания устанавливает уровень считьгоания ниже высокого логического уровня в ячейке памяти накопителя на величину падения напряжения на ре- зисторе 18 (фиг. 1), в результате че- ,го весь ток выборки, за исключением тока эмиттера закрытог о транзисто ра 10, течет в ячейку памяти накопи- -теля. Этот режим (фиг. 3) характе- ризуется точками А, В, С. Б этом случае положение уровня считывания определяется соотношением резисторов 1 и 21. Резистор 19 выбирается так, чтобы скомпенсировать ошибку в положении уровня считывания, вносимую базовым током транзистора 16.

Формула изобретения

1. Формирователь уровня считыва- ния, содержащий переключающий, нагрузочный, усилительный и согласующие транзисторы, первый диод, источник тока и резисторы, причем база первого согласующего транзистора соединена с первым выводом первого резистора, а коллектор и второй выв.од первого резистора подключены к шине нулевого потенциала, выход первого источника тока соединен с эмиттером нагрузоч- ного транзистора, база которого подключена к первому выводу второго резистора, а коллектор соединен с пер вым вьюодом третьего резистора и ка- тодом первого диода, коллектор пере- .ключакнцего транзистора подключен к первому выводу четвертого резистора

5

0 5 0 5

о

5

18

и базе второго согласующего транзистора, первый вывод пятого резистора подключен к базе третьего согласующего транзистора, коллекторы второго и третьего согласующих транзисторов и второй вывод четвертого резистора соединены с шиной нулевого потенциала, коллектор и база усилительного транзистора подключены к первому выводу шестого резистора, входы первого и второго источников тока соединены с шиной питания, отличающийся тем, что, с целью повьшге- ния точности формирования уровня считывания, в формирователь введен четвертый согласующий транзистор, коллектор которого подключен к базе первого согласующего транзистора, а база соединена с базой усилительного транзистора, эмиттер которого и эмиттеры четвертого согласующего и переключающего транзисторов подключены к шине питания, причем эмиттер второго согласующего транзистора соединен с первым выводом пятого резистора, второй вывод которого подключен к аноду первого диода и вторым выводам второго и третьего р.езисторов, эмиттер третьего согласующего транзистора соединен с вторым выводом шестого резистора, база переключающего транзистора соединена с выходом первого источника тока, эмиттер первого со гласующего транзистора подключен к выходу второго источника тока и является выходом формирователя.

2. Формирователь по п. 1, отличающийся тем, что в него введены второй диод, третий источник тока и седьмой резистор, первый вывод которого соединен с базой первого согласующего транзистора, а второй вывод и катод второго диода подключены к выходу третьего источника, тока, вход которого соединен с шиной питания , причем анод второго диода подключен к шине нулевого потенциала.

L...

фusi

iJj

Гз

r-l r

.Z

Ii

Фие.З

и ел и разр

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Параметрический источник опорного напряжения для запоминающего устройства | 1989 |

|

SU1647647A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Формирователь сигнала для выборки элементов матрицы | 1982 |

|

SU1045364A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Формирователь сигналов считывания | 1984 |

|

SU1238152A1 |

Изобретение относился к вь1числи- тельной технике и может быть использовано в биполярных статических запоминающих устройствах. Целью изобретения является повышение точности формирования уровня считывания. Формиро тватель уровня Считывания содержит . переключающий, нагрузочный, усилительный и три согласующих транзистора, первьй диод, два источника тока, шесть резисторов. Повышение точности . формирования уровня считывания достигается введением четвертого согласующего транзистора, .что обеспечивает увеличение тока, протекающего через нагрузочный транзистор. Введение в формирователь второго диода, третьего источника тока и седьмого резистора позволяет учесть перепад логических уровней. 1 з.п.. ф-лы, 3 ил. о ю 4

| Патент США № 4099070, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Эмульсионный буровой раствор | 2020 |

|

RU2738187C1 |

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1986-07-15—Публикация

1984-10-01—Подача