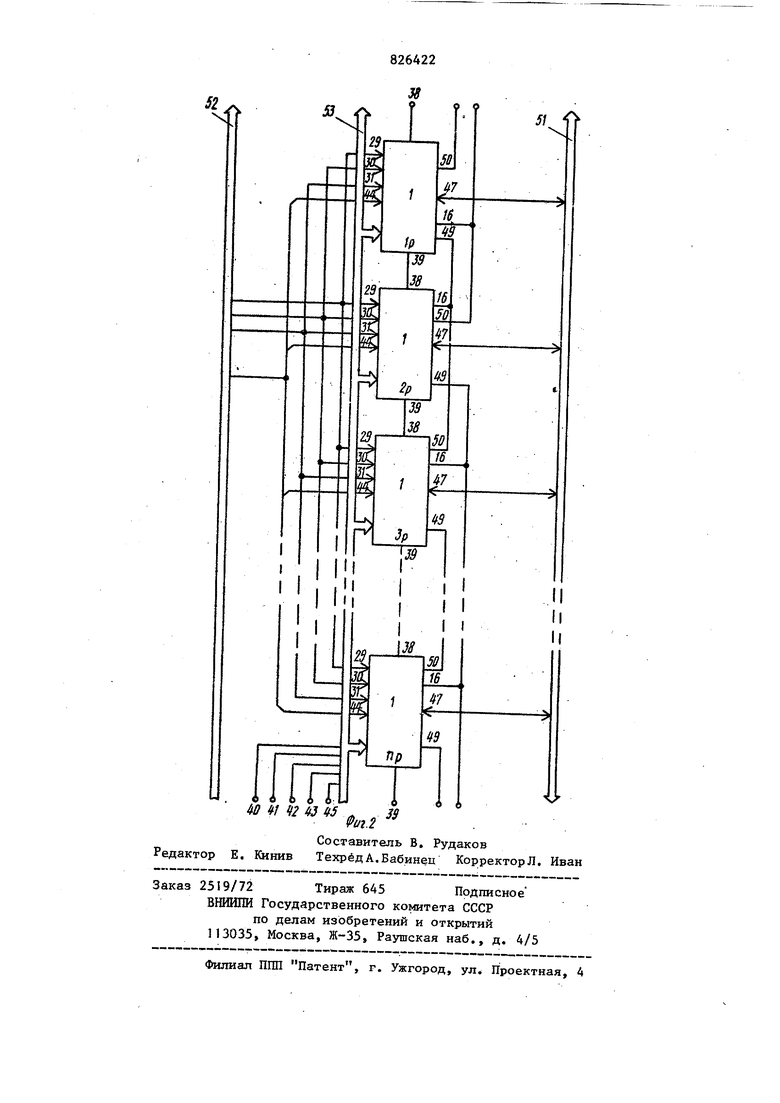

Изобретение относится к запоминающим устройствам. Известный блок логической памяти содержит два адресно-числовых регис ра, управляющий вход первого из кото pbix соединен с выходом первого разря да регистра адреса, а управляю-дий вход второго- с выходом второго адреса,вы ходы первого адресно-числового регист ра соединены с адресными входами первых разрядов накопителей, а выходы второго - с адреснымивходами вторых разрядов накопителей l. Недостатком этого блока является низкая производительность при выполнении операции суммирования и вычи тания вследствие многократного выполнения поразрядных логических операций и операции сдвига на один разряд при распространении волны переносов (или заемов). Наиболее близким техническим решением к предпагаемому изобретению является блок логической памяти. содержащий элементы памяти, выходы которых соединены с соответствующими информационными входами регистра числа, регистров первого и второго операндов, выход каждого разряда рет гистра числа соединен с информационным входом соответствующего эле. мента памяти, первый и второй управляющие входы которого являются первым и вторым управляющими входами устройства, выходы разрядов регистра адреса соединены с соответствующими адресными входами элементов памяти, первый и второй адресные входы кото рых соединены с первым и вторым вхо дами коммутаторов, первый и второй информационные входы которых соединены с выходами соответствукрцх разрядов регистра первого и второ1о операндов, первый и второй управляющие входы коммутаторов являются третьими и четвертым управляющими входами устройства соответственно, блок коммутации, первый и второй информационные зходы которого соединены с выходами первого и второго разрядов реггиетра адреса соотзетственно, пер вый и второй информационные выходы с третьим и четвертым информаци OHiSsSbsj входами ко,ммутаторов, а унрав лякщий вход с пятым управляющим входом устройства, информационный вх каждого ко1 мутатора-, кроме первого соединен с информационным выходом предьвдущего коммутатора, а информационньк выход последнего коммутатора является информационньш вьзходом устройства 2J, Недостатками этого блока являются невьзсокая экономичность структуры, заключающаяся в наличии третьего числового регистра (регистра второго операнда7 и сравнительно большое число связей, нейЬюокая надежность, отсутствие средств реализующих опера ции сдвига числовой информации,что ограничивает область использования блока. Цель изобретения - упрощение и по вьшение надежности блока логической памяти. Поставленная цель достигается тем что в блок логической памяти, содержащий накопитель, коммутаторы адресных сигналов, регистр числа и рег-истр операнда, причем один из входов первого и второго коммутаторов адресных сигналов подключены соответственно к выходам регистра числа и регистра операцца, а выходы - к одним из адресьагх входов накопителя, информационный выход которого соединен с выходом регистра чиапа, а инфор мационный выход соединен со входом ре гистра операнда и является первым ин фор.мационным выходом блока, управляющие входы накопителя первого и второго коммутаторов адресных сигналов являются соответственно первым, вторым и третьим управляющими входами блока, другие входы первого и второго коммутаторов адресных сигналов - первым и вторым адресными входами блока введены третий, четвертый коммутаторы адресных сигналов, формирователь сигнала переноса, коммутатор информационных сигналов и блок согласования, причем первый вход формирователя сигнала, переноса соединен с инфор мационным входом третьего коммутатора адресных сигналов и является информа- ,цнонным входом блока, второй и третий входы соединены соответственно с выходами регистра числа и регистра операнда, а выход является вторым информационным выходом блока, вы-. ход третьего и одни из выходов четвертого коммутаторов адресных сигналов подключены соответственно к другим адресным входам накопителя, выход регистра числа соединен с одним из входов блока согласования, другой вход которого подключен х информационному выходу накопителя и первому входу коммутатора информационных сигналов, а выход соединен со -вторым входом коммутатора информационных сигналов, а выход соединен со вторым входом коммутатора информационных сигналов и с шиной, являющейся вторым информащшнным входом и трегьим информационным выходом блока, другие входы ; коммутатора информационных сигналов являются соответственно третьим и четвертым информационными входами блока, выход коммутатора информацион1й1х сигналов подключен ко входу регистра числа, управляющие входы коммутатора информационных сигналов, регистра числа, регистра операнда и блока согласования соединены с другими выходами четвертого коммутатора адресных сигналов, управляющие входы третьего и четвертого коммутаторов, адресных сигналов являются соответственно четвертым и пятым управляющими входами блока, адресные входы - соответственно третьим и четвертым адресными входами блока. На фиг.1 приведена структурная .схема одноразрядного блока. логической памяти; на фиг,2 - структурная схема, логического запоминающего устройства, содержащая п одноразрядных блоков логической памяти (). Одноразрядньш блок логической памяти 1 (.смофиг.1 и фиг.2) содержит первый 2 второй 3 и третий 4 коммутаторы адресных сигналов, формирователь сигнала переноса 5, четвертый коммутатор адресных сигналов 6, накопитель 7, коммутатор информационных сигналов 8, регистр числа 9, регистр операнда 10, блок 11 согласования Информационный выход 12 накопителя 7 подключен к одному из входов 13 коммутатора 8, информационным входам 4 и 15 регистра 10 и блока 11 соэтветственно. Выход 12 накопителя 7 является первым информационным вькодом 16 блока 1. Выход коммутато ра 8 соединен с информационным входом 17 регистра 9, выход 18 кото рого соединен со входом 19 блока 11 информационным входом 20 накопителя 7, а также с информационным входом 21 коммутатора 3 и входом 22 формирователя 5, Выход 23 регистра . 10 соединен с информационным входом 24 коммутатора 2 и входом 25 формир вателя 5. Три младших адресных вход 26-28 накопителя 7 соединены с выходами соответствующих коммутаторов. 2-4, информационные входы 29-31 кот рых являются первым-третьим адресны ми входами блока 1 Старшие адресные входы 32 накопителя 7 соединены с одним из выходов коммутатора 6, другие выходы 33 кото рого соединены с управлякяцими входами 34,35, 36-и 37 коммутатора В, регистра 9, регистра 10 и блока 11, Первый информационный вход 38 бло ка 1 соединен с информаодонным входом коммутатора 4 и одним из входов формирователя 5, выход 39 которого является вторым информационным выходом блока 1, Формирователь 5 в каждом разряде. реализует распространение волны переносов при выполнении операций слож ний и вычитания. При этой на вход 38 поступает сигнал переноса П из предыдущего младшего разряда а с выхода 39 снимается сигнал перенос П в старший разряд. Межразрядное распространение волны переносов обеспечивается путем последовательного соединения соответствующих входов 38 и выходов 39 соседних разрядов. Логическая функция, реализуемая формирователем 5 выявления переноса имеет вид Y -у у АЗЦ 25 Здесь и дальше индексы переменных соответствуют номерам позиций на фиг,1 и 2, Управляющий вход 40 накопителя 7 является первым управляющим входом блока 1 и предназначен для управления записью и считыванием. Управляющие входы 41, 42 и 43 являются вторым , третьим и четвертым управляющими входами блока соответствен 26 но и предназначены для управления коммутацией сигналов поступакщих на адресные входы 26, 27, 28 накопителя 7 Через коммутаторы 2, 3, 4, Коммутаторы 2, 3 и 4 реализуют логические функции 26 2.4 Коммутатор 6 реализует переклю чение адресно-управляющей информации, поступающей с четвертого адресного Ёкода 44 блока 1 на выходы 32 и 33 коммутатора 6. Управляющий вход 45 коммутатора 6 является пятым управляю1цим входом блока 1. Коммутатор 6 выполняет следующие логические функции , о СЧ4Я5..-.Ягу,)/ .ЗбЛзтг (Г. Г„--(2:э24) десь Y. Y, - двоичные управляющие переменные; двоичные переменные на соответствующих адресных входах накопителя 7, Выход 46 блока 11 соединен с шиной 7 и входом 48 коммутатора 8. Второй 9 и третий 50 информационш 1е входы лока I обеспечивают связь данного ислового разряда с информационными ходами соседних, старшего i+ и ладшего разрядов. Каждый выход 46. блока 11 принимает дно из 3-х состояний 0,1Д..соотетствунщиХ передаче О, 1 и пасивному состоянию с большим выходным опротивлением. Структурный входной игнал Yj- содержит два двоичных игнала (Zj , Z ) которые правляют работой блока I1 в соотетс вии со следукшщми условиями ри де . -« переменные на соответ-г твующих входах блока 11, а переменая У-, характеризует состояние его ыхода. Устройство, составленное из п бл ков 1, содержит числовую магистраль 51 сполудуплексной передачей сигналов , адресную магистраль 52 и магистраль 53 управляющих сигналов, предназначенных для симплексной передачи сигналов (см.фиг.2 Адресные входы 29, 30, 31 и 44 каждо блока 1 подключены к адресной магист рали 52,шина 47 к числовой магистрали 51, а управляющие входы 40, 41, 42; 43 и 45 к магистрали 53 управляющих сигналов. Информационные выходы 16 каждого i -го блока 1 соединены с входом 49 младшего i-1 и входом 50 старшего i +1 соседних блоков,, обеспечивая реализацию сдвигов числовой информации. Выход 39 каждого предыдущего блока 1 соединен с входом 38 последующего, обеспечивая межразрядиое распространение волны переносов Вхо 38 первого и выход 39 п-го блоков. 1 являются информационными входом и выходом устройства соответственно. Выводы 50 и 16 младшего (1-го) и 49 и 16 старшего (И-го) блоков 1 . используются для организации циклических СДВИГОВо Устройство работает в различных режимах. .i. Прием слова из числовой магист рапи 51 в регистр 9. Слово из числовой магистрали 51 через выводы 47 и коммутатор 8под действием управляющих сигналов на входах 34 подается на вход 17 и з письтается в регистр 9. Необходимые управляющие сигналы на входы 34 и 35 поступают со входа 44 устройства и далее через коммутатор 6, необходимая настройка которого осуществляется управляющим снгнаиомсна входе 4 « .5.Э6.%-Г 33 .4.Э5 Э6%Т В рассматоиваемом режиме Л37-,24)00 2, Запись слова из регистра числа 9 в накопители 7. Адрес слова из адресной магистрали 52 подается на адресные входы 29, 30, 31 и 44 блоков 1 и при наличии сигналов соответствунщих входам коммутаторов 2,3, 4 и переключателя 6 к адресным входам 26, 27, 28 и 32 накопителей 7 Числовая информация подается на входы 20 накопителей 7 с выходов 18 регистра 9. Необходимые для обеспечения записи управляющие сигналы поступают, на вход 40 накопителей 7. Последовательное выполнение режи- :: мов I и 2 обеспечивает запись в накопители 7 устройства слова, поступающего через числовую магистраль 51 от других устройств ЭВМ. 3.Передача слова из регистра 9 в числовую магистрал-ь 51. Передаваемое слово из регистра 9 в числовую магистраль 51 с выходов 18 регистра 9 через блок 11 под действием управляющих сигналов на входе 37, поступающих на вход 44. В рассматриваемом режиме -(Уз4 Ь5 6 37 , p((Z,Zi),j5,36,CZ3,24)).,©,,), 4.Считывание слова из накопителей 7 в регистр 10. Адресные входы накопителей 7 устанавливается как в режиме 2. Необходимые для обеспечения считывания управляющие сигналы поступают на вход 40 накопителей 7. В момент воспроизведе|ния считанной информации на управляющий вход 45 подается сигнал 5145 При этом из адресной магистрали на управляющий вход 36 регистра 10 поступает сигнал у, осуществляющий запись считываемого слова в регистр 10. При этом fja-C i. (2з,4)),ои-(о,о) 5.Считывание слова из накопителей 7 во внешнюю магистраль 51. В этом режиме установление адресных входов, реализация считывания и переключение адресных входов 44 осуществляется аналогично режиму 4, Отличие состоит в значении структурного сигнала (),35.6.. CZ3,(---),o,o,(o) в ммомент воспроизведения считанной информации. При этом ,46Л о. Считывание слова в регистр 9 без сдвига, со сдвигом вправо или влево на один разряд. Установление адресных входов, ре лизация считывания из накопителей 7 и переключение адресных входов 44 выполняется как и в режимах 4 и В момент воспроизведения информа ции структурный сигналi33 управлени имеет следующие значения Чз((2:,г2),зГ зб. CZз,I.4)) Uz,Z2)Лo(opl| При считывании без сдвига .-0/ -П -Xl-b при считывании со сдвигом влево сторону старших разрядов Z Z4- 0; i 7-Х49 при считывании со сдвигом вправо /в сторону младших разрядов/ , Во всех случаях сигнал обеспечивает запись в регистр 9, 7. Выполнение логической операции. Выполнение логической операции реализуется табличным способом. Дл этого программным путем в накопит лях 7 вьщеляется необходимое число сегментов по 4 ячейки в каждом и пр изводится настройка каждого сегыект на выполиение любой двyx 4ecтиpй ло гической операции одновременно во всех разрядах накопителей путем записи в них соответйтвуюпщх таблиц (результатов) логических функци Местоположение таблиц в накопителях 7 определяется cигнaлa ш на их адре .ных входах 28 и 32 о Предварительно операнды, над которыми необходимо выполнить логичес1 ую операцию, передаются в регистр 10 и регистр 9, Для чего последовательно реализуются режимы 4 и 5 (в режиме 6 производится счит вание слова без сдвига). Далее адрес таблицы необходимой логической функции из адресной маги рали 52 через входы 31 и 44 под дей вием управлягадих сигналов у Уд| О иа соответсвующих входах 43 45 блоков 1, поступают на адресные входы 28 и 32 накопителей 7, опред ляя местоположение сегмента памяти хранящего таблицу. Установка двух младших адресных входов 26 и 27 на 2 копителей 7, определяющих адрес ячейки внутри выбранного сегмента, который в общем случае для каждого накопителя 7 является различным, произво дится путем подключения выходов 23 и 18 каждого разряда регистров, хранящихся операции, через входы 24 и 21 коммутаторов 2 и 3 соответствен- . но, к адресным входам 26 и 27 накопителей 7 под действием управляющих сигналов Улл- 1 Удч входах 41 и 42 коммутаторов. Выбранные эле-, менты накопителей 7 содержат результаты поразрядного выполнения COOTветствукицей логической функции, который считывается в регистр 9 без сдвиг га, аналогично тому, как это описано для режима 6, . 8. Выполнение арифметических операций. При выполнении арифметических операций сигнал переноса в старший разряд вычисляется по формуле n.()ni-v где а; , в г 1-ые разряды операндов. Сигнал Xjjjформируется формирователем 5 (см, описание логической функции J« Сумма S начисляется по формуле ., . согласно которой операция сложения выполняется как логическая операция суммирования по модулю два трех аргументов. Для ее реализации в накопителях выделен сегмент памяти из В ячеек, хранящий соответствующую таблицу, адресация которого производиться по входам 32. В предлагаемом устройстве в срав ении с известным отсутствует один регистр операнда и проще регистр 4исла. Для обеспечения операций сдвигов в известном устройстве регистр числа должен быть реверсивным сдвигаюищм регистром, в том время Как в предлагаемом - это простой статистический регистр, аналогичный регистру операндов. Дополнительная экономия аппаратурных затрат в опнсаниом устройстве может быть получена за счет возможности размещения микропрограммы в накопителях устройства. Кроме того за счет уменьшения числа обращений к накопителям время выполнения операции суммирования уменьшается по сравнению с известным, примерно в 3 раза.

II

Формула изобретения

одноразрядный блок логической памяти, содержащий накопитель,коммутаторы адресных сигналов, регистр числа и регистр операнда, причем одни из входов первого и второго коммутаторов адресных сигналов подключены соответственно к выходам регистра числа и регистра операнда, а выходы - к одним из адресных входов накопителя, информационный вход которого соединен с выходом регистра числа, а информационный выход соединен со входом регистра операнда и является первым информационным выходом блока, управляющие входы накопителя первого и второго коммутаторов адресных сигналов являются соответственно первым, вторым и третьим управляющими входами блока, другие входы первого и второго коммутаторов адресных сигналов - первым и вторым адресными входами блока, о т ли чающийс я тем, что с целью упрощения и повьшения надежности блока, он содержит третий и четвертый коммутаторы адресных сигналов, формирователь сигнала переноса, коммутатор информационных сигналов и блок согласования, причем первый вход формирователя сигнала переноса соединен с информационным входом третьего коммутатора адресных сигналов и является первым информаци онным входом блока, второй и третий соединены соответственно с выkoдaми регистра числа и регистра операнда, и.выход является вторым ин- формационным выходом блока, выход

826422

12

Третьего и одни из выходов четвертого коммутаторов адресных сигналов под1шючены соответственно к другим адресным входам накопителя, выход регистра числа соединен с одним из входов блока согласования, другой вход которого подключен к информационному выходу накопителя и первому входу коммутатора информационных сигналов, а выход соединен со вторым входом коммутатора информационных сигналов и с шиной, являющейся вторым информационным входом и третьим информационным выходом блока, другие входы коммутатора информационных сигналов являются соответственно третьим и четвертым информацион1П)1ми входами блока, выход коммзтатора информационных сигналов подключен ко входу регистра числа, управляющие входы коммутатора информационных сигналов, регистра числа, регистра операнда и блока согласования соединены с другими выходами четвертого коммутатора адресных сигналов, управляющие входы третьего и четвертого коммутаторов адресных сигналов являются соответственно четвертым и пятым управляющими входами блока, адресные входы - соответственно третьим и четвертым адресными входами блока.

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР № 494768, кл. СП С 17/00, 1974.

2.Авторское свидетельство СССР по заявке № 2503720/18-24,

кл. G 06 F 15/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Система для выполнения команд десятичной арифметики табличным способом | 1981 |

|

SU1027731A1 |

| Логическое запоминающее устройство | 1977 |

|

SU691926A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

Авторы

Даты

1981-04-30—Публикация

1979-07-18—Подача