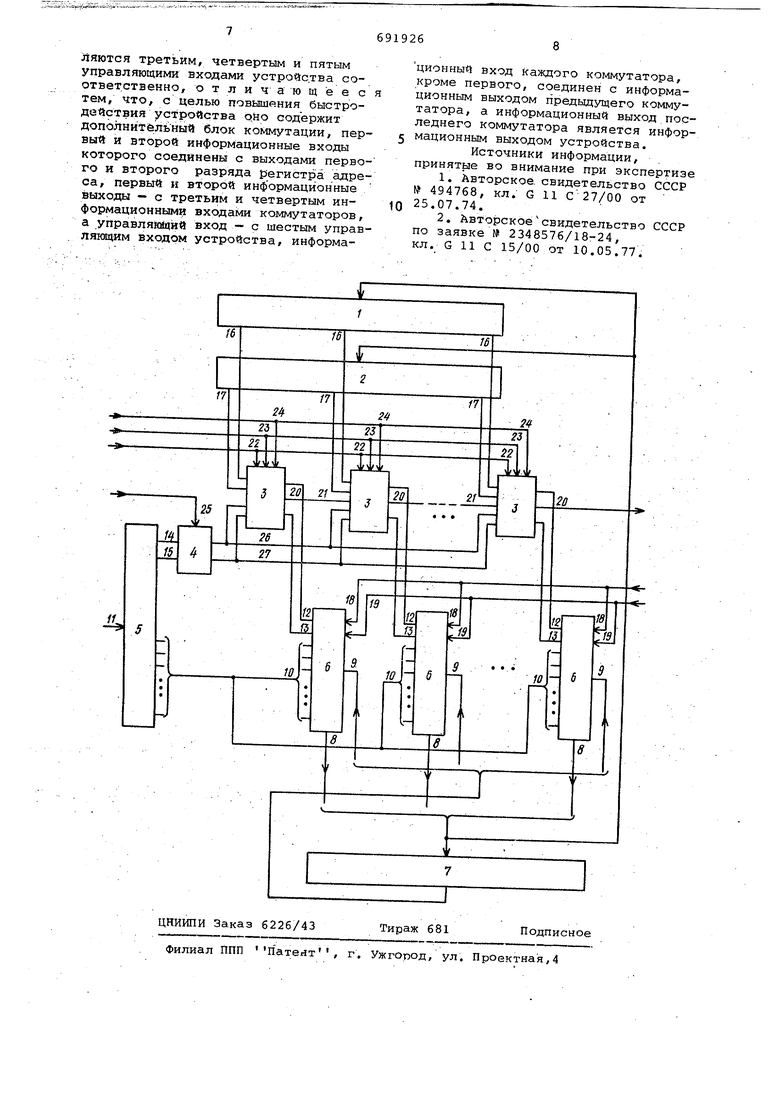

(54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО с выходами первого и второго разряда регистра адреса, первый и второй, информационные выходы - с третьим и четвертым информационными входами KONiMyTaxopoB, а управляющий вход - с шестым управляющим входом устройства, информационный вход каждого коммутатора,кроме первого, соединен с информационным выходом предыдущего коммутатора, а информационный выход последнего коммутатора является информационн м выходом устройства. - Блок-схема предложенного устройства представлена на чертеже. Лрги.ческое запоминающее устройство содержит регистр 1 первого операнда, регистр 2 второго операнда, крммутаторы 3,: блок 4 коммутации; регистр 5 адреса, элементы 6 памяти с разрйдной д рганизацией и встроенными дёшифраторами адреса, и регистр 1 числа. Выходы 8 элементов 6. памяти подключены к информацион ным входам соо тветствующих разрядов регистра 7 числа, а также регистров 1 первого и 2 второго-операндов.Информационны входы 9 элементов б памяти соединены С выходами соответствующих разрядов регистра 7 числа, а адресные входы : 10, за исключением первыхдвух,-с соотвётствуюЩими выходами регистра 5 адреса. Через вход 11 .заполняется регистр 5 адреса. Первые два адресные входа 12 и 13 элементов б памяти связаны через коммутаторы 3 с выходами первых двух разрядов 14 и 15 регистра 5 адреса и с выходами 16 и. -. 7 регистров 1 первого и 2 второго операндрв таким образом, что первый адресный вход 12 i-ro элемента 6 памяти соединен через 1-й коммутатор как С вШ:одом пёрвого разряда 14 ре. гистра 5 адреса (через блок-.4 коммутации), таки свыходом 16 i-ro разряда регистра 1 первого операнда И аналогично второй адресный вход 1 i-ro элемента 6 памяти соёДйнён чер коммутатор 3 как с выходом второго разряда 15 регистра 5 адреса. - (через блок 4 коммутации), так и с выходом 17 i-ro разряда регистра 2 -второго операнда. - . Первый и второй управляющий, входы устройства соединены с первым 18 и в ... -рым 19 управляющими входами элемент -.. 6 памяти, на которые поступают сигн лы запись и считывание . Каждый коммутатор 3 имеет выход 20, соединенный, с входом 21 аналоги ного коммутатора .в соседнем старшем разряде. Выход 20 коммутатора старшего разряда является информационны выходом устройства. Коммутаторы 3 реализуют коммутацию адресных сигна лов первых двух адресных входов эле Ментов 6 Пс1мяти и волну перенос Первый 22, второй 23 и третий 24 управляющий входы коммутаторов 3 яв яются третьим, четвертым и пятым правляющими входами устройства. лок 4 коммутации коммутирует адресые сигналы с выхода первого разряда 4 и второгоразряда 15 регистра 5 дреса с помощью сигнала на управляюем входе 25, Который является шестым правляющим входом устройства. Выходы 6 и 27 блока 4 коммутации соединены третьим и, четвёртым информационным ходами коммутаторов 3 соответственно. лок 4 коммутации, и коммутаторы 3 выолняют следующие логические функции: .. .- . . . .(, - N V Y .20 16 2- где индексы переменных соответствуют Номерам позиций на чертеже. ., . Предяаг.аемое устройство работает разных режимах. ; . :. 1.Считывание слова из элементов Памятй в; регистре 7 числа в регист- 1 ИЛИ в регистр 2. Адрес слова по-:.: дается на регистр 5 а:дрёса и, при . наличии управляющего сигнала на0ходе. 25, выходЕа; первых двух разрядрё . регистра адреса подключаются через блок коммутации и коммутаторы к первым двум адресным входам элементов памяти, а остальные выходы регистра адреса йепосредственно связаны с адресными входами 10 элементов памяти. Затем йрЬизводитс51 считывание, и выбранное слово поступает на регистр числа, регистр 1 иди регистр 2. . 2.Запись .слова, в элементы памяти из регистра -«хисла. Адресные входы элементов памяти Устанавливаются как в режиме считывания. Запис.ййаемое слово находится в регистре числа, и в режиме записи заноситсй в выбранную адресом ячейку. ;. . ... 3.Выполнение логической операции. Для этого программным путем в элементах памяти вьаделено любое число сег-. ментов по 4 ячейки в каждом и произведена настройка каждого из выделенных йегМ(ентов на .выполнение любой двухместной логической операции одновременно во всех разрядах, то есть в каждом выделенном сегменте находится таблиЦё (результаты) данной логической функции, местоположение .которрй в элементах памяти определяется адресными сигналами на входах 10 элементов памяти. Следует отметить, что считывание производится без разрушения информации. На.регистры 1 и 2 подаются операнда, над которыми необходимо выполнить логическуй операцию. Выходы 16 и 17 регистров 1 и 2 подключаются через коммутаторы 3 под действием управляющих сигналов на входах 22 и 23 к соответствующим первым двум сщресным входам 12 и 13 элементов памяти. Затем производится считывание и содержимое ячеек табли поступает на регистр числа. 4. Выполнение логической операци с использованием схе.мы сквозного пе носа. Схемой сквозного переноса явл ется- составная часть коммутаторов 3 Она используется при выполнений ари метических операций сложения и вычи тания. Слово переноса i-ro разряда П- вычисляется по формуле («г®Ч Ч1 Ч1 Р21П1и где F ot-it){; Fj bi и реализуется схемным способом (см. на фун цию У go коммутаторов). При этом и регистре 1 должна находиться функци F ив регистре 2 F,. При выполне НИИ операций сложений сумма S вычис ляется однократным суммированием tto модулю 2 по формуле ; . S;t«i®4 ®n,:T2 ®niH: : V ПоскЬльку содержимое регистра 2 при распространении волцы переноса совпадает с одним слагаемь;м (Fg) сум мы S, логическая операция сложения по модулю 2 производится сразу-же после ее распростра нений. Операция сложения двух чисел производится сле дующим оЬраэом. ПредварйтеЛьнс skчислЯй ся при /режиме № 3 функции F и Fj, и размещаются их результаты в регистрах 1 и 2 соответственно. на регистр адреса поступает код фуйк ции сложение по модулю 2, и с .; использованием этого адреса таблицы (без использования первых Двух разрядов) и управляйщих сигналов на входах 24 и 23, подклйчающих к перврму адресному входу i-ro элемент памяти перенос предыдущего разряда П , и ко второму Адресному входу i-гб элемента памяти вь1ход i-ro разряда регистра 2 сЪответственйо, производится считывание , и сумма S поступает на регистр числа. ФункциойНальная микропрограмма сложения имее следующий ВИД: НАЧАЛО. ; ,P2, /PI СО 1 ,P2t4V,Il И); , ,P2/.-o ,П cV-i ; Р4; , КОЙЁЦ где РЧ - регистр числа; Р1 и Р2 -регистр 1 первого и 2 второго операндов j . ...l - содержимое ячейки Н по адресным сигналам 1...пг -адресный код функции F и Fg; ,s,0 -адрес ячеек операндов .1 и 2, суммы и промежу. точного результата со.ответственно. Выше описанная схемная реализация переноса и микропрограмма используется также для вычисления заема и раз|НосТй; при выполнении операции вычитания. . Слово заема i-ro разряда 3 вычис:ляется по формуле i--«i4(ai©V4H где и F )Разность двух чисел определяется формулой Р ( -ь. P4i® i-H Структура формул как .переноса П и заема , так и,суммы S и разности Р одинакова. Выполнение сложения отличается ст.- выполнения вычитания только тем, что при выполнении сложения используются функции F и Fg, а при вычитании функции F и F, что скажется только на мйкропрограмме при адресации таблиц поВходам 10, а не отражается в аппаратурной организации устройства. В данном устройстве, при необходимости выполнения различных двухместных операций, должно быть выделено в элементах памяти сегментов по 4 ячейки в каждом. Оставшаяся (основная) часть элементов памяти используется для хранения информации. В сравнении с известными устройствами данное устройство выполняет арифметическиеОперации сложения и вычитания более чём в 6 раз быстрее при незначительном/Увеличении стоимости устройства. ... Формула изобретения . Логическое запоминающё-е устройство, содержащее элемёнты памяти, выходы которых соединены с соответствующими нфо рмаци6ннымй входами регистра исла, регистров первого ивторого перандов, выход каждого разряда реистра числа Соединен с информационым входом соответствующего элемента амяти, первый и ;второй управляющий ходы которого являются первым и торым управляющими входами устройтва, выходы разрядов регистра адреа соединены с соответствующими адесными входами элементов памяти, ервый й второй адресные входы котоых соедйненн с первым и вторьм выодами коммутаторов, первый и второй нформационные входы которых соедиены с выходами соответствующих разядов регистров первого и второго перандов, первый, второй и третий правляющий входы коммутаторов явйяются третьим, четвертым и пятым управляющими входами устройства соответ.ственно, отличающеес тем, что, с целью повышяния быстродействия устройства рйо содержит дополнитёльный блок коммутации, первый и второй информационные входы которого соединены с выходами первого и второго разряда регист1эа адреса, первый и второй информационные выходы - с третьим и четвертым информационными входами коммутаторов, а управлякйдий вход - с шестым управляющим входом устройства, информационный вход каждого коммутатора, кроме первого, соединен с информационным выходом предыдущего коммутатора, а информационный выход последнего коммутатора является информационным выходом устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское, свидетельство СССР № 494768, кл. G 11 С27/00 от 25.07.74.

2.Авторскоесвидетельство СССР по заявке 2348576/18-24,

кл. G 11 С 15/00 от 10.05.77.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки нечеткой информации | 1989 |

|

SU1674145A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| ОДНОРАЗРЯДНЫЙ БЛОК ЛогаЧЕСКОЙ ПАМЯТИ | 1979 |

|

SU826422A1 |

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Система для выполнения команд десятичной арифметики табличным способом | 1981 |

|

SU1027731A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

Авторы

Даты

1979-10-15—Публикация

1977-06-28—Подача