блока выборки адресных микрокоманд, управляющим входом блока приема и входом элемента задержки, выход которого соединен с первыми входами элементов И (N-i-M-l)-oA группы, выходы которых соединены с четвертый входом блока выборки адресных микрокоманд, пятый выход которого соединен с синхронизирующим входом блока выборки операционных микрокоманд, шестой выход блока выборки адресных кшкрокоманд соединен с вторыми входами элементов И первой группы, входом установки в ноль второго буферного регистра и синхронизрующим входом блока приема, выходы элементов ИЛИ группы соединены с информационным входом блока приема, первый выход которого соединен с вторым входом блока сравнения и вторыми входами элементов И (N+M-1)-й группы, входы элементов И ()-й группы являются вторым информационным входом устройства, второй выход блока приема соединен с вторыми входами элементов И (N+M)-и группы, выходы которых соединены с пятым входом блока выборки адресных микрокоманд, шестой и седьмой входы которого являются соответственно трет им и четвертым информационными входами устройства, информационный выход регистра передачи управления соединен с первыми входами элементов И второй группы, информационный выход регистра передачи управления соединен с третьими входами элементов И второй и )-й групп, выходы дешифратора соединены с вторыми входами элементов И второй группы, выходы которых являются вторыми информационными выходами устройства.

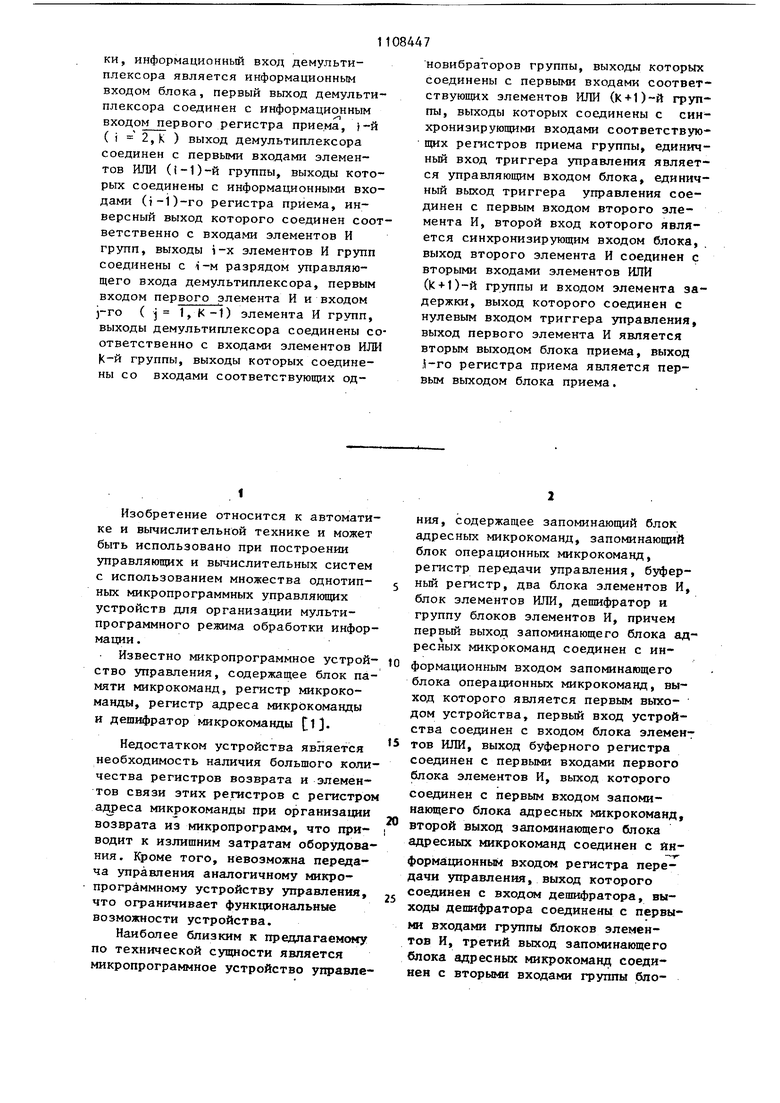

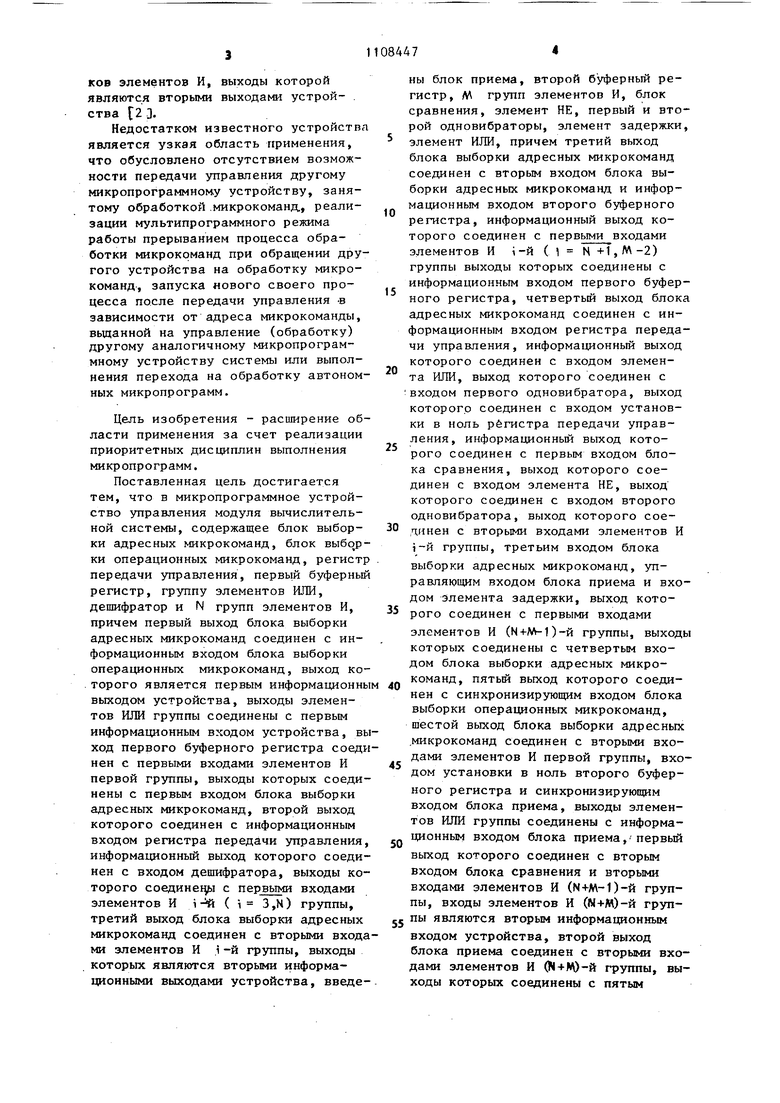

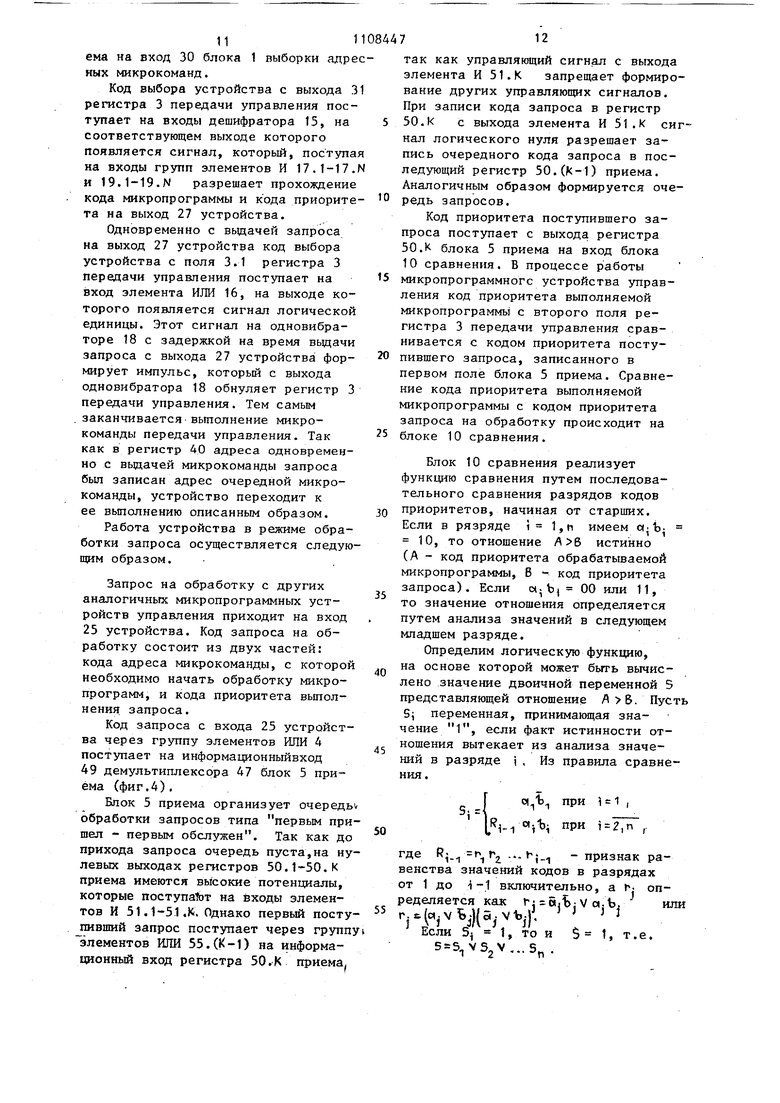

2. Устройство по п.1, о т л ичающееся тем, что блок выборки адресных микрокоманд содержит группу элементов ИЛИ, группу сумматоров по модулю два, регистр адреса, дешифратор адреса, узел памяти адресных микрокоманд, элемент задержки, причем выходы элементов ИЛИ группы соединены с информахщонньм входом регистра и первыми входами сумматоров по модулю два группы, выходы которых соединены с информационным входом регистра адреса, информационный выход которого соединен с входом дешифратора адреса, выход которого соединен с ад0R447

ресным входом узла памяти адресных икpoкoмaнд, выход адреса операционных микрокоманд которого является первым выходом блока выборки адресных микрокоманд, первые входы элементов ИЛИ группы являются первым входом блока, выход адреса передачи управления узла памяти адресных микрокоманд является вторым выходом блока выборки адресных микрокоманд, вторые входы элементов ИЛИ группы являются вторым входом блока, выход адреса очередной микрокоманды узла памяти адресных

микрокоманд является третьим выходом блока, вход установки в ноль регистра адреса является третьим входом блока, выход кода приоритета узла памяти адресных микрокоманд является четвертым выходом блока, третьи и четвертые входы элементов ИЛИ группы являются соответственно четвертым и пятым входами блока, вторые входы сумматоров по модулю два группы являются шестым входом блока, синхронизирующий вход дешифратора адреса и вход элемента задержки объединены и.являются седьмым входом блока, выход элемента задержки является пятым выходом блока, выход окончания вьтолнения микропрограммы узла памяти адресных микрокоманд является шестым выходом блока.

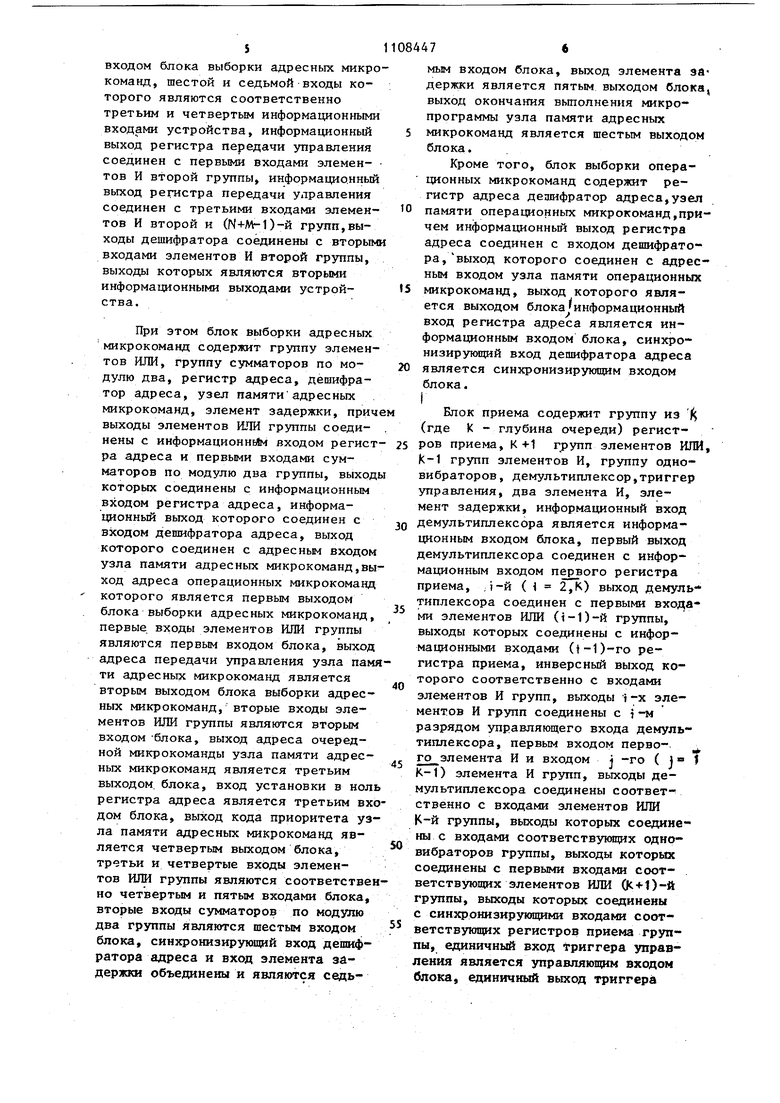

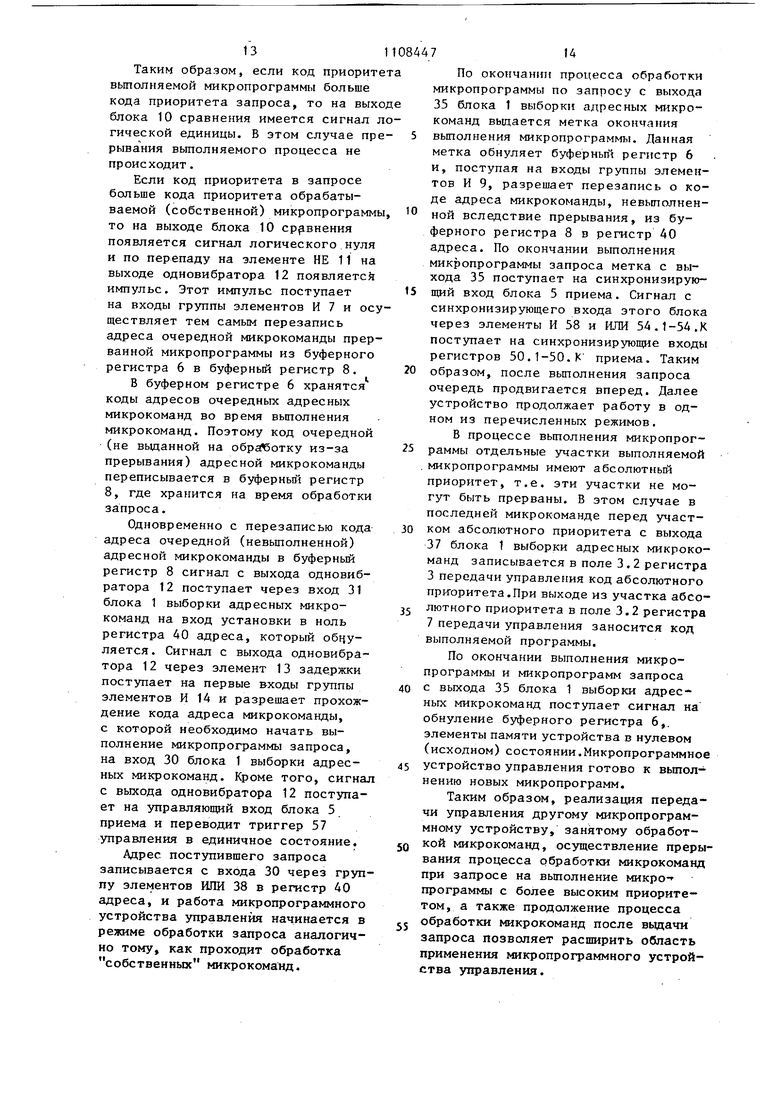

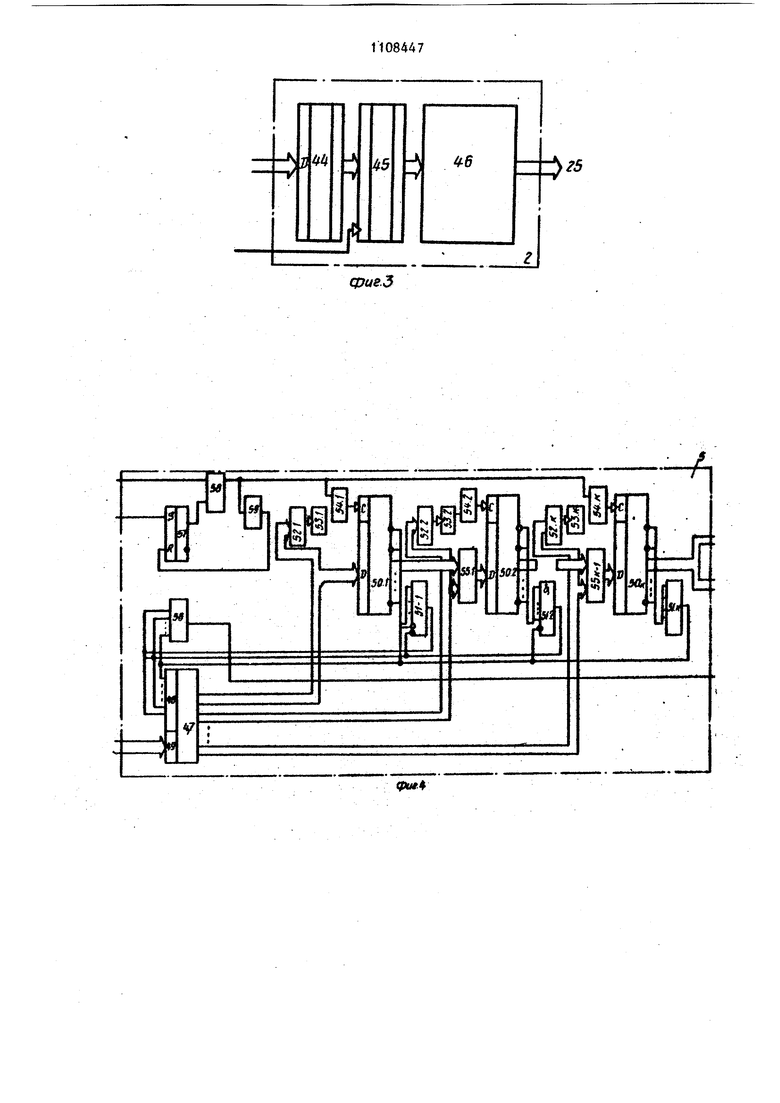

3.Устройство по П.1, о т л ичающееся тем, что блок выборки операционных микрокоманд содержит регистр адреса, дешифратор адреса, узел памяти операционных микрокоманд, причем информационный выход регистра адреса соединен с входом дешифратора адреса, выход которого соединен с адресным входом узла памяти операционных мт крокоманд, выход которого является .выходом блока, информационный вход регистра адреса является информационным входом блока, синхронизирующий вход дешифратора адреса является синхронизирующим входом блока.

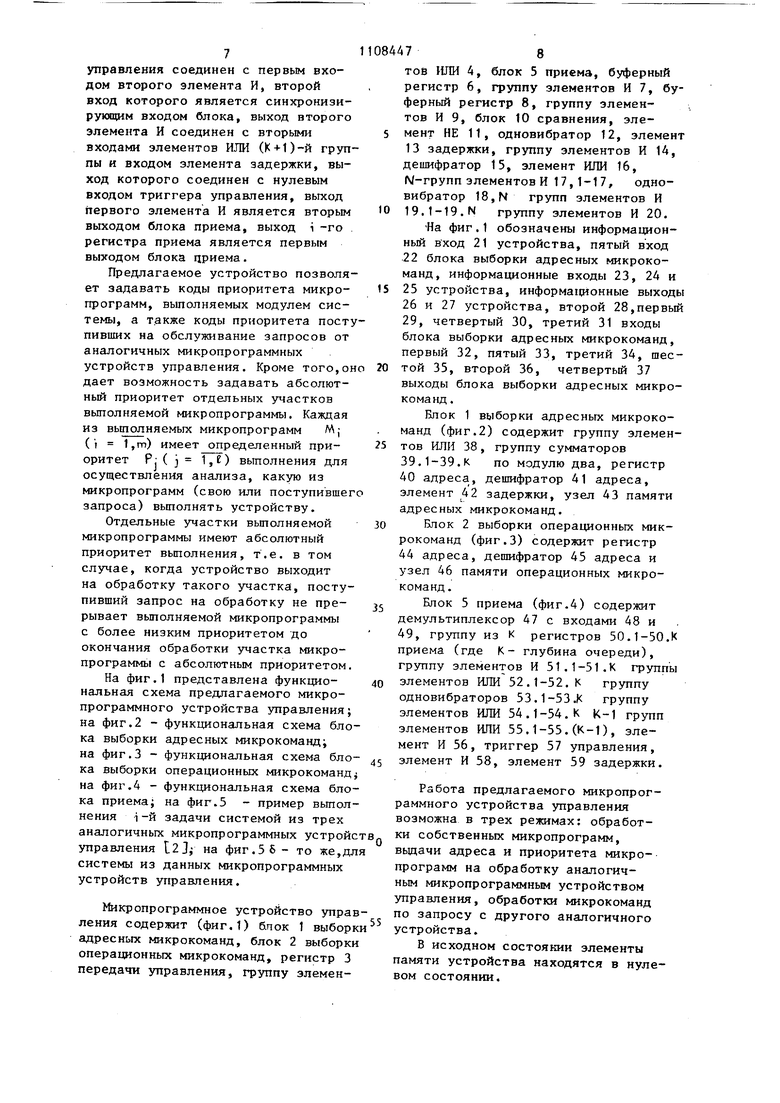

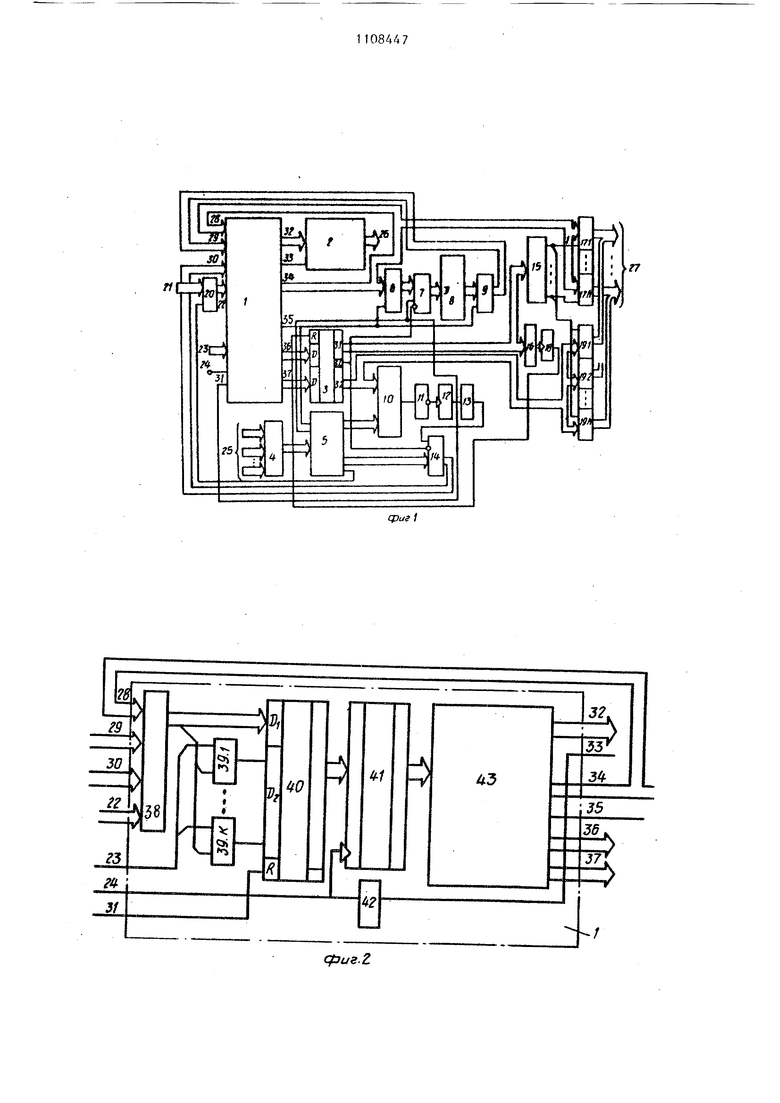

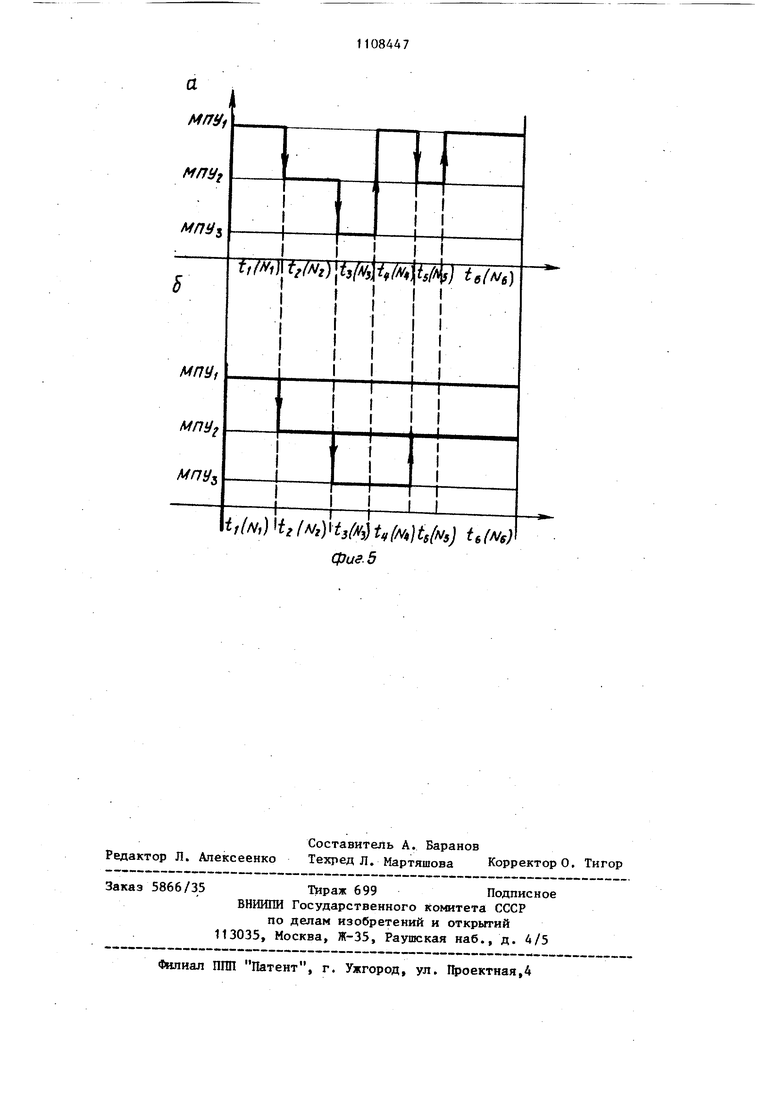

4.Устройство по п.1, о т л ичающееся тем, что блок приема содержит группу из К (где К глубина очереди) регистров приема, К+1 групп элементов ИЛИ, К-1 групп элементов И, группу одновибраторов, демультиплексор, триггер управления, два элемента И, элемент задержки, информационный вход демультиплексора является информационным входом блока, первый выход демультиплексора соединен с информационным входом первого регистра приема, ;-й ( i 2,К ) выход демультиплексора соединен с первыми входами элементов ИЛИ (-1)-й группы, выходы которых соединены с информационными входами (i-l)-ro регистра приема, инверсный выход которого соединен соответственно с входами элементов И групп, выходы i-x элементов И групп соединены с i-м разрядом управляющего входа демультиплексора, первым входом первого элемента И и входом j-го ( j 1,К-1) элемента И групп, выходы демультиплексора соединены соответственно с входами элементов ИЛИ К-й группы, выходы которых соединены со входами соответствующих одновибраторов группы, выходы которых соединены с первыми входами соответствуюиих элементов ИЛИ (К + О-й группы, выходы которых соединены с синхронизирующими входами соответствующих регистров приема группы, единичный вход триггера управления является управляющим входом блока, единичный выход триггера управления соединен с первым входом второго элемента И, второй вход которого является синхронизирующим входом блока, выход второго элемента И соединен с вторыми входами элементов ШТИ ()-й группы и входом элемента задержки, выход которого соединен с нулевым входом триггера управления, выход первого элемента И является вторым выходом блока приема, выход ;5-го регистра приема является первым выходом блока приема.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный модуль | 1984 |

|

SU1193675A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043653A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1092505A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Мультимикропрограммная управляющая система | 1989 |

|

SU1631542A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

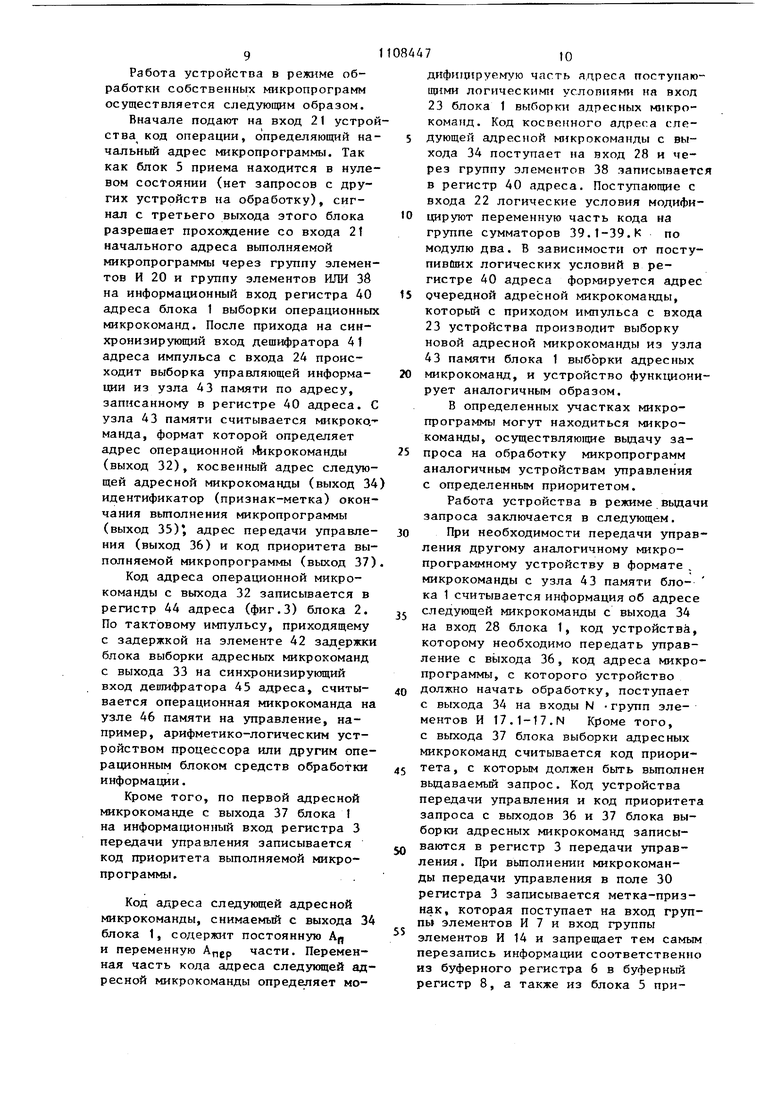

1. МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ МОДУЛЯ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, содержащее блок выборки адресных микрокоманд, блок выборки операционных микрокоманд, регистр передачи управления, первый буферный регистр, группу элементов ИЛИ, дешифратор и N групп элементов И, причем первый выход блока выборки адресных микрокоманд соединен с информационным входом блока выборки операщюнных микрокоманд, выход которого является первым информационным выходом устройства, входы элементов ИЛИ группы соединены с первым информационным входом устройства, выход первого буферного регистра соединен с первыми входами элементов И первой группы, выходы которых соединены с первым входом блока выборки, адресных микрокоманд, второй выхид которого соединен с информацион тым входом регистра передачи управления, информационный выход которого соединен с входом дешифратора, выходы которого соединены с первыми входа « элементов И i-й (i 3,W) группы, третий выход блока выборки адресных микрокоманд соединен с вторыми входами элементов И i -и группы, выходы которых являются вторыми информационными выходами устройства, отличающееся тем, что, с целью расширения области применения за счет реализации приоритетных дисциплин выполнения микропрограмм, в него введены блок приема, второй буферный регистр, М групп элементов И, блок сравнения, элемент НЕ, первый и второй одновибраторы, элемент эадержки, элемент ИЛИ, причем третий выход блока выборки адресных микрокоманд соединен с вторым входом блока выш с борки адресных микрокоманд и информационным входом второго буферного регистра, информационный выход которогю соединен с первыми входами элементов И i-и ( i N+1,W-2) группы, выходы которых соединены с информационным входом первого буферо ного регистра, четвертый выход бло2 ка выборки адресных микрокоманд соединен с информационным входом гистра передачи управления, информаЧ ционный выход которого соединен с входом элемента ИЛИ, выход которого соединен с входом первого одновибратора, выход которого соединен с входом установки в ноль регистра передачи з равпения, информационный выход которого соединен с первым входом блока сравнения, выход которого соединен с входом элемента НЕ, выход которого соединен с входом второго одновибратора, выход которого соединен с вторыми входами элементов И -и группы, третьим входом

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении управляющих и вычислительных систем с использованием множества однотипных микропрограммных управляющих устройств для организации мультипрограммного режима обработки информации.

Известно микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр микрокоманды, регистр адреса микрокоманды и дешифратор микрокоманды ij.

Недостатком устройства является необходимость наличия большого количества регистров возврата и элементов связи этих регистров с регистром

адреса микрокоманды при организации возврата из микропрограмм, что приводит к излишним затратам оборудования. Кроме того, невозможна передача управления аналогичному микропрограммному устройству управления, что ограничивает функциональные возможности устройства.

Наиболее близким к преялагаем(1у по технической сущности является микропрограммное устройство управления, содержащее запоминающий блок адресных микрокоманд, запоминающий блок операционных микрокоманд, peniCTp передачи управления, буферный регистр, два блока элементов И блок элементов ИЛИ, дешифратор и группу блоков элементов И, причем первый выход запоминающего блока адресных микрокоманд соединен с информационным входом запоминающего блока операционных микрокоманд, выход которого является первым выходом устройства, первый вход устройства соединен с входом блока элемен тов ИЛИ, выход буферного регистра соединен с первыми входами первого блока элементов И, выход которого соединен с первым входом запоминающего блока адресных микрокоманд, второй выход запоминающего блока адресных микрокоманд соединен с информационным входом регистра передачи управления, выход которого соединен с входом дешифратора, выходы дешифратора соединены с первыми входами группы блоков элементов И, третий выход запоминающего блока адресных микрокоманд соединен с вторыми входами группы блоков элементов И, выходы которой являются вторыми выходами устройства f 2 . Недостатком известного устройств является узкая область применения, что обусловлено отсутствием возможности передачи управления другому микропрограммному устройству, занятому обработкой .микрокоманд, реализации мультипрограммного режима работы прерыванием процесса обработки микрокоманд при обращении дру гого устройства на обработку микрокоманд, запуска нового своего процесса после передачи управления -в зависимости от адреса микрокоманды, вьщанной на управление (обработку) другому аналогичному микропрограммному устройству системы или выполнения перехода на обработку автоном ных микропрограмм. Цель изобретения - расширение об ласти применения за счет реализации приоритетных дисциплин выполнения микропрограмм. Поставленная цель достигается тем, что в микропрограммное устройство управления модуля вычислительной системы, содержащее блок выборки адресных микрокоманд, блок выбор ки операционных микрокоманд, регист передачи управления, первый буферны регистр, группу элементов ИЛИ, дешифратор и N групп элементов И, причем первый выход блока выборки адресных микрокоманд соединен с информационным входом блока выборки операционных микрокоманд, выход ко .торого является первым информационн выходом устройства, выходы элементов ИЛИ группы соединены с первым информационным входом устройства, в ход первого буферного регистра соед нен с первыми входами элементов И первой группы, выходы которых соеди нены с первым входом блока выборки адресных микрокоманд, второй выход которого соединен с информационным входом регистра передачи управления информационный выход которого соеди нен с входом дешифратора, выходы ко торого соединець с первыми входами элементов И i - ( i 3,N) группы, третий выход блока выборки адресных микрокоманд соединен с вторыми вход ми элементов И i-и группы, выходы которых являются вторыми информационными выходами устройства, введе ны блок приема, второй буферный регистр, М групп элементов И, блок сравнения, элемент НЕ, первый и второй одновибраторы, элемент задержки, элемент ИЛИ, причем третий выход блока выборки адресных микрокоманд соединен с вторым входом блока выборки адресных микрокоманд и информационным входом второго буферного регистра, информационный выход которого соединен с первыми входами элементов И i-и ( 1 N +1,М-2) группы выходы которых соединены с информационным входом первого буферного регистра, четвертьй выход блока адресных микрокоманд соединен с информационным входом регистра передачи управления, информационный выход которого соединен с входом элемента ИЛИ, выход которого соединен с входом первого одновибратора, выход которого соединен с входом установки в ноль регистра передачи управления, информационный выход которого соединен с первым входом блока сравнения, выход которого соединен с входом элемента НЕ, выход которого соединен с входом второго одновибратора, выход которого соединен с вторыми входами элементов И i-й группы, третьим входом блока выборки адресных микрокоманд, управляющим входом блока приема и входом элемента задержки, выход которого соединен с первыми входами элементов И ()-й группы, выходы которых соединены с четвертым входом блока выборки адресных микрокоманд, пятый выход которого соединен с синхронизирующим входом блока выборки операционных микрокоманд, шестой выход блока выборки адресных .микрокоманд соединен с вторыми входами элементов И первой группы, входом установки в ноль второго буферного регистра и синхронизирующим входом блока приема, выходы элементов ИЛИ группы соединены с информационным входом блока приема,первый выход которого соединен с вторым входом блока сравнения и вторыми входами элементов И (Ы+М-1)-й группы, входы элементов И (Ы+М)-й группы являются вторым информационным входом устройства, второй выход блока приема соединен с вторыми входами элементов И (N+M)-u группы, выходы которых соединены с пятым входом блока выборки адресных микро команд, шестой и седьмой входы которого являются соответственно третьим и четвертьм информационными входами устройства, информационный выход регистра передачи управления соединен с первыми входами элементов И второй группы, информационный выход регистра передачи управления соединен с третьими входами элементов И второй и (N+M-1)-й групп,выходы дешифратора соединены с вторым входами элементов И второй группы, выходы которых являются вторыми информационными выходами устройства. При этом блок выборки адресных микрокоманд содержит группу элементов ИЛИ, группу cjfMMaTopoB по модулю два, регистр адреса, дешифратор адреса, узел памяти адресных микрокоманд, элемент задержки, прич выходы элементов ИЛИ группы соедииены с информационна входом регист ра адреса и первыми входами сумматоров по модулю два группы, выход которых соединены с информационным входом регистра адреса, информационный выход которого соединен с входом дешифратора адреса, выход которого соединен с адресньм входом узла памяти адресных микрокоманд,вы ход адреса операционных микрокоманд которого является первым выходом блока выборки адресных микрокоманд, первые, входы элементов ИЛИ группы являются первым входом блока, выход адреса передачи управления узла пам ти адресных микрокоманд является вторым выходом блока выборки адресных микрокоманд, вторые входы элементов ИЛИ группы являются вторым входом блока, выход адреса очередной микрокоманды узла памяти адресных микрокоманд является третьим выходом, блока, вход установки в нол регистра адреса является третьим вх дом блока, выход кода приоритета уз ла памяти адресных микрокоманд является четвертьм выходом блока, тр-этьи и четвертые входы элементов ИЛИ группы являются соответстве но четвертым и пятым входами блока, вторые входы сумматоров по модулю два группы я:вляются шестым входом блока, синхронизирующий вход дешифратора адреса и вход элемента задержки об1 единены и являются седь476мым входом блока, выход элемента задержки является пятым выходом блока, выход окончания выполнения микропрограммы узла памяти адресных микрокоманд является шестым выходом блока. Кроме того, блок выборки операционных микрокоманд содержит регистр адреса дешифратор адреса,узел памяти операционных микрокоманд,причем информационньй выход регистра адреса соединен с входом дешифратора, выход которого соединен с адресным входом узла памяти операционных микрокоманд, выход которого является выходом блокаинформационный вход регистра адреса является информационным входом блока, синхронизирующий вход дешифратора адреса является синхронизирующим входом блока. Блок приема содержит группу из | (где К - глубина очереди) регистров приема, К+1 групп элементов ИЛИ, k-1 групп элементов И, группу одновибраторов, демультиплексор,триггер управления, два элемента И, элемент задержки, информационный вход демультиплексора является информационным входом блока, первый выход демультиплексора соединен с информационным входом первого регистра приема, ;)-й ( i 2,К) выход демуль- типлексора соединен с первыми входами элементов ИЛИ (1-1)-й группы, выходы которых соединены с информационными входами (t-l)-ro регистра приема, инверсный выход которого соответственно с входами элементов И групп, выходы i-х элементов И групп соединены с j-м разрядом управляющего входа демультиплексора, первым входом первого элемента И и входом j -го ( j I К-1) элемента И групп, выходы демультиплексора соединены соответственно с входами элементов ИЛИ К-й группы, выходы КОТОР1ЛХ соединены с входами соответствующих одновибраторов группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ (К + 1)-й группы, выходы которых соединены с синхронизирующими входами соответствующих регистров приема группы, единичный вход триггера управления является управляющим входом блока, единичный выход триггера управления соединен с первым входом второго элемента И, второй вход которого является синхронизирующим входом блока, выход второго элемента И соединен с вторыми входами элементов ИЛИ (К + О-й группы и входом элемента задержки, выход которого соединен с нулевым входом триггера управления, выход первого элемента И является вторым выходом блока приема, выход i -го регистра приема является первым выходом блока приема. Предлагаемое устройство позволяет задавать коды приоритета микропрограмм, выполняемых модулем системы, а также коды приоритета посту пивших на обслуживание запросов от аналогичных микропрограммных устройств управления. Кроме того,он дает возможность задавать абсолютный приоритет отдельных участков вьшолняемой микропрограммы. Каждая из вьшолняемых микропрограмм М,(i 1,m) имеет определенный приоритет Р; ( j выполнения для осуществления анализа, какую из микропрограмм (свою или поступившег запроса) выполнять устройству. Отдельные участки выполняемой микропрограммы имеют абсолютный приоритет выполнения, т.е. в том случае, когда устройство выходит на обработку такого участка, поступивший запрос на обработку не прерывает выполняемой микропрограммы с более низким приоритетом до окончания обработки участка микропрограммы с абсолютным приоритетом На фиг.1 представлена функциональная схема предлагаемого микропрограммного устройства управления на фиг.2 - функциональная схема бло ка выборки адресных микрокоманд; на фиг.З - функциональная схема бло ка выборки операционных микрокоманд на фиг.4 - функциональная схема бло ка приема; на фиг.З - пример выпол нения i-и задачи системой из трех аналогичных микропрограммных устрой управления t2j,; на фиг.56- то же,д системы из данных микропрограммных устройств 5Т1равления. №1кропрограммное устройство упра ления содержит (фиг.1) бпок 1 выбор адресных микрокоманд, блок 2 выбор операционных микрокоманд, регистр передачи управления, группу элемен 78 той или 4, блок 5 приема, буферный регистр 6, группу элементов И 7, буферный регистр 8, группу элементов И 9, блок 10 сравнения, элемент НЕ 11, одновибратор 12, элемент 13 задержки, группу элементов И 14, дешифратор 15, элемент ИЛИ 16, (V-rpynn элементов И 17, 1-1 7, одновибратор 18,N групп элементов И 19.1-19.N группу элементов И 20. На фиг . 1 обозначены информационный вход 21 устройства, пятый вход 22 блока выборки адресных микрокоманд, информационные входы 23, 24 и 25устройства, информационные выходы 26и 27 устройства, второй 28,первый 29, четвертый 30, третий 31 входы блока выборки адресных микрокоманд, первый 32, пятый 33, третий 34, шестой 35, второй 36, четвертый 37 выходы блока выборки адресных микрокоманд . Блок 1 выборки адресных микрокоманд (фиг.2) содержит группу элементов ИЛИ 38, группу сумматоров 39.1-39.К по модулю два, регистр 40 адреса, дешифратор 41 адреса, элемент 42 задержки, узел 43 памяти адресных микрокоманд. Блок 2 выборки операционных микрокоманд (фиг.З) содержит регистр 44 адреса, дешифратор 45 адреса и узел 46 памяти операционных микрокоманд. Блок 5 приема (фиг.4) содержит демультиплексор 47 с входами 48 и 49, группу из К регистров 50.1-50.К приема (где К- глубина очереди), группу элементов И 51.1-51.К группы элементов ИЛИ 52.1-52. К группу одновибраторов 53.1-53.К группу элементов ИЛИ 54.1-54.К К-1 групп элементов ИЛИ 55.1-55.(К-1), элемент И 56, триггер 57 управления, элемент И 58, элемент 59 задержки. Работа предлагаемого микропрограммного устройства управления возможна в трех режимах: обработки собственных микропрограмм, вьщачи адреса и приоритета микропрограмм на обработку аналогичным микропрограммным устройством управления, обработки микрокоманд по запросу с другого аналогичного устройства. В исходном состоянии элементы памяти устройства находятся в нулевом состоянии. Работа устройства в режиме обработки собственных микропрограмм осуществляется следующим образом. Вначале подают на вход 21 устрой ства код операции, определяющий начальный адрес микропрограммы. Так как блок 5 приема находится в нулевом состоянии (нет запросов с других устройств на обработку), сигнал с третьего выхода этого блока разрешает прохождение со входа 21 начального адреса выполняемой микропрограммы через группу элементов И 20 и группу элементов ИЛИ 38 на информационный вход регистра 40 адреса блока 1 выборки операционных микрокоманд. После прихода на синхронизирующий вход дешифратора 41 адреса импульса с входа 24 происходит выборка управляющей информации из узла 43 памяти по адресу, записанному в регистре 40 адреса. С узла 43 памяти считывается микроко. манда, формат которой определяет адрес операционной г4 крокоманды (выход 32), косвенный адрес следующей адресной микрокоманды (выход 34 идентификатор (признак-метка) окончания выполнения микропрограммы (выход 35), адрес передачи управления (выход 36) и код приоритета выполняемой микропрограммы (выход 37 Код адреса операционной микрокоманды с выхода 32 записывается в регистр 44 адреса (фиг.З) блока 2. По тактовому импульсу, приходящему с задержкой на элементе 42 задержки блока выборки адресных микрокоманд с выхода 33 на синхронизирующий вход дешифратора 45 адреса, считывается операционная микрокоманда на узле 46 памяти на управление, например, арифметико-логическим устройством процессора или другим операционным блоком средств обработки информации. Кроме того, по первой адресной микрокоманде с выхода 37 блока I на информационный вход регистра 3 передачи управления записывается код приоритета выполняемой микропрограммы. Код адреса следующей адресной микрокоманды, снимаемый с выхода 3 блока 1, содержит постоянную Ад и переменную части. Переменная часть кода адреса следуиицей ад ресной микрокоманды определяет мо710дифицируемую часть адреса поступающитчи логическими услопиями на вход 23 блока 1 выборки адресных микрокоманд. Код косвенного адреса следующей адресной М1 крокоманды с выхода 34 поступает на вход 28 и через группу элементов 38 яаписмвается в регистр 40 адреса. Поступающие с входа 22 логические условия модифицируют переменную часть кода на группе сумматоров 39.1-39.К по модулю два. В зависимости от поступивших логических условий в регистре 40 адреса формируется адрес очередной адресной микрокоманды, который с приходом импульса с входа 23 устройства производит выборку новой адресной микрокоманды из узла 43 памяти блока 1 выборки адресных микрокоманд, и устройство функционирует аналогичным образом. В определенных участках микропрограммы могут находиться микрокоманды, осуществляющие вьщачу запроса на обработку микропрограмм аналогичным устройствам управления с определенным приоритетом. Работа устройства в режиме вьщачи запроса заключается в следующем. При необходимости передачи управления другому аналогичному микропрограммному устройству в формате микрокоманды с узла 43 памяти блока 1 считывается информация об адресе следующей микрокоманды с выхода 34 на вход 28 блока 1, код устройства, которому необходимо передать управление с выхода 36, код адреса микропрограммы, с которого устройство должно начать обработку, поступает с выхода 34 на входы N групп элементов И 17.1-17,N Кроме того, с выхода 37 блока выборки адресных микрокоманд считывается код приоритета, с которым должен быть вьтолнен вьщаваемый запрос. Код устройства передачи управления и код приоритета запроса с выходов 36 и 37 блока выборки адресных микрокоманд записываются в регистр 3 передачи управления. При выполнении микрокоманды передачи управления в поле 30 регистра 3 записывается метка-признак, которая поступает на вход группы элементов И 7 и вход группы элементов И 14 и запрещает тем самым перезапись информации соответственно из буферного регистра 6 в буферный регистр 8, а также из блока 5 ема на вход 30 блока 1 выборки адре ных микрокоманд, Код выбора устройства с выхода 3 регистра 3 передачи управления поступает на входы дешифратора 15, на соответствующем выходе которого появляется сигнал, который, поступа на входы групп элементов И 17.1-17. и 19.1-19.N разрешает прохождение кода микропрограммы и кода приорите та на выход 27 устройства. Одновременно с вьщачей запроса на выход 27 устройства код выбора устройства с поля 3.1 регистра 3 передачи управления поступает на вход элемента ИЛИ 16, на выходе которого появляется сигнал логической единицы. Этот сигнал на одновибраторе 18 с задержкой на время вьщачи запроса с выхода 27 устройства формирует импульс, который с выхода одновибратора 18 обнуляет регистр 3 передачи управления. Тем самым заканчивается выполнение микрокоманды передачи управления. Так как в регистр 40 адреса одновременно с вьщачей микрокоманды запроса бьш записан адрес очередной микрокоманды, устройство переходит к ее выполнению описанным образом. Работа устройства в режиме обработки запроса осуществляется следую щим образом. Запрос на обработку с других аналогичных микропрограммных устройств управления приходит на вход 25 устройства. Код запроса на обработку состоит из двух частей: кода адреса микрокоманды, с которой необходимо начать обработку микропрограмм, и кода приоритета вьитолнения запроса. Код запроса с входа 25 устройства через группу элементов ИЛИ 4 поступает на информационныйвход 49 демультиплексора 47 блок 5 приёма (фиг.4). Блок 5 приема организует очередь обработки запросов типа первьм при шел - первым обслужен. Так как до прихода запроса очередь пуста,на ну левых выходах регистров 50.1-50.К приема имеются высокие потенциалы, которые поступает на входы элементов И 51.1-51.К, Однако первый посту пивший запрос поступает через групп элементов ИЛИ 55.(К-1) на информационный вход регистра 50.К приема. так как управляющий сигнал с выхода элемента И 51.К запрещает формирование других управляющих сигналов. При записи кода запроса в регистр 50.К с выхода элемента И 51.К сигнал логического нуля разрешает запись очередного кода запроса в последующий регистр 50.(k-1) приема. Аналогичным образом формируется очередь запросов. Код приоритета поступивщего запроса поступает с выхода регистра 50.К блока 5 приема на вход блока 10 сравнения. В процессе работы микропрограммного устройства управления код приоритета выполняемой микропрограммь с второго поля регистра 3 передачи управления сравнивается с кодом приоритета поступившего запроса, записанного в первом поле блока 5 приема. Сравнение кода приоритета выполняемой микропрограммы с кодом приоритета запроса на обработку происходит на блоке 10 сравнения. Блок 10 сравнения реализует функцию сравнения путем последовательного сравнения разрядов кодов приоритетов, начиная от старших. Если в рязряде i 1,я имеем «Ъ 10, то отношение истинно (А - код приоритета обрабатываемой микропрограммы, В - код приоритета запроса). Если сн-Ь 00 или 11, то значение отношения определяется путем анализа значений в следующем младшем разряде. Определим логическую функцию, на основе которой может быть вычислено значение двоичной переменной 5 представляющей отношение Л Б. Пусть Si переменная, принимающая значение 1, если факт истинности отношения вытекает из анализа значений в разряде i , Из правила сравнения. при 1 1 1 при i 2,n f, ... h ., ... 1 j - признак равенства значений кодов в разрядах от 1 до /i-l включительно, а hj оп 5jbjV«.b ределяется как fj rc(«.vVj){5.Vb.|. S t, т.е. Если 5 1, то и 5 S V S V ч П

13

Таким образом, если код приорите вьшолняемой микропрограммы больше кода приоритета запроса, то на выхо блока 10 сравнения имеется сигнал лгической единицы. В этом случае пре рывания выполняемого процесса не происходит.

Если код приоритета в запросе больше кода приоритета обрабатываемой (собственной) микропрограммы то на выходе блока 10 сравнения появляется сигнал логического нуля и по перепаду на элементе НЕ 11 на выходе одновибратора 12 появляется импульс. Этот импульс поступает на входы группы элементов И 7 и осуществляет тем самым перезапись адреса очередной микрокоманды прерванной микропрограммы из буферного регистра 6 в буферный регистр 8.

В буферном регистре 6 хранятся коды адресов очередных адресных микрокоманд во время выполнения микрокоманд. Поэтому код очередной (не вьщанной на обработку из-за прерывания) адресной микрокоманды переписывается в буферный регистр 8, где хранится на время обработки запроса.

Одновременно с перезаписью кода адреса очередной (невыполненной) адресной микрокоманды в буферный регистр 8 сигнал с выхода одновибратора 12 поступает через вход 31 блока 1 выборки адресных микрокоманд на вход установки в ноль регистра 40 адреса, который обнуляется. Сигнал с выхода одновибратора 12 через элемент 13 задержки поступает на первые входы группы элементов И 14 и разрешает прохождение кода адреса микрокоманды, с которой необходимо начать выполнение микропрограммы запроса, на вход 30 блока 1 выборки адресных микрокоманд. Кроме того, сигнал с выхода одновибратора 12 nocTjmaет на управляющий вход блока 5 приема и переводит триггер 57 управления в единичное состояние.

Адрес поступившего запроса записывается с входа 30 через группу элементов ИЛИ 38 в регистр 40 адреса, и работа микропрограммного устройства управления начинается в режиме обработки запроса аналогично тому, как проходит обработка собственных микрокоманд.

714

По окончании процесса обработки микропрограммы по запросу с выхода 35 блока 1 выборки адресных микрокоманд выдается метка окончания выполнения микропрограммы. Данная метка обнуляет буферньп1 регистр 6 и, поступая на входы группы элементов И 9, разрешает перезапись о коде адреса микрокоманды, невыполненной вследствие прерывания, из буферного регистра 8 в регистр 40 адреса. По окончании выполнения микропрограммы запроса метка с выхода 35 поступает на синхронизирующий вход блока 5 приема. Сигнал с синхронизирующего входа этого блока через элементы И 58 и ИЛИ 54.1-54.К поступает на синхронизирующие входы регистров 50.1-50.К приема. Таким образом, после выполнения запроса очередь продвигается вперед. Далее устройство продолжает работу в одном из перечисленных режимов.

В процессе вьшолнения микропрограммы отдельные участки выполняемой микропрограммы имеют абсолютный приоритет, т.е. эти участки не могут быть прерваны. В этом случае в последней микрокоманде перед участком абсолютного приоритета с выхода 37 блока 1 выборки адресных микрокоманд записывается в поле 3.2 регистра 3 передачи управления код абсолютного приоритета,При выходе из участка абсолютного приоритета в поле 3.2 регистра 7 передачи управления заносится код выполняемой программы.

По окончании выполнения микропрограммы и микpoпpoгpaм запроса с выхода 35 блока 1 выборки адресных микрокоманд поступает сигнал на обнуление буферного регистра 6,. элементы памяти устройства в нулевом (исходном) состоянии.Микропрограммно устройство управления готово к вьшолнению новых микропрограмм.

Таким образом, реализация передачи управления другому микропрограммному устройству, занятому обработкой микрокоманд, осуществление прерывания процесса обработки г-шкрокоманд при запросе на выполнение микро- программы с более высоким приоритетом, а также продолжение процесса обработки микрокоманд после вьщачи запроса позволяет расширить область применения микропрограммного устройства управления.

38

S

34

43

35

36

cfsus.Z

Ittt

6

/5

Фие.З

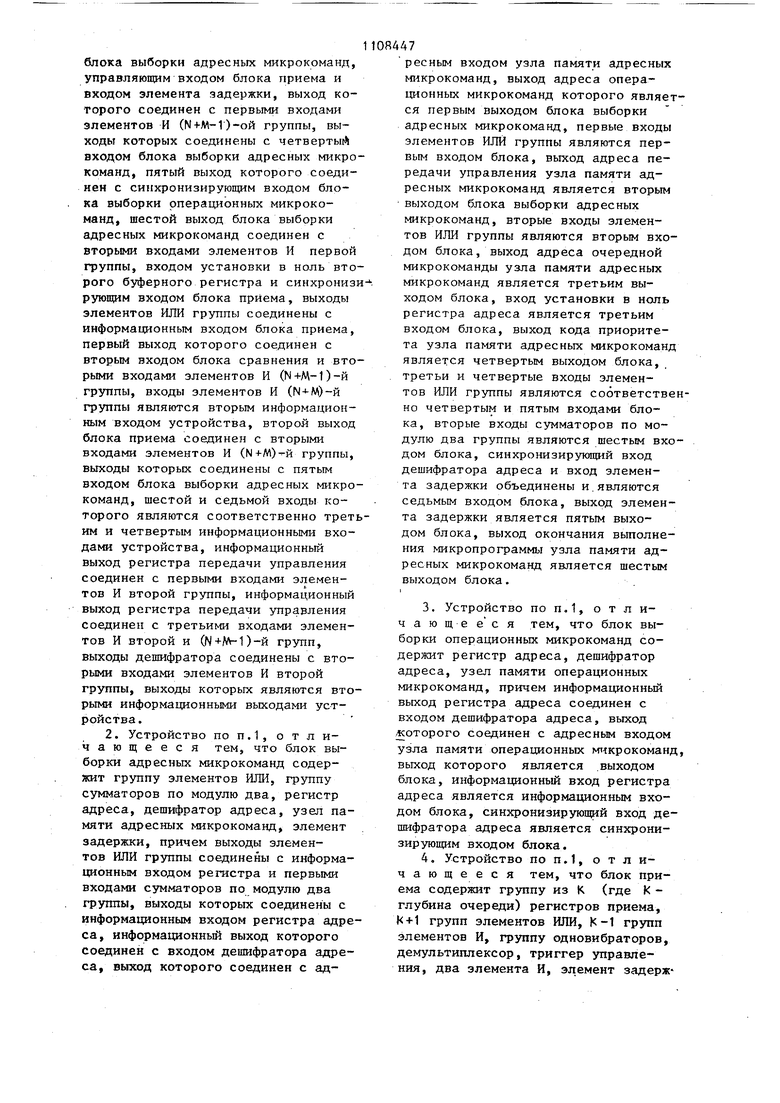

а

МПУ1

мпУг

f///VfJlf/W 5/4/,j,/Aij| 5/ij t,(N,

I

МПУ

мпу

ilM ii t4lN,tiiNi) i(Nf}

I фаз. 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Хассон С | |||

| № кpoпpoгpa fмнoe управление, кн.1 | |||

| М., №ip, 1973 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное устройство управления | 1976 |

|

SU596947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1983-01-11—Подача