рых соединены соответственно с входами данных устройства и регистра данных запросов, счетный вход счетчика битов соединен с выходом второго элемента ИЛИ группы блока управления, первые входы элементов И первой и второй групп соединены с выходом первого элемента И блока управления, вторые входы элементов И первой и второй групп соединены с выходом выбора входа блока памяти группы регистра данных запросов,, выходы данных запросов, адреса сегмента и выбора блока памяти группы которого соединены соответственно с выходом данных запроса устройства,информационным входом регистра адреса сегмента и с первым входом схемы сравнения, второй вход которой соединен с первым выходом дешифратора шагов, с первыми входами первого элемента И второй группы и второго элемента И первой группы блока управления, второй вход которого соединен с выходом схемы сравнения, второй и третий выходы дешифратора состояний соединены с первыми входами соответственно второго элемента И второй группы и третьего элемента И первой группы блока управления , выход дешифратора номера модуля соединен с вторым входом первого элемента И второй группы блока управления, входы считьгоания и разрешения считывания регистра данных запросов соединены соответственно с выходом элемента ИЛИ устройства и с выходом второго элемента И блока управления, вход байтов, вход приема байта и вход запроса регистра данных запросов соединены соответственно с входом байтов устройства, с выходо

третьего элемента И блока управления и с выходом запроса регистра адреса сегмента, адресный выход которого соединен с адресным выходом устройства, управляющий вход которого соединен с управляющим входом регистра адреса сегмента, вход фиксации сравнения, вход сдвига и вход переписи информации регистра данных запросов соединены соответственно с выходом четвертого элемента И первой грзшпы и с выходом третьего элемента ИЛИ группы блока управления и с входом переписи информации устройства, вход синхроимпульса устройства соединен с входом синхроимпульса регистра данных запросов и с первым входом элемента И-ИЛИ блока управления, вход синхроимпульса управления устройства соединен с входом синхроимпульса управления регистра данных запросов и с вторым входом элемента И-ИЛИ блока управления, а в блоке управления первый вход шифратора соединен с входами начальной установки в нуль устройства и первого счетчика, группа выходов шифратора соединена с группой информационных входов второго счетчика, группа выходов которого соединена с группой входов дешифратора шагов, выход элемента И-ИЛИ соединен со счетным входом второго счетчика, третий и четвертый входы элемента И-ИЛИ соединены с единичным выходом второго триггера и с первым входом четвертого элемента И, выход и второй вход которого соединены соответственно со счетным входом первого счетчика и выходом третьего элемента ИЛИ группы, группа выходов первого счетчика соединена с группой входов дешифратора числа сдвигов, выход которого соединен с первыми входами третьего и пятого элементов И и пятым элементом И первой группы, нулевой выход первого триггера соединен с первыми входами шестого и седьмого элементов И, единичный выход первого триггера соединен с первым входом восьмого элемента И, единичный выход третьего триггера соединен с вторым входом седьмого элемента И, нулевой выход третьего триггера соединен с вторыми входами шестого и восьмого элементов И, единичный выход второго триггера соединен с третьими входами шестого седьмого и восьмого элементов И, выход шестого элемента И соединен с первым ВХОДСЯ4 второго и вторым входом пятого элементов И и с первым входом элемента ИЛИ, второй вход которого соединен с выходом восьмого элемента И, с первым входом первого и вторым входом третьего элементов И, третьи входы третьего и пятого элементов И соединены с соответствукицим выходом дешифратора шагов и с вторыми входами второго элемента И второй группы и третьего элемента И первой группы вторые входы первого и второго элементов И соединены с соответствующим выходом дешифратора шагов и с первым входом первого элемента И первой группы, первый вход третьего элемента И второй группы соедин с соответствующим выходом дешифратора шагов и с первым входом шест элемента И первой группы, первый вход четвертого элемента И второй группы соединен с соответствуюшзим выходом дешифратора шагов и с перв входом четвертого элемента И перво группы, первый вход седьмого и второй вход пятого элементов И первой группы соединены с соответствующими выходами дешифратора шагов, выход элемента ИЛИ соединен с соответствующими входами.элементов И второй группы, выход седьмог элемента И соединен с соответствую щими входами элементов И первой группы, выход третьего элемента И второй группы соединен с первыми входами третьего и второго элементов ИЛИ группы, вторые входы котор соединены с выходом седьмого элеме та И первой группы и с первым входом первого элемента ИЛИ группы, второй вход которого соединен с вы ходом четвертого элемента И второй группы, прямой и инверсный выходы первого элемента И второй группы соединены соответственно с первьми 0 входами четвертого и пятого элементов ИЛИ группы, прямой и инверсный выходы второго элемента И второй группы соединены соответственно с первым входом шестого и вторым входом пятого элементов ИЛИ группы, выход шестого элемента И первой группы соединен с третьим входом второго элемента ИЛИ группы, прямой и инверсный выходы третьего элемента И первой группы соединены соответственно с вторым входом шестого и третьим входом пятого элементов ИЛИ группы, прямой и инверсный выходы второго элемента Ц первой группы соединены соответственно с вторым входом четвертого элемента ИЛИ группы и с вторым входом дешифратора, третий вход которого соединен ,с инверсным выходом пятого элемента ИЛИ группы, прямой и инверсный выходы пятого элемента И первой группы соединены соответственно с третьим входом четвертого элемента ИЛИ группы и с четвертым входом шифратора, пятый вход которого соединен с инверсным выходом шестого элемента ИЛИ группы, выход четвертого элемента ИЛИ группь соединен с R -входом второго триггера, выход пятого элемента И является выходом выдачи байта устройст

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

УСТРОЙСТВО ПРИОРИТЕТА, содержащее группу блоков памяти,блок управления, регистр данных запросов отличающееся тем, что, с целью повьпиения быстродействия устройства, оно содержит счетчик, дешифратор номера модуля, счетчик битов, группу элементов И-ИЛИ,три группы элементов И, группу элементов ИСКЛЮЧАННЦЕЕ ИЛИ, дешифратор состояний, регистр адреса сегмента, схему сравнения и элемент ИЛИ,а блок утфавления содержит, шифратор, два счетчика, дешифратор шагов, дешифратор числа сдвигов, три триггера, элемент И-ИЛИ, восемь элементов И, элемент ИЛИ, две группы элементов И и группу элементов ИЛИ, причем нулевой выход первого триггера блока управления соединен с первыми входами разрешения блоков памяти группы,входы начальной установки, Учетный и установки в нуль счетчика соединены соответственно с входом начальной установки устройства, с выходом первого элемента ИЛИ группы блока управления и с единичным выходом второго триггера блока управления, группа выходов счетчика соединена с группой входов дешифратора номера модуля, выходы группы которого соединены с первыми входами элементов И-ИЛИ группы, вторые и третьи входы которых соединены соответственно с выходами элемента ИЛИ и первого элемента И первой группы блока управления , выходы элементов И-ИЛИ группы соединены с первыми управляющими входами соответствующих блоков памяти группы, группы адресных входов которых соединены с (/) группой выходов счетчика битов и С группой входов дешифратора состояний, первый выход которого является выходом пересчета эапросов устройства, вход начальной установки которого соединен с входами начальной установки счетчика битов и регистра адреса сегмента устройства и R и 5-входами первого, второго и треть00 4 О1 его триггеров блока управления, выходы элементов И первой и второй групп соединены с вторыми управляющими входами соответствующих блоков памяти группы, выходы которых соединены с соответствующими входами элемента ИЛИ и с первыми входами элементов И третьей группы, вторые входы которых соединены с выходом первого элемента И первой группы блока управления, выходы элементов И третьей группы соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, вторые входы и выходы кото

Изобретение относится к вычислительной технике и предназначено для уменьшения среднего времени доступа к сегментам информации, размещенным на вращающихся носителях с цикличесКИМ доступом (диски, барабаны и т.д.

Устройства для уменьшения среднего времени доступа для средних ЭВМстроятся в составе блок-мультиплексного канала, который обслуживает до восьми накопителей на дисках. Преимуществом этого класса устройств является совмещение функций канала и контроллера с функцией ускоренного обращения к записям накопителя с пря мым доступом l .

Недостаток этих устройств - приближенный характер определения положения вала накопителя и связанный с этим определенный объем аппаратурных затрат. Кроме того, по мере увеличения единичной емкости накопителей с прямым доступом для ЭВМ возникает необходимость оптимизации доступа к информации в пределах одного накопителя или в пределах части последнего.

Наиболее близким к предлагаемому является устройство для уменьшения среднего времени доступа к сегментам данных, расположенных на дисках (барабанах), состоящее из схемы управления, которая соединена по входу с процессором ввода-вьшода, по выходам - с регистром приема информации, регистром вершины стека, преобразователвм, блоком регистров дельт, схем адресации, стеком, регистром вьщачи информации, блок регистров дельт со динен по входам, с преобразователем схемой управления, по выходу - со схемой адресации, преобразователь соединен по выходу с блоком регистров дельт, по входам - со схемой управления и накопителем на дисках .(барабанах) , схема адресации соедииена по входам с блоком регистров дельт, стеком, схемой управления/ регистр приема информации соединен по входам со схемой управления и процессором, по выходу - с регистро вершины стека регистр вершины стек соединен по выходу со стеком, по входам - со схемой управления, схемой адресации,регистром вершины стека, по выходу - с регистром вьщачи информации, который соединен по входам со схемой управления и стеком, по выходу - с процессором (23, Недостатком устройства является низкое быстродействие. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что в устройство приоритета, содержащее группу блоков памяти, блок управления, регистр данных запросов, введены счетчик, дешифратор номера модуля, счетчик битов, группа элементов И-ИЛИ, три группы элементов И, группа элементов ИС1СПЮЧАЩЕЕ ИЛИ дешифратор состояний, регистр адреса сегмента, схема сравнения и элементх Ш1И, а блок управления содержит шифратор, два счетчика, дешифратор шагов, дешифратор числа сдвигов, три триггера, элемент И-ИЛИ, восемь элементов И, элемент ИЛИ, две грзшпы элеMeHtOB И и группу элементов ИЛИ, причем нулевой выход первого триггера блока управления соединен с первыми входами разрешения блоков памяти группы, входы начальной уста новки, счетный и установки в нуль счетчика соединены соответственно с входом начальной установки устройства,, с выходе первого элемента ИЛИ группы блока управления и с единичным выходом второго триггера блока управления, группа выЬсодов счетчика соединена с групЬой.входов дешифратора номера модуля, выходы группы которого соединены с первыми входами элементов И-ИЛИ группы вторые и третьи входы которых соединены соответственно с выходами элемента ИЛИ и первого элемента И первой группы блока управления , выходы элементов И-И1Ш группы соединены с первыми упра.впяклцими входами соответствующих блоков памяти группы,группы адресных входов которых соединены с группой выходов счетчика битов и группой входов дешифратора состояний, первый выход которого является выходом пересчета запросов устройства, вход начальной установки которого соединен с входа- . мн начальной установки счетчика битов и регистра адреса сегмента устройства и R и 5 - входами первого, второго и третьего триггеров блока управления, выходы элементов И первой и второй групп соединены с вторыми управляющиьга входами соответствующих блоков памяти группы, выходы которых соединены с соответствующими входами элемента ИЛИ и с первьми входами элементов И третьей группы, вторые входы которых соединены с выходом первого элемента И первой группы блока управления, выходы элементов И третьей группы соединены с первыми входами элементов ИСКЛЮЧАЩЕЕ ИЛИ группы, вторые входы и выходы которых соединены соответственно с входами данных устройства и регистра данных запросов, счетный вход счетчика битов соединен с выходом второго элемента ИЛИ группы блока управления, первые входы элементов И первой и второй грзтп соединены с выходом первого элемента И блока управления, вторые входы элементов И первой и второй групп соединены с выходом выбора входа блока памяти группы регистра данных запросов, шлходы данных запросов, адреса сегмента и выбора блока памяти группы которого соединены соответственно с выходом данных запроса устройства, информационньм входом регистра адреса сегмента и с первым входом схемы сравнения второй вход которой соединен с первым выходом дешифратора шагов, с первыми входами первого элемента И второй группы и второго элемента И первой группы блока управления, второй вход которого соединен с выходом схемы сравнения, второй и третий выходы дешифратора состояний соединен с первыми входами соответственно второго элемента И второй группы и третьего элемента И первой группы блока управления, выход дешифратора номера модуля, соединен с вторым входом первого элемента И второй группы блока управления, входы считьшания и. разрешения считывания регистра данных запросов соединены соответственно с выходом элемента ИЛИ устройства и с выходом второго элемента И блока управления, вхо байтов, вход приема байта и вход запроса регистра данных запросов соединены соответственно с входом байтов устройства, с выходом третьего элемента И блока управления и с выходом запроса регистра адреса сегмента, адресный выход которого соединен с выходом устройства, управляющий вход которого соединен с управляющим входом регистра адреса сегмента, вход фиксации сравнения, вход сдвига и вход переписи

информации регистра данных запросов соединены соответственно с

выходом четвертого элемента И первой группы и с выходом третьего элемента ИЛИ группы блока управления и с входом переписи информации устройства, вход синхроимпульса устройства соединен с входом синхроимпульса регистра данных запросов и с первым входом элемента И-ИП блока управления, вход синхроимпульса управления устройства соединен с входом синхроимпульса управления регистра данных запросов и с вторым входом элемента И-Ш1И блока управления, а в блоке управления первый вход шифратора соединен с входами начальной установки в нуль устройства и первого счетчика, группа выходов шифратора соединена с группой информационных входов второго счетчика, группа выходов которого соединена с группой входов дешифратора шагов, выход элемента И-ИЛИ соединен со счетным входом второго счетчика, третий и четвертый входы элемента И-ИПИ соединены с единичным выходом второго триггера и с первым входом четвертого элемента И, выход и второй вход которого соединены соответственно со счетным входом первого счетчика и выходом третьего элемента ИЛИ группы, группа выходов первого

счетчика соединена с группой входов дешифратора числа сдвигов, выход которого соединен с первыми входами третьего и пятого элементов И и пятым элементом И первой группы, нулевой выход первого триггера соединен с первыми входами шестого и седьмого элементов И, единичный выход первого триггера соединен с первым входом восьмого элемента И, единичный выход первого триггера соединен с первым входом восьмого элемента И, единичный выход третьго триггера соединен с вторым входом седьмого элемента И, нулевой выход третьего триггера соединен с вторыми входами шестого и восьмого элементов И, единичный выход второго триггера соединен с третьими входами шестого, седьмого и восьмого элементов И, выход шестого элемента И соединен с первым входом второго и вторым входом пятого элемента И, и с первым входом элемента ИЛИ, второй вход которого соединен с выходом восьмого элемента И, с первым входом первого и вторым входом третьего элемента И, третьи входы третьего и пятого элементов И соединены с соответствующим выходом дешифратора шагов и с вторыми входами второго элемента И второй группы и третьего элемента И первой группы, вторые входы первого и второго элементов И соединены с соответствующим выходом дешифратора шагов и с первым входом первого элемента И первой группы, первый вход третьего элемента И второй группы соединен с соответствующим выходом дешифратора шагов и с первым входом шестого элемента И первой группы, первый вход четвертого элемента И второй группы соединен с соответствующим выходом дешифратора шагов и с первым входом четвертого

элемента И первой группы, первьй вход седьмого и второй вход пятого элементов И первой группы соединены с соответствующими выходами дешифратора шагов, выход элемента ИЛИ соединен с соответствующими входами элементов И второй группы, выход седьмого элемента И соединен с соответствующими входами элементов И первой группы, выход третьего элемента И второй группы соединен с первыми входами третьего и второго

элементов ИЛИ группы, вторые входы которых соединены с выходом седьмог элемента И первой группы и с первым входом первого элемента ИЛИ группы, второй вход которого соединен с вых дом четвертого элемента И второй группы, прямой и инверсный выходы первого элемента И второй группы соединены соответственно с первыми входами четвертого и пятого элементов ИЛИ группы,прямой и инверсный выходы второго элемента И второй группы соединены соответственно с первым входом шестого и вторым входом пятого элементов ИЛИ группы, выход шестого элемента И первой группы соединен с третьим входом второго элемента ИЛИ группы,прямой и инверсньй выходы третьего элемента И первой группы соединены соответственно с вторым входом шестого и третьим входом пятого элементов ИЛИ группы, прямой и инверсный выходы второго элемента И первой группы соединены соответственно . с вторым входом четвертого элемента ИЛИ группы и с вторым входом шифратора, третий вход которого соединен с инверсным выходом пятого элемента ИЛИ группы, прямой и инверсный выходы пятого элемента И первой группы соединены соответственно с третьим входом четвертого элемента ИЛИ группы и с четвертым входим шифратора, пятьш вход которого соединен с инверсны } выходом шестого элемента ИЛИ группы, выход четвертого элемента ШМ группы соединен с R -входом второго триггера, выход пятого элемента И является выходом вьщачи байта устройства.

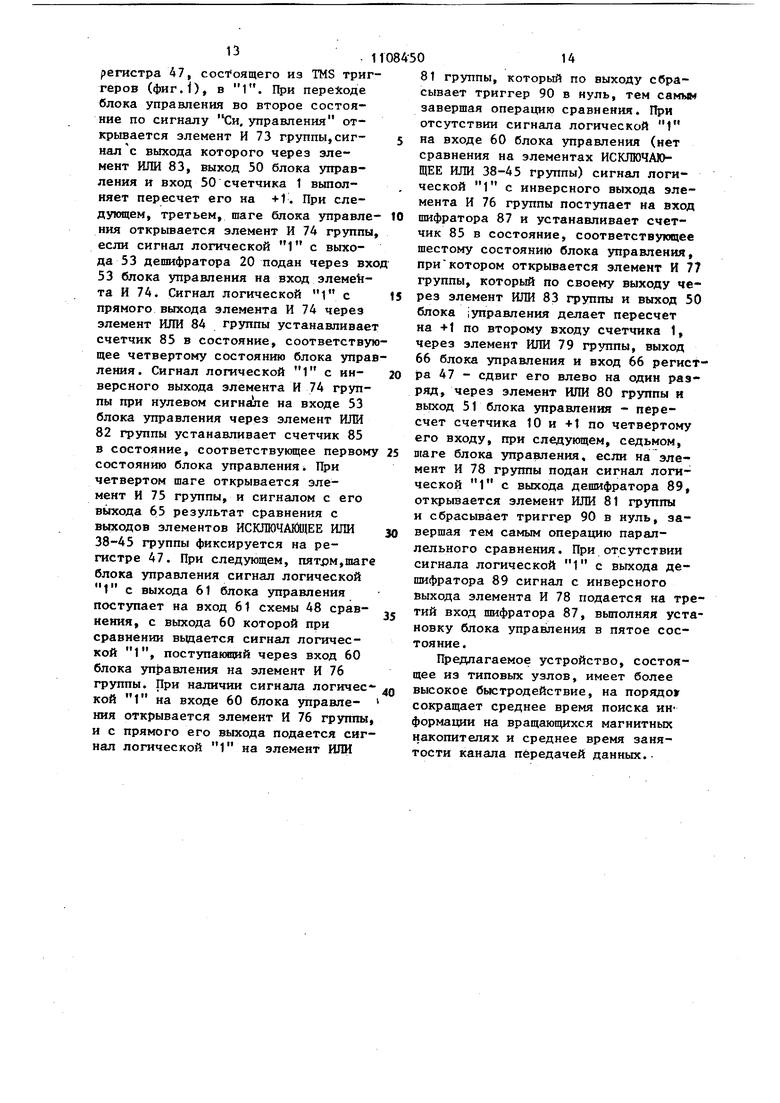

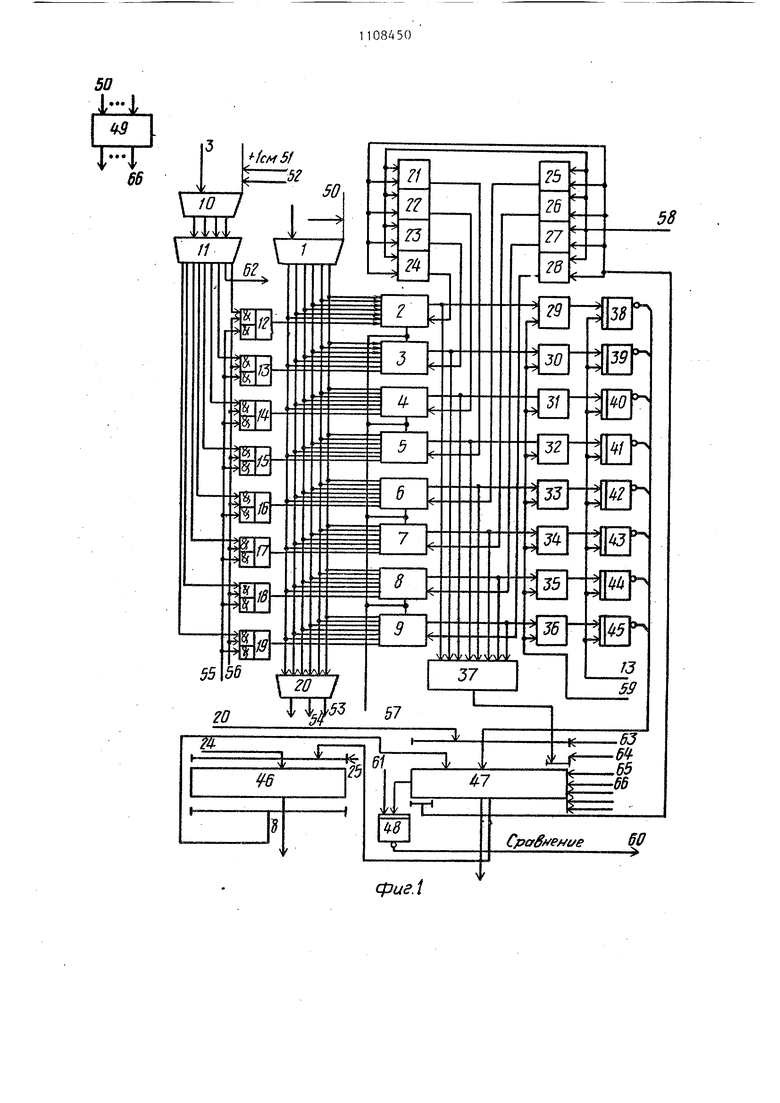

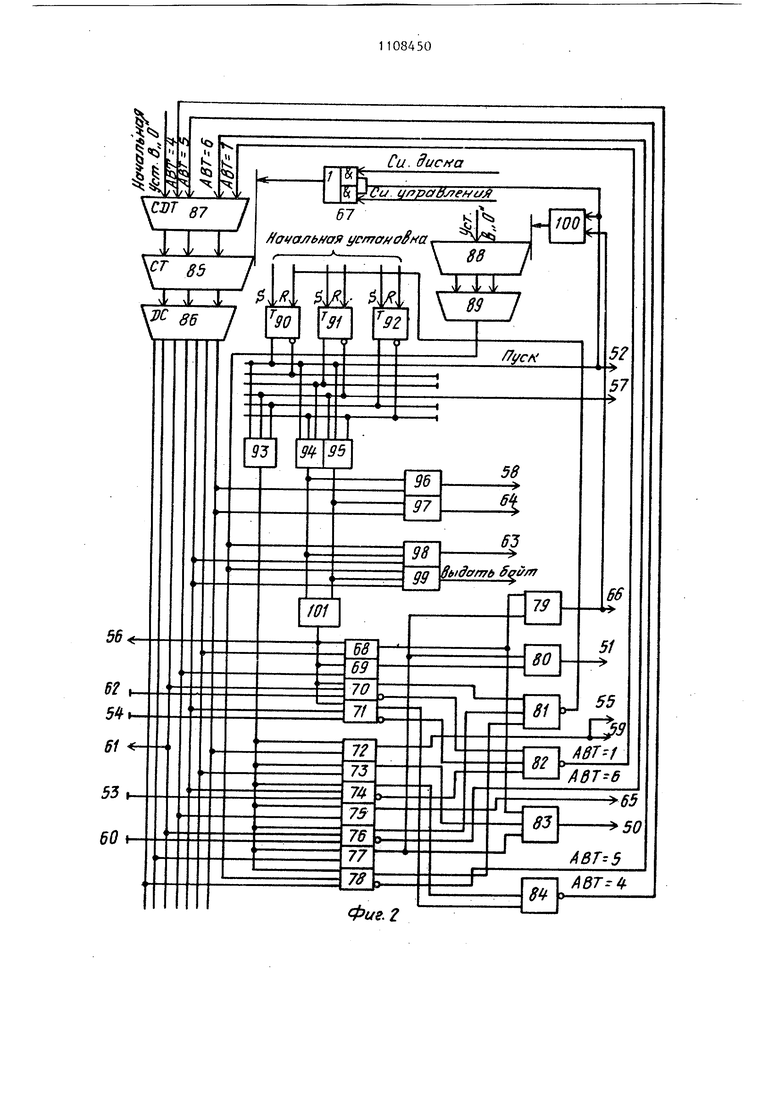

На фиг.1 представлена блок-схема предлагаемого устройства, на фиг,2 - йпок-схема блока управления на фиг. 3 - блок-схема регистра за,просов данных. Устройство запроса состоит из счетчика 1 битов, группы блоков 2-9 памяти, счетчика 10, дешифратора 11 номера модуля, группы элементов И-ИЛИ 12-19, дешифратора 20 состояний, первой и второй групп элементов И 21-24 и 25-28, третьей груп пы элементов И 29-36, элемента ИЛИ 37, группы элементов ИСКЛЮЧАЩЕЕ ИЛИ 38-45, регистра 46 адреса сегмента,, регистра 47 запросов данных, схемы

I

48 сравнения, блока 49 управления с входами и выходами 50-66, состоящего из элемента И-ШШ 67, второй и первой групп элементов И 68-71 и 5 72-78, группы элементов ИЖ 79-84, второго счетчика 85, дешифратора 86 шагов, шифратора 87, первого счетчика 88, дешифратора 89 числа сдвигов, триггеров 90-92, элементов И О 93-100, элемента ИЛИ 101,

Входной-выходной регистр содержит элементы И 102-105, элементы 3 И-ШШ 106-109, триггеры 110-113, вход 114 байтов устройства.

5 Устройство эапроса работает следующим образом,

Данные управляющие слова обмена

(УСО) поступают по-байтно по входу

из процессора на регистр 47 - го 8 байтов. Епок 49 управления

реализует три типа микропрограммы.

Пример для случая памяти для восьми слов УСО;

I, Микропрограмма записи в буфер 5 ную память N слов, .

Начальная установка триггеров режима и счетчиков: Т.ЗП/ЧТ «- 1 установка триггера 91 в режим записи-, Т.СР/ВУФ - О - установка 30 триггера 92 в режим буферизации, СМ - О - установка в нуль счетчика 1 i СДВ - О - установка в нуль счетчика 88; ТПО f- О - установка триггера 90 в режим ожидания. з5 0. Пуск: ТПО ,

1 бит регистра 47 - СДВ СДВ+1, 40 . 3. Проверить: если , то принять очередной байт на регистр-47j проверить: если , то перейти в п.4, иначе - в п.1;

4, +1 в счетчик 10 - , 45 5. Проверить: если СМ N 8, то ТПО «-- О, иначе перейти в п.1. II, Микропрограмма чтения из блоков памяти N слов, N 8, Начальная установка триггеров и счетчиков: Т.ЗП/ЧТ «-О - установка триггера 30 в режим чтенияf Т.СР/БУФ -«-О - установка триггера 91 в режим буферизации, СМ О установка в нуль счетчика 10, ТПО - Of САБ - О - установка в нуль счетчика 1, СДВ О - установка в нуль счетчика 88. 0. Пуск: ТПО «-1 1.Чтение 1 бита на регистр 47 из памяти/ 2.САБ САБ+1; сдвиг влево на Iбит регистра 47 - (-1; 3. Проверить: если , то вы дать из регистра 47 один байт, проверить: если , то перейти в п.4, иначе - в n.lj 4.+1 в счетчик 10 - , 5.Проверить: если СМ N 8, то ТПО - О, иначе перейти в п.1. III. Микропрограмма параллельно чтения, сравнения, получения резул татов сравнения для N слов, Начальная установка триггеров и счетчиков: Т. ЗП/ЧТ «- О - устано ка триггера 91 в режим чтенияj Т. СР/БУФ - О - установка тригге ра 92 в режим параллельного сравне ния j СМ - О - установка в нуль счетчика 10 СДВ - О - установка нуль счетчика 88, ТПО - О - установка в нуль триггера 90. 0.Пуск: ТПО -/, 1.Параллельное чтение N слов из блоков памяти на схему сравнения/2.САБ САБ+1; 3.Проверить: если (17 и 40 - граница поля адреса сегментов в УСО), то перейти в п.4, иначе в п. 1; 4.Запись результатов сравнения на регистр 47/ 5.Проверить: если левый бит ра вен 1, то перейти к микропрограмме IIдля чтения из памяти, ТПО О, иначе перейти в п.7/ 6.Сдвиг влево на 1 бит, СДВ СДВ+1, 7.Проверить: если , то О, иначе перейти в п.5. Для записи управляющих слов УСО в память процессор через блок сопряжения (на фиг.1 и 2 не показан) с помощью команд ввода-вывода уста навливает режим работы микропрограммы, определяющий последовательную запись слов УСО в блоки 2-9 памяти группы. При этом режим записи для блоков 2-9 памяти группы устанавливается по входу 57 блоков памяти, на который подается с нулевого входа триггера 19 сигнал логической 1. Режим последовател ного заполнения блоков 2-9 памяти группы определяется входом 56 эле010ментов И-ШШ 12-19 на которые подается сигнал логической 1 с выхода элемента ИЛИ 101, который пропускает сигнал логической 1 с Открытого элемента И 94. Режим прохода сигналов через элементы И 21-28 групп устанавливается разрешающим сигналом по входу 58, на который подается сигнал логической 1 с выхода элемента И 96, когда по сигналу Пуск, подаваемому с единичного выхода триггера 90, открывается первый вход элемента И-ИЛИ 67 и счетчик 85 вьтолняет пересчет на +1, в результате чего на первом выходе дешифратора 86 появляется сигнал логической 1. Так как счетчики 1 и 10 находятся в первоначально установленном нулевом состоянии первые их выходы сигналами логической 1 выбирают соответственно первый бит в первом блоке 2 памяти группы, и бит с самого левого разряда регистра 47 записывается в блок 2 памяти группы. Через интервал времени, определяемый циклом работы схемы записи в блоки памяти, приходящий следующий по входу сигнал Си.управления переводит счетчик 85 и его дешифратор 86 во второе состояние, по которому сигналом логической 1 с второго выхода дещифратора 86 открывается элемент И 68 группы, а сигналом логического О с первого выхода дещифратора 86 закрывается элемент И 96. Сигнал логической 1 с выхода элемента И 68 группы поступает на вход элемента ИЛИ 79 группы, и вход элемента ИЛИ 83 группы, в результате чего вьтолняется соответственно пересчет счетчика 88 на +1, а через выход блока управления и вход 66 регистра 47 - сдвиг последнего бита влево на один разряд. После этого по сигналу Си.управления блок управления перехоит в третье состояние, по которому сигнал логической 1 подается с третьего выхода дешифратора 86 на вход элемента И 98, сигнал подается через выход блока vпoaвлeия на вход 63 регистра 47 в том лучае, если с выхода дешифратора 89 ыдается сигнал логической 1, укаывакиций на выполнение N 8 сдвигов регистра 47, после чего следующий байт принимается на регистр А7. С прямого выхода элемента И 71 группы вьдаетсясигнал логической 1, если с выхода 54 дешифратора 20 пода сигнал логической 1, указывающей на пересчет и заполнение одного блока памяти. При выполнении этого условия счетчик 85 устанавливается в состояние АВТ 4 через элемент ИЛ 84 группы и шифратор 87, в результате чего блок управления переходит в четвертое состояние j при кoтopo открывается элемент И 69 группы и элемент ИЛИ группы и через выход 51 блока управления вьшолняется пересче на 1 счетчика 10 через его вход 51 . По следующему, приходящему сигналу Си.управления блок управления переходит в пятое состояние, при котором с пятого выхода дешифратора 86 сигнал логической 1 поступает на вход элемента И 70 группы. В зависимости от наличия или отсутствия сигнала логической 1, поступающего с выхода 62 дешифратора 11 на вход 62 блока управления, возбуждается соответственно прямой или инверсный выход элемента И 70 группы. Сигнал с прямого выхода элемента И 70 группы через элемент ИЛИ 81 группы устанавливает триггер 90 в нулевое состояние, на чем и заканчивается микропрограмма записи. Сигнал с инверсного выхода элемента И 71 группы через элемент ИЛИ 82 группы устанавливает счетчик 85 в первое состоя нив через шифратор 87. Блок управления начинает работать с первого шага микропрограммы, но запись уже производится в следующий по порядку блок 3 памяти группы. По сигналу логического О с единичного выхода тригге,ра 90 закрываются элементы И-ИЛИ 67 и элемент И 100, тем самым предотвра щая .продвижение до следующего шага блока управления (фиг.2). Операция чтения УСО из памяти выполняется ана логично операции записи за тем исключением, что для ее выполнения на блоки 2-9 памяти группы с выхода триггера 91 через выход 57 блока управления и через вход 57 блоков 2-9 памяти группы подается сигнал логического О, устанавливающий режим чтения блоков памяти, а считывание по битно с каждого из блоков памяти на регистр 47 вьтояняется через элемент ИЛИ 37 при наличии сигналау поступающего с выхода элемента И 97 через выход 64 блока управления и вход 64 регистра 47. При операции чтения вместо элемента И 94 работает элемент И 95,вместо элемента И 96 - элемент И 97,вместо элемента И 98 - элемент И 99.0пе,элемента И 98 - элемент И 99. Операция параллельного сравнения (микропрограмма III) синхронизируется сигналом СИ диска, поступающим на вход блока управления. При этом поступление сигнала Си.управления по входу блока управления синхронизируется внешним по отношению к устройству запросч управлением диска (на фиг.2 не показано). Внешнее управление производит также начальную установку триггеров 90-92 и счетчиков 1,10,85 и 88, а также пуск блока управления установкой в 1 триггера 90. При пуске блока управления в режиме параллельного сравнения открьшается элемент И 93 сигналами логической 1 соответственно с единичного выхода триггера 90, нулевого выхода триггера 91 и единичного выхода триггера 92. При этом сигнал логической 1 с выхода элемента И 93 поступает на входы элементов И 72-78 группы. Сигнал Пуск, поступающий с единичного выхода триггера, открывает элемент И-ИЛИ 67 и синхросигнал Си.диска через вход блока управления переводит счетчик 85 в первое состояние, при котором возбуждается первый выход дешифратора 86, сигнал которого открьшает элемент И 72 группы. Сигнал логической 1 с выхода элемента 72 группы через выход 55 блока управления и вход 55 элементов И-ИЛИ 12 и 13 группы устанавливает последние в режим параллельного выбора всех блоков 2-9 памяти. Сигнал с выхода 59 блока управления также открывает элементы И 21-28 групп через вход 59 для параллельного приема битов из блоков 2-9 памяти. Поступающие синхронно с Си.диска биты диска на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 38-45 группы одновременно сравниваются с битами, поступающими соответственно иэ каждого блока 2-9 памяти. В случае одного сравнения на одном из элементов ИСКПГОЧАЩЕЕ ИЛИ 38-45 сигнал логической f устанавливает соответствующий разряз регистра 47, состоящего из TMS триг геров (фиг. О, в 1. При блока управления во второе состояние по сигналу Си, управления открывается элемент И 73 группы,сигнал с выхода которого через элемент ИЛИ 83, выход 50 блока управления и вход 50 счетчика 1 выполняет пересчет его на +1. При следующем, третьем, шаге блока управле ния открывается элемент И 74 группы если сигнал логической 1 с выхода 53 дешифратора 20 подан через вх 53 блока управления на вход элемейта И 74. Сигнал логической 1 с прямого выхода элемента И 74 через элемент ИЛИ 84 группы устанавливае счетчик 85 в состояние, соответству щее четвертому состоянию блока упра ления. Сигнал логической 1 с инверсного выхода элемента И 74 группы при нулевом на входе 53 блока управления через элемент ИЛИ 82 группы устанавливает счетчик 85 в состояние, соответствующее первом состоянию блока управления При четвертом шаге открывается элемент И 75 группы, и сигналом с его выхода 65 результат сравнения с выходов элементов ИСКЛЮЧАНЙ1ЕЕ ИЛИ 38-45 группы фиксируется на регистре 47. При следующем, пят)м,шаг блока управления сигнал логической 1 с выхода 61 блока управления поступает на вход 61 схемы 48 сравнения, с выхода 60 которой при сравнении вьщается сигнал логической 1, поступающий через вход 60 блока управления на элемент И 76 группы. При наличии сигнала логичес кой 1 на входе 60 блока управления открывается элемент И 76 группы и с прямого его выхода подается сиг нал логической 1 на элемент ИЛИ 81 группы, который по выходу сбрасывает триггер 90 в нуль, тем самым завершая операцию сравнения. При отсутствии сигнала логической 1 на входе 60 блока управления (нет сравнения на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 38-45 группы) сигнал логической 1 с инверсного выхода элемента И 76 группы поступает на вход шифратора 87 и устанавливает счетчик 85 в состояние, соответствующее шестому состоянию блока управления, прикотором открывается элемент И 77 группы, который по своему выходу через элемент ИЛИ 83 группы и выход 50 блока iуправления делает пересчет на +1 по второму входу счетчика 1, через элемент ИЛИ 79 группы, выход 66 блока управления и вход 66 регистра 47 - сдвиг его влево на один разряд, через элемент ИЛИ 80 группы и выход 51 блока управления - пересчет счетчика 10 и +1 по четвертому его входу, при следующем, седьмом, шаге блока управления, если на элемент И 78 группы подан сигнал логической 1 с выхода дешифратора 89, открьгоается элемент ИЛИ 81 группы и сбрасывает триггер 90 в нуль, завершая тем самым операцию параллельного сравнения. При отсутствии сигнала логической 1 с выхода дешифратора 89 сигнал с инверсного выхода элемента И 78 подается на третий вход шифратора 87, выполняя установку блока управления в пятое состояние . Предлагаемое устройство, состоящее из типовых узлов, имеет более высокое быстродействие, на порядо сокращает среднее время поиска информации на вращающихся магнитных накопителях и среднее время занятости канала передачей данных.50

i-X

TFT

66

cpue.i

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Катцан Г | |||

| Разборное колесо | 1921 |

|

SU370A1 |

| М., Мир, 1974, с | |||

| Способ получения олифы или массы для приготовления лаков | 1913 |

|

SU507A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент Великобритании № 1340003, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

Авторы

Даты

1984-08-15—Публикация

1982-11-22—Подача