тов и третьей группы соединены с входами задания поряд15 а преобразования

вычислителя,а их вькоды,подключены к входам элемента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегро-дифференциальный вычислитель | 1980 |

|

SU955051A1 |

| Цифровой регулятор | 1980 |

|

SU938255A1 |

| Интегро-дифференциальный вычислитель | 1981 |

|

SU1020823A1 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

| Интегродифференциальный вычислитель | 1981 |

|

SU1007105A1 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU960813A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Цифровой регулятор | 1979 |

|

SU938253A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

ИНТЕГРО-ДИФФЕРЕНЦИАЛЬНЫЙ ВЫЧИСЛИТЕЛЬ по авт.ев, № 955051, отличающийся тем, что, с целью расширения функциональных возможностей за счет вычисления интегро-дифференциальных преобразований п-го порядка, в него введены девятый регистр сдвига, второй сумматор, третий формирователь дополнительного кода, п - разрядный распределитель импульсов, второй триггер, первая, вторая и третья группы элементов И, третий, четвертый, пятый и шестой элементы И и элемент ИЛИ, причем четвертый выход блока синхро низации соединен с входом м -разрядного распределителя импульсов, первые входы 1-х (,п) элементов И первой, второй и третьей групп соединены соответственно с выходом -го разряда распределителя импульсов, вторые входы элементов И первой и второй групп соединены соответственно с выходом второго формирователя дополнительного кода и вторым выходом блока формирования знака, выход элемента ИЛИ соединен с первым входом третьего элемента И, второй вход которого соединен с выходом элемента задержки, выход третьего элемента И соединен с первым входом второго сумматора, второй вход которого соединен с выходом девятого регистра сдвига и с информационным входом третьего формирователя дополнительного кода, выход второго сумматора соединен с информационным входом девятого регистра сдвига и с первым входом четвертого элемента И, выход которого соединен с входом установки в 1 второго триггера, третий выход блока синхронизации соединен с вторым входом четвертого элемента И и с входом установки в О второго триггера, прямой выходjкоторого соединен с первым входом пятого элемента И и с управляющим входом третьего формирователя дополнительного кода, выход . которого соединен с первым входом шестого элемента И, девятый выход блока синхронизации соединен с вторыми входами пятого и шестого элементов И, выходы которых являются соответственно выходами общего знака и общего 00 преобразования вычислителя, выходы частного преобразования с первого по 4; DI п-й порядок вычислителя и выходы знака частных преобразований вычислителя соединены соответственно с выходами элементов И первой и второй групп, вход синхронизации девятого регистра сдвига соединен с десятым выходом блока синхронизации, одиннадцатый выход которого соедийен с входом управления девятого регистра сдвига, двенадцатый выход блока синхронизации соединен с входом сброса второго сумматора и третьего формирователя дополнительного кода, входы элемен

I

Изобретение относится к автоматике и вычислительной технике и может быть использовано для моделирования и управления динамическими объектами в различных отраслях промышленности.

По основному авт.св. № 955051 известен интегро-дифференциальный вычислитель, содержащий первый регистр сдвига, информационный вход которого соединен с выходом сумматора и с первым входом блока формирования знака второй вход которого соединен с входом знака входной информации вычислителя, третья группа входов - с первой группой входов блока синхронизации, первый выход блока формирования знака соединен с первым входом первого формирователя дополнительного кода, а второй выход соединен с первым входом второго формирователя дополнительного кода, второй вход которого подключен к первому входу первого коммутатора и к выходу элеме та задержки, вход которого соединен с выходом первого регистра сдвига и с вторым входом первого коммутатора, выход которого подключен к первому входу второго коммутатора, выход которого подключен к первому входу сумматора, второй вход которого соеди нен с выходом первого формирователя дополнительного кода, второй вход которого подключен к выходу первого злемента И, первый вход которого соединен с первым выходом триггера, первьй вход которого подключен к выходу

второго злемента И, первый вход котО| рого соединен с вторым выходом блока

синхронизации, третий выход которого подключен к второму входу триггера, а второй вход второго элемента И соединен с выходом третьего коммутатора и с информационным входом второго регистра сдвига, третий регистр сдвига и четвертый коммутатор, первый вход которого соединен с входом абсолютной величины вычислителя, а выход - с информационным входом четвертого регистра сдвига, пятый.

шестой, седьмой и восьмой регистры сдвига и пятьй, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый коммутаторы, причем первый вход пятого коммутатора соединен с выходом второго формиро- вателя дополнительного кода и с первым входом шестого коммутатора, второй вход - с четвертым выходом блока синхронизации, с вторым входом второго коммутатора, с первым входом седьмого коммутатора, третий вход с выходом пятого регистра сдвига, с первым входом восьмого коммутатора

и с первым входом девятого коммутатора, а выход - с первым входом десятого коммутатора, второй вход которого подключен к пятому выходу блока синхронизации и к второму входу девятого коммутатора, третий вход которого соединен с третьим входом десятоного коммутатора и с выходом шестого регистра сдвига, информационный вход которого подключен к выходу десятого коммутатора, выход девятого коммутатора соединен с информационным входом пятого регистра сдвига, шестой выход блока синхронизации подключен к первому входу одиннадцатого коммутатора и к первому входу двенад-. цатого коммутатора, второй вход которого соединен с вторым входом одиннадцатого коммутатора и с выходом седьмого регистра сдига, информационный вход которого подключен к второ- му входу первого элемента Ник выоду одиннадцатого коммутатора, третий вход которого соединен с третьим входом двенадцатого коммутатора и

с вьпсодом восьмого регистра сдвига, инфо|рмационный вход которого подключен к выходу двенадцатого коммутатора, седьмой выход блока синхронизации соединен с третьим входом первого коммутатора, восьмой выход блока синхронизации соединен с первым вхоом третьего коммутатора, второй вход которого подключен к выходу третьего регистра сдвига, информационный вход которого соединен с выходом седьмого коммутатора, второй вход которого подключен к выходу второго регистра сдвига, а третий вход - к выходу шестого коммутатора, второй вход которого соединен с входом абсолютной величины вычислителя, а третий вход - с девятым выходом блока синхронизации и с вторыми входами четвертого и восьмого коммутаторов, третьи входы которых подключены к выходу четвертого регистра сдвига, выход восьмого коммутатора соединен с третьим входом третьего коммутатора 1 3.

Недостатками известного интегродифференциального вычислителя являютсГя ограниченные функциональные возможности, которые не позволяют формировать сложные интегро-дифференциальные преобразования, составленные из интегро-дифференциальных преобразований с первого по п-и порядок.

Цель изобретения - расширение функциональных возможностей за счет вы1

числения интегро-дифференциальных преобразований п-го порядка.

Указанная цель достигается тем, что в интегро-дифференциальный вычислитель введены девятый регистр сдвига, второй сумматор, третий формирователь дополнительного кода, п -разрядный распределитель импульсов, второй триггер, первая, вторая и третья группы элементов И, третий, четвертый, пятый и шестой злементы И и элемент ИЛИ, причем четвертый выход блока синхронизации соединен с входом П-разрядного распределителя импульсов, первые входы i-х ( i 1, п ) элемент тов И первой, второй и третьей групп соединены соответственно с выходом i-ro разряда распределителя импульсов, вторые входы элементов И первой и второй групп соединены соответственно с выходом второго формирователя дополнительного кода и вторым выходом блока формирования знака, выход элемента ИЛИ соединен с первым входом третьего элемента И, второй вход которого соединен с выходом элемента задержки, выход третьего элемента И соединен с первым входом второго сумматора, второй вход которого Соединен с выходом девятогорегистра сдвига и с информационным входом третьего формирователя дополнительного кода, выход второго сумматора соединен с информацион-. ным входом девятого регистра сдвига и с первым входом четвертого элемента И, выход которого соединен с входом установки в 1 ВТОРОГО триггера, третий выход блока синхронизации соединен с вторым входом четвертого элемента И и с входом установки в О второго триггера, прямой выход которо го соединен с первым входом пятого элемента И и с управляющим .входом

третьего формирователя дополнительно го кода, выход которого соединен с

первым входом шестого элемента И, девятьга выход блока синхронизации соединен с вторыми входами пятого и шестого элементов И, выходы которых являются соответственно выходами общего знака и общего преобразования вы- числителя, выходы частного преобразования с первого по h -и порядок вычислителя и выходы знака частных преобразований вычислителя соединены соответственно с выходами элементов И первой и второй групп, вход синхронизации девятого регистра сдвига соединен 1 с десятым выходом блока синхронизации, одиннадцатый вьгход которого соединен с входом управления депятого регистра сдвига, двенадцатый выход блока синхронизации соединен с входом сброса второго сумматора и третьего формирователя дополнительного кода, входы элементов И третьей группы соединены с входами задания порядка преобразования вычислителя, а их выходы подключень к входам элемента ИЛИ.

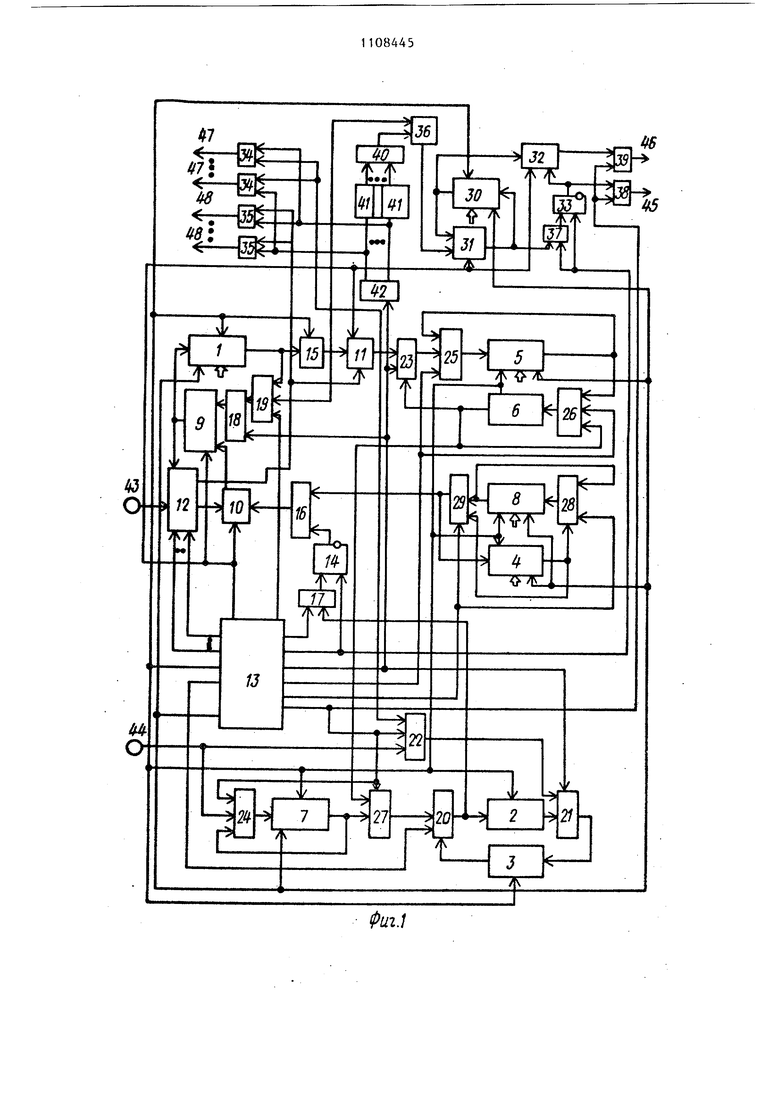

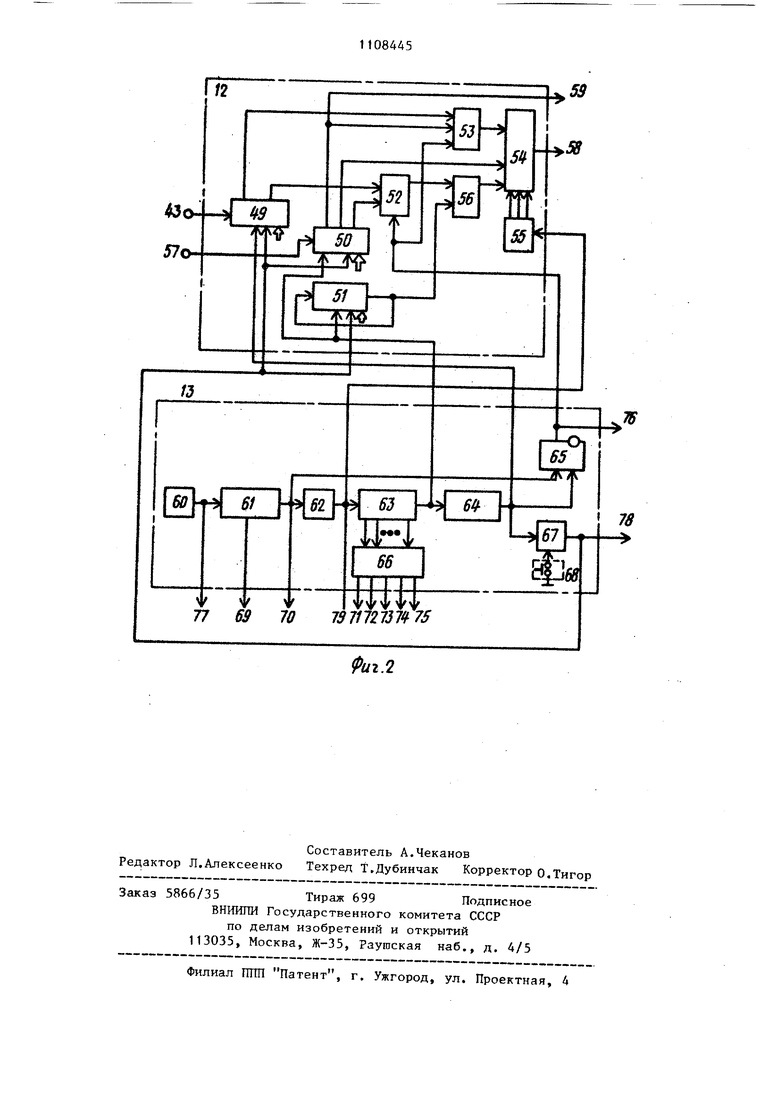

На фиг. 1 изображена структурная схема интегро-дифференциального вычислителя j на фиг. 2 .- структурные схемы блока формирования знака и блока синхронизации.

Интегро-дифференциальный вычислитель содержит регистры 1-8 сдвига, сумматор 9, формирователи 10 и 11 дополнительного кода, блок 12 формирования знака, блок 13 синхронизации, 5 -триггер 14, элемент 15 задержки, элементы И 16 и 17, коммутаторы 18-29, регистр 30 сдвига, сумматор 31, формирователь 32 дополнительного кода, 5-триггер 33, группы элементов И 34 и 35, элементы И 36-39 элемент ИЛИ 40, группу элементов И 41, п -разрядный распределитель 42 импульсов, вход 43 знака входной информации вычислителя, вход 44 абсолютной величины вычислителя, выход

45общего знака вычислителя, выход

46общего преобразования вычислителя, группу выходов 47 частного преобразования вычислителя и группу выходов 48 знака частных преобразований вычислителя.

Выход регистра 1 сдвига соединен с входом элемента 15 задержки и с вторым входом коммутатора 19, выход и первый вход которого соединены соответственно с первым входом коммутатора 18 и с выходом элемента 15 за,цержки.

Выход регистра 2 сдвига соединен с вторым входом коммутатора 21, выход которого соединен с информационным входом регистра 3 сдвига, информационный вход регистра 2 сдвига соединен с вторым входом элемента И 17 и с выходом коммутатора 20, второй вход которого подключен к выходу регистра 3 сдвига. Информационный вход регистра 4 сдвига подключен к выходу коммутатора 29, второй и третий входы которого соединены соответственно с выходом регистра 4 сдвига и с выхо дом регистра 8 сдвига. Выход регистра 5 сдвига подключен к третьему входу коммутатора 26, выход которого соединен с информационным входом регистра 6 сдвига. Информационный вход регистра 7 сдвига подключей к выходу коммутатора 24, первьй и третий входы которого соединены соответственно с входом 44 абсолютной величины вычислителя и с выходом регистра 7 сдвига. Информационный вход регистра 8 сдвига подключен к выходу коммутатора 28, второй и третий входы которого соединены соответственно с выходом регистра 4 сдвига и с выходом регистра 8 сдвига. Информационньй вход регистра 1 сдвига подключен к вьпсоду сумматора 9, первый и второй входы которого сое динены соответственно с выходом комму татора 18 и с выходом формирователя 10 дополнительного кода, первый и вто рой входы которого подключены соответственно к выходу элемента И 16 и к первому выходу блока 12 формирования знака, третья группа входов которого соединена с первой группой выходов блока 13 синхронизации.

Второй и первый входы формирователя 1 1 дополнительного кода соединены соответственно с выходом элемента 15 задержки и с вторым выходом блока 12 формирования знака, второй и первый входы которого подключены соответственно к входу 43 знака входной информации вычислителя и к выходу сумматора 9.

Выход формирователя 11 дополнительного кода соединен с первыми входами коммутаторов 22 и 23.

Блок 13 синхронизации соединен. седьмым входом с третьим входом коммутатора 19,восьмым выходом - с первым входом коммутатора 20,четвертым выходом - с вторыми входами коммутаторов 18 и 23 и с первым входом коммутатора 21, вторым выходом - с первым входом элемента И 17, выход которого подключен к первому входу триггера 14. Второй

мента ИЛИ 40. Первые входы первого п-го элементов групп элементов И 34 и 35 соединены соответственно с выходами первого h -го разрядов распределителя 42 импульсов. Вторые входы групп 34 и 35 элементов И соединены соответственно с выходом формирователя 11 дополнительного ковход и прямой выход триггера 14 соединены соответственно с третьим выходом блока 13 синхронизации и с первым входом элемента И 16, второй вход которого подключен к выходу коммутатора 29. Выход коммутатора 23 подключен KI первому входу коммутатора 25, выход и третий вход которого соединены соответственно с информационным входом и выходом регистра 5 сдвига. Выход регистра 6 сдвига подключен к третьему входу коммутатора 23, к первому входу коммутатора 26 и к первому входу коммутатора 27, выход и третий входы которого соединены соответственно с третьим входом коммутатора 20 и с выходом регистра 7 сдвига. Третий вход коммутатора 21 подключен к выходу коммутатора 22, второй вход которого соединен с входом 44 абсолютной величины вычислителя. Девятый выход блока 13 синхронизации подключен к вторым входам коммутаторов 24 и 27 и к третьему входу коммутатора 22. Пятый выход блока 13 синхронизации соединен с вторыми входами коммутаторов 25 и 26. Шестой выход блока 13 синхронизации соединен с первыми входами коммутаторов 28 и 29. Четвертый выход блока 13 синхронизации соединен с входом h -разрядного распределителя 42 импульсов, выходы которого соединены через группу элементов И 41 и с входами эледа и вторым вькодом блока 12 формирования знака. Выход элемента ИЛИ 4 соединен с первым входом элемента И 36, второй вход которого соединен с выходом элемента 15 задержки. Выход элемента И 36 соединен с первым входом сумматора 31, второй вход которого соединен с выходом регистра 30 сдвига и первым входом формирователя 32 дополнительного кода. Выход сумматора 31 соединен с информационным входом регистра 30 сдвига и первым входом элемента И 37, выход которого соединен с первым входом триггера 33. Третий выход блока 13 синхронизации соединен с вторыми входами элемента И 37 и триггера 33 прямой выход которого соединен с первым входом элемента И 38 и с вторым входом формирователя 32 дополнительного кода, выход которого соединен с первым входом элемента И 39. Девятый выход блока 13 синхронизации соединен с вторыми входами элементов И 38 и 39, выходы которых являются соответственно выходами общего знака 45 и преобразования вычислителя 46, выходы 47 частного преобразования с первого по п -и порядок и выходы 48 знака частных преобразоваНИИ которого соединены соответственно с выходами групп элементов И 34 и 35. Входы синхронизации регистров 1-8 и 30 сдвига соединены с входом синхронизации элемента 15 задержки и с десятым выходом блока 13 синхронизации, одиннадцатый выход которого соединен с входами управления регист ров 1, .4, 5, 7, 8 и 30 сдвига. Двенадцатый выход блока 13 синхронизации соединен с входами сброса сумматоров 9 и 31 формирователей 10, 11 и 32 дополнительного кода. Блок 12 формирования знака (фиг.2 содержит три регистра 49-51 сдвига, три коммутатора 52-54, распределител 55 импульсов, элемент ИСКПЮЧАЩЕЕ ИЛИ 56, входы 43 и 57, выходы 58 и 5 Блок 13 синхронизации содержит генератор 60 тактовых сигналов, распределитель 61 импульсов, элемент 62 задержки, счетчик 63, делитель 64 частоты, S-триггер 65, дешифратор 66, генератор 67 одиночных импульсов коммутатор 68 и выходы 69-79. Вход 43 знака входной информации вычислителя подключен к информацион ному входу двухразрядного регистра 49 сдвига, шина сдвига которого coe-f динена с выходом делителя 64 частоты. Информационный вход регистра 50 сдвига, содержащего п + 1 разряд, соединен с шиной 57 с выходом сумматора 9. Выход регистра 51 сдвига емкостью в п разрядов соединен со своим информационным входом и с первым входом элемента 56 ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к вы- .ходу коммутлтора 52, Выходы первых разрядов регистров 49 и 50 сдвига соединены с первым и вторым входами коммутаторов 53 соответственно. Выходы второго разряда регистра 49 сдвига и h + 1-го разряда регистра 50 сдвига соединены с первым и вторым входами коммутатора 52 соответственно. Первый, второй и третий входы коммутатора 54 соединены соответственно с выходом коммутатора 53, с выходом п-го разряда регистра 50 сдвига и с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 56. Вход распределителя 55 импульсов соединен с выходом элемента 62 задержки. Три управляющих входа KOMhfyTaTOра 54 соединены с соответствующими тремя выходами распределителя 55 импульсов. Выход коммутатора 54 подключен к вы: одной шине 58, которая является первым выходом блока 12 формирования знака. Выход первого разряда регистра 50 сдвига соединен с выходной шиной 59, которая является вторым выходом бло- ка 12 формирования знака. Входы упавления вводом информации регистров 49-51 сдвига соединены с выходом генератора 67 одиночных импульсов. Выход генератора 60 тактовых сигалов блока 13 синхронизации подклюен к шине 77 и к входу п -разрядно го распределителя 61 импульсов, выод h -го разряда которого соединен входом элемента 62 задержки, с ервым входом триггера 65 и с выход ой шиной 70. Выход первого разряда аспределителя 61 импульсов соединен с шиной 69. Выход элемента 62 задержки соеди ен с входом счетчика 63 и с выходной шиной 79. Выход переполнения четчика 63, имеющего коэффициент пеерасчета Зи, соединен с входом деителя 64 частоты и с шинами однига регистров 50 и 51 сдвига блока 12 формирования 3Haka. Выход делителя 6А частоты, имеющего коэффициент деления h , соединен с вторым входом триггера 65, прямой выход которого подключен к выходной шине 76 и к третьим входам коммутаторов 52 и 53 блока 12 формирования знака. Выходы триггеров счетчика 63 подключены к входам дешифратора 66, выходы которого соединены с выходными шинами 71-75.блока 13 синхронизации. Выход делителя 64 частоты соединен с тактовым входом генератора 67 одиночных импульсов, выход которого сое динен с шиной 78, а вход запуска через коммутатор 68 - с нулевой шиной вычислителя. Выходные шины 69-79 являются вторым - двенадцатым выходами блока 13 синхронизации соответственно. Интегро-дифференциальный вычислитель реализует в цифровой форме пере даточную функцию h -и степени вида W(P) n Wp{P) , (1) гдеШ(Р) - передаточная функция г звена интегро-дифференциального преобразования реализуемого из п звеньев. Каждое Р-е звено с интегро-дифференциальным преобразйванием IVg(P) интегро-дифференциальный вычислитель реализует согласно рекуррентному соотношению;,-.., ( где V. -и Yj. значения выходной величины для t-ro звена интегро-дифференциального преобразования на .1 -м и ( - 1)-м шагах вычислений соответственно i значения входной величины для 6-го звена интегро-дифференциального преобразования на 1 -м и ( 1 1)-м шагах вычислений соответственно постоянные коэффицив в и Со енты, от значения которых зависит вид интегрот-дифференциаЛьного преобразования Wj(P) согласно таблице. Заданное интегро-дифференциапьное преобразование высокого порядка представляется согласно выражению (1) в виде произведения Г) элементарных интегро-дифференциальных звеньев We(Р), дпя каждого из которых производят предварительный расчет постоянных коэффициентов А, В«, Cj по формулам табл. 1, где К - коэффициент усиления, Т, Т, Tj - постоянные времениj - шаг последовательного преобразования входной величины в выходную, который выбирается из условия заданной точности. Все звенья интегро-дифференциапьного преобразования на каждом шаге вычислений обрабатываются последовательно с первого до последнего. Входной величиной для каждого звена интегро-дифференциального преобразования, кроме первого, является выходная величина предьщущего звена, т.е «., У Y г,- е-1и-1 V Jj Интегро-дифференциальньй вычислитель оперирует с двоичными переменными, для которых соотношение (2) принимает вид У.:Е2(/1А..6Л (Л.Х rp.H.... ь где Y, -двоичная переменная 2,i-i,j j-ro разряда величины Хр . . . и X. .:. -двоичные переменные t.-j ,ij J-X разрядов величин Х . i соответственно;h - количество звеньев (вида WX) согласно таблице/, входящих в интегро-дифференциальное преобразование, равное количеству разрядов представления двоичных переменных. Интегро-дифференциальный вычислитель дополнительно формирует на каждом шаге вычислений выходную величину сложного интегро-дифференциального преобразования согласно выражениюz. (л„ . (5) где Z - значения выходной величины сложного интегро-дифференциального преобразования на 1 -м шаге, . - значения выходной величины для -го звена интегро-дифференциалъного преобразования i-го порядка на t-м шаге; бр - заданная переключательная переменная, которая принимает значение О либо 1. Начальная установка регистров 1, 4, 5, 7, 8 и 30 сдвига осуществляется либо от цифровой вычислительной машины, либо от устройств автоматического ввода информации по одиночному импульсу, вырабатываемому на. одиннадцатом выходе блока 13 синхронизации. Начальная ус тановка регистров 2, 3 и 6 выполняется путем ввода информации через коммутаторы 20, 21 и 26 от регистров 7, 1 и 5 сдвига соответственно. Начальное расположение информации в регистрах 1-8 сдвига соответствует расположению информации в конце некоторого ( i - 1)-го шага вычислений. Если двоичные коды коэффициентов AJ, Вр и Cj, а также начальные усло вия входной величины и выходных вели чин всех звеньев интегро-дифференциального преобразования постоянны и не могут измениться в процессе использования интегро-дифференциального вычислителя, то шины ввода информации в соответствующие разряды регистров 1-8 и 30 сдвига могут быть постоянно соединены с шинами логического нуля или едини.цы вычислителя в зависимости от значения вводимого кода. Интегро-дифференциальный вычислитель работает циклическим образом, выполняя последовательно интегродифференциальное образование над двоичным кодом входного сигнала согласно выражению (4). В конце ( - 1)-го шага вычислений в регистре 1 сдвига на п. - 1 раз ряд, который дополняется элементом 15 задержки на такт до ,п -разрядов, содержится п-разрядный двоичный код выходной величины , вычисленной на ( 1 - 1)-м шаге. В регистре 8 11 512 сдвига емкостью в 3( п - О слов, каждое из которых содержит п двоичных разрядов, записаны последовательно двоичные коды коэффициентов Aj, Bj, Cj , где f. 1, 2, ..., h - 1 обозначает порядковый номер звена интегродифференциального преобразования. В регистре 4 сдвига емкостью в три слова по п разрядов каждое записаны двоичные коды коэффициентов Aj, Вр, Cf, последнего по порядку п-го звена интегро-дифференциального преобразова ия. В регистре 5 сдвига емкостью в И - 1 слово по п разрядов каждое содержатся двоичные коды абсолютных значений выходных величин звеньев интегро-дифференциального преобразования с первого по п- 1, вычисленные на предьцтущем ( - 1)-м шаге вычислений. В регистре 6 сдвига емкостью в одно слово на и разрядов содержится выходная величина последнего h-го звена интегро-дифференциального преобразования. Регистр 2 сдвига на и - 1 разряд и регистр 3 сдвига на 2п разрядов обеспечивают в процессе вычислений хранение двоичных кодов X .., , Е,1-1 .i Б регистре 7 сдвига на п разрядов хранится абсолютное значение входной величины Х интегро-дифференциального вычислителя от предыдущего шага вычислений, знак которой хранится в блоке 12 формирования знака. Каждый шаг вычислений начинается в момент генерации на девятом выходе блока 13 синхронизации управляющего сигнала длительностью в п тактов, который переключает коммутаторы 22, 24 и 27. Одновременно на восьмом выходе блока 13 синхронизации вырабатывается управляющий сигнал длительностью 2п тактов, действующий на коммутатор 20, а на четвертом выходе блока 13 синхронизации вырабатывается управляющий -сигнал длительностью h тактов, действующий на коммутаторы 18, 21 и 23. На шестом выходе блока 13 синхронизации в это время формируется управляющий сигнал длительностью в Зп тактов, который переключает коммутаторы 28 и 29. Вход 44 абсолютной величины вычислителя подключается коммутаторами 2 и 22 к информационному входу реистра 3 сдвига и коммутатором 24 к информационному входу регистра 7 сдвига, выход которого коммутаторами 20 и 27 подключается к информационно му входу регистра 2 сдвига. Двоичньй код абсолютной величины входного сиг нала на 4-м шаге вычислений, поступающий последовательно во в земени, начиная с младших разрядов, по входу 44 абсолютной величины вычислителя записывается под действием импуль сов десятого выхода блока 13 синхронизации за п тактов в регистр 3 сдвига, емкость которого составляет 2tl разрядов. Одновременно с этим двоичный код абсолютной величины входного сигнала на предыдущем (i - 1)-м шаге вычислений, который хранится в регистре 7 сдвига, переписывается под действием импульсов десятого выхода блока 13 синхронизации с выхода регистра 7 сдвига через коммутаторы 27 и 20 в регистр 2 сдвига, имеющий емкость в п- 1 раз ряд. По мере освобождения старших ра рядов регистра 7 сдвига в них записывается через коммутатор 24 двоичный код входного сигнала на i -м шаге, действующий на входе 44 абсолютной величины вычислителя. Сигнал, поступающий по входу 43 знака входной информации вычислителя, записьгоается в блок 12 формирования знака. Коммутатор 18 разрывает на ti тактов цепь циркуляции двоичного кода регистра 1 сдвига через сумматор 9. Коммутаторы 23 и 25 подключают выход формирователя 11 дополнительного кода к информационному входу регистра 5 сдвига, выход которого подключается коммутатором 26 к информацион ному входу регистра 6 сдвига емкость в п разрядов. Прямой или дополнительный код выходной величины интегро-дифференциального вычислителя на ( i - 1)-м шаге сдвигается с выхода регистра 1 сдвига через элемент 15 задержки, формирователь 11 дополнительного кода и коммутаторы 23 и 25 в регистр 5 сдвига, с выхода которого в это время сдвигается двоичный код абсолю ного значения выходной величины пер вого звена интегро-дифференциального преобразования на ( - 1)-м шаге вычислений. Формирователь 11 дополни тельного кода по сигналам второго выхода блока 12 формирования знака преобразует дополнительный код регис ра 1 сдвига в прямой код, прямой код регистра 1 сдвига пропускает без изменения. Таким образом, в регистр. 5 сдвига записывается прямой код абсолютного значения выходной величины интегро-дифференциального преобразования п -го порядка. Если с выхода регистра 7 сдвига сдвигается в младшем разряде входной величины на (i - 1)-м шаге единичный сигнал, который через коммутаторы 20 и 27 поступает на второй вход элемента И 17, то сигнал второго выхода блока 13 синхронизации поступает через элемент И 17 на первый вход триггера 14, который переходит из нулевого состояния в единичное. В этом случае на прямом выходе триггера 14 формируется сигнал, который открывает элемент И 16. В это время с выхода регистра 8 сдвига сдвигается, начиная с младших разрядов, двоичный код коэффициента А, который записывается через коммутатор 29 в регистр 4 сдвига и через элемент И 16, формирователь 10 дополнительного кода и сумматор 9 в регистр 1 сдвига. Формирователь 10 дополнительного кода управляется сигналом первого выхода блока 12 формирования знака так, что при положительном знаке произведения AJ Х двоичный код коэффициента А. проходит без изменения, а при отрицательном знаке преобразуется в до полнит ел ь-ньй код. Спустя гг тактов после начала вычислений на i-м шаге на четвертом и девятом выходах блока 13 синхронизации начинают действовать сигналы управления, которые переводят коммутаторы 18, 21, 23 и 24,22, 27 соответственно в исходное положение. В этом случае коммутатор 18 подключает выход коммутатора 19 к первому входу сумматора 9, коммутатор 21 подключает выход регистра 2 сдвига к входу регистра 3 сдвига, коммутатор 23 подключает выход регистра 6 сдвига к первому входу коммутатора 25, коммутатор 22 подключает выход формирователя 11 дополнительного кода к третьему входу коммутатора 21, коммутатор 24 подключает выход регистра 7 сдвига к его информационному входу, коммутатор 27 подключает выход регистра 6 сдвига к третьему входу коммутатора 20. После этого вькодной сигнал первого звена на (li - 1)-м шаге сдвигается с выхода регистра 6 сдвига через коммутаторы 27 и 20 в регистр 2 сдвига, с выхода которого через коммутатор 21 в регцстр 3 сдвигается И - 1 разряд двоичного кода входной величины на (i - 1)-м шаге. Если в младшем разряде двоичного кода Y - содержится единичный код, то единичный сигнал с выхода регистра 6 сдвига через коммутаторы 27 и 20 поступает на второй элемента И 17, на первом входе которого действует сигнал второго выхода блока 13 синхронизации. В этом случае триггер 14 устанавливает ся в единичное состояние выходным сигналом элемента И 17. Если в младшем разряде величины ;-т содержит ся нулевой код, то триггер 14 устанавливается в нулевое состояние налом третьего выхода блока 13 синхр низации. При единичном состоянии триггера 14 сигнал его прямого выход открывает элемент И 16. Двоичный код коэффициента В сдвигается с выхода регистра 8 сдвига через коммута тор 29 в регистр 4 сдвига, а также через элемент И 16 и формирователь 10 дополнительного кода на второй ,вход сумматора 9, на первый вход которого в это время с выхода регистра 1 сдвига через элемент 15 задержки и коммутаторы 18 и 19 сдвигается

двоичный код коэффициента А. Результат суммирования коэффициентов А, В записывается с выхода сумматора 9 с

в регистр 1 сдвига. Формирователь 10 дополнительного кода в это время управляется сигналом знака произведения , действующим на первом выходе блока 12 формирования знака. Спустя 2 h тактов после начала . вычислений на i-м шаге на восьмом выходе блока 13 синхронизации формируется управляюш;ий сигнал, которьй возвращает коммутатор 20 в исходное состояние. Коммутатор 20 подключает выход регистра 3 сдвига к информационному входу регистра 2 сдвига, . выход которого подключен коммутатором 21 к информационному входу регисра 3 сдвига. В результате этого регистры 2 и 3 сдвига объедин1потся в кольцевой регистр сдвига на 3h - 1 разряд.

В момент объединения регистров 2 и 3 сдвига с выхода регистра 3 сдайга сдвигается, начиная с мпадших раз110си г-

тов А

и В. Результат суммирова(А, В + С) записывается с выния

1

хода сумматора 9 в регистр 1 сдвига. Таким образом, спустя Зп тактов после начала вычислений в регистре сдвига фopмиpyetcя двоичньй код суммы произведений первых разрядов величин

i

двоичные ко-

на В

С соответ-

ентов А

1

1

Двоичные коды коэффициентов А

1

В

, С последовательно переписываются под действием импульсов десятого выхода блока 13 синхронизации с выхода регистра 8 сдвига через коммутатор 29 в регистр 4 сдвига, с выхода которого двоичные коды коэффициентов А, В, С переписьгеаются через коммутатор 28 в регистр 8 сдвига.

В кольцевом регистре сдвига, образованном объединением регистров 2 и 3 сдвига, емкостью в 3 п - 1 разряд за Зп тактов происходит сдвиг на один разряд так, что с сигналами второго выхода блока 13 синхронизации, деист16рядов двоичный код входной величины Х- на i -м шаге. Если в младшем разряде величины Vj содержится единичный код, то единичный сигнал с выхода регистра 3 сдвига через коммутатор 20 поступает на первый вход элемента И 17, открывая его. Сигнал второго выхода блока 13 синхронизации проходит через элемент И 17, устанавливая триггер 14 в единичное состояние. Если в мла,гуием разряде величины Х содержится нулевой код, то триггер 14 сбрасывается в нулевое состояние сигналом третьего выхода блока 13 синхронизации. В случае единичного состояния триггера 14 сигнал его прямого выхода открывает элемент И 16. В это время с выхода регистра 8 сдвига через коммутатор 29 сдвигается двоичный код коэффициента С, который записывается в регистр 4 сдвига и через элемент И 16, формирователь 10 допол нительного кода поступает на второй сумматора .9. Формирователь 10 вход дополнительного кода в это время управляет сигналами произведения С Х , действующим на первом выходе, блока 12 формирования знака. Одновременно на первый вход сумматора 9 с выхода регистра 1 сдвига сдвигается через элемент 15 задержки и коммутаторы 18 и 19 двоичный код суммы коэффициен,вукяцими на первом входе элемента И 17, совпадают сигналы;вторых разря дов величин Х. , , Спустя Зп тактов после начала вычислений на седьмом и шестом выходах блока 13 синхронизации формируются сигналы управления, которые при водят к переключению коммутаторов 19 28 и 29 соответственно. Коммутатор 19 подключает пыход регистра 1 сдвига через коммутатор 18 к первому вхо ду сумматора 9. Этим обеспечивается сдвиг в регистре 1 двоичного кода накопленной суммы коэффициентов Ал, , С на один разряд или умножение этой суммы на два. Коммутатор 28 подключает выход ре гистра 8 сдвига к его информационному входу, а коммутатор 29 подключает выход регистра 4 сдвига к своему входу. В результате этого в регистре 4 сдвига запоминаются двоичные коды коэффициентов А, В, С, а в регист ре 8 сдвига - двоичные коды коэффици ентов А, Bg, Cj, где , 3, ...,л Спустя п тактов после переключения коммутатора 19 на седьмом выходе блока 13 синхронизации формируется сигнал управления, который возвращает коммутатор 19 в исходное состояние. Цепь циркуляции кодов в регистре 1 сдвига вновь замыкается через элемент 15 задержки, коммутаторы 18 и 19 и сумматор 9. В течение 3 ti тактов после начала вычислений интегро-дифференциальный вычислитель работает так же, как и на первых Зп Тактах работы. В регистре 1 сдвига накапливаются п стар тих разрядов суммы произведений величин , , Y и Х на двоичные коды коэффициентов А, В, С соответственно. Согласно соотношению (4) ЭТОТ результат соответствует выход ной величине Y . первого звена интег ро-дифференциального преобразования на -м шаге вычислений. Спустя 2 гт тактов после начала вычислений на пятом выходе блока 13 синхронизации формируется на время п( h - 1) тактов сигнал управления, который приводит к переключению коммутаторов 25 и 26. Если до переключения коммутаторы 25 и 26 объединяли регистры 5 и 6 сдвига в кольцевой регистр на П слов по п разрядов в каждом, то после переключения коммутаторов 25 11 18 и 26 вькод регистра 5 сдвига соединяется с его входом через коммутатор 25, а выход регистра 6 сдвига подключается к своему входу через коммутатор 26. После этого в регистре 5 сдвига емкостью в п - 1 слово по п разрядов каждое осуществляется хранение последовательности величин YPJ.-I , где f 1, 2, ..., h - 1, а в регистре 6 сдвига запоминается веСпустя (п - 1)1 такличина Y тов после переключения коммутаторов 25 и 26 на пятом выходе блока 13 синхронизации формируется сигнал управления, возвращающий коммутаторы 25 и 26 в исходное состояние. В этом случае выход регистра 6 сдвига подключается через коммутаторы 23 и 25 к входу регистра 5 сдвига, выход которого соединяется через коммутатор 26 к входу регистра 6 сдвига. Регистры 5 и 6 сдвига вновь объединяются в кольцевой регистр сдвига на h слов по п разрядов в каждом. Таким образом осуществляется сдвиг последовательности величин Yf ..j , где t 1, 2, ...м , на одно слово в кольцевом регистре сдвига, образованном регистрами 5 и 6. Спустя 3 п 2 после начала вычислений на ( i - 1)-м щаге или к моменту начала вычислений для второго звена интегро-дифференциального преобразования в регистре 5 сдвига содержится последовательность величин Y j.-| Уэ,1-1 . Yf, 5 , а в регистре 6 сдвига - величина .. Во время первых п тактов вычислений для второго звена интегро-дифференциального преобразования на f-м шаге на восьмом и четвертом выходах блока 13 синхронизации формируются сигналы управления, которые переключают коммутаторы 20, 18, 21, 23 соответственно. Импульсный сигнал четвертого выхода блока 13 синхронизации поступает на вход п -разрядного распределителя 42 импульсов, на первом выходе которого начинает действовать импульс, открывающий первые элементы И 34 и 35. Двоичный код абсолютного значения выходной величины интегро-дифференциапьного преобразования первого порядка сдвигается с выхода регистра 1 сдвига через элемент 15 задержки, формирователь 11 дополнительного кода и первый элемент И 34 на первую выходную шину 47 частотного преобразования интегро-дифференциал ного вычислителя. Знак выходной величины интегро-дифференциального пр образования первого порядка поступа ет с второго выхода блока 12 формирования знака через первый элемент И 35 на первую выходную шину А8 знака частного преобразования интегродифференциального вычислителя. Двоичный код выходной величины Yi первого звена интегро-дифференциального преобразования также сдвигается с выхода регистра 1 сдвига через элемент 15 задержки, формирователь 11 дополнительного кода, коммутаторы 23 и 25 в регистр 5 сдвига с выхода которого последовательност величин 2,,-- . э,1-1 . Yn,i-i 1-,, сдвигается в регистр 6 сдвига. Кроме этоого, величина Y сдвигается с выхода регистра 1 сдвига через элемент 15 задержки, формирова тель 11 дополнительного кода, коммутаторы 21 и 22 в реИистр 3 сдвига в качестве входного сигнала Xj для второго звена интегро-дифференциального преобразования. Величина Y в это время сдвигается с выход регистра 6 сдвига через коммутаторы 27 и 20 в регистр 2 сдвига в качестве входного сигнала Х -, для второго звена интегродифференциального преобразования. В последующие г тактов с выхода регистра 6 сдвига сдвигается двоичный код величины Yj i-i который через коммутаторы 27 и 20 записывается в регистр 2 сдвига. Таким образом, в кольцевой регистр сдвига, образованный объединением регистров 2 и 3, записьтаются начальные условия Xj,,---, , i.-i ,4 необходимые для выполнения вычислений для второго звена интегро-дифференциального преобразования. В первые 3rj тактов вычислений для второго звена интегро-диффереяциального преобразования на шестом выходе блока 13 синхронизации формируется сигнал управления, который переключает коммутаторы 28 и 29, В этом случае с выхода регистра 8 сдвига через коммутатор 29 сдвигаются в регистр 4 сдвига двоичные коды коэффициентов Aj, Bj и С для второг звейа интегро-дифференциального преобразования, а двоичные коды коэффи1520 циентов А, В, С с выхода регистра 4 сдвига сдвигаются через коммутатор 28 на вход регистра 8 сдвига. Спустя Зп тактов коммутаторы 28 и 29 возвращаются в исходное состояние. Поэтому во время вычислений для второго звена интегро-дифференциаль- ного преобразования в регистре 4 сдвига хранятся коэффициенты А, Bj, Cj, а в регистре 8 сдвига - коэффициенты А, В , С,з э 3 А,, В4, С А, В1, С. Таким образом, в регистры 2, 3 4 сдвига записываются двоичные коды начальных условий и коэффициентов, необходимые для выполнения вычислений второго звена интегро-дифференциального преобразования, которые вьтолняются аналогично вычислениям для первого звена интегро-дифференциального преобразования. После окончания вычислений интегро-дифференциального преобразования второго порядка на четвертом выходе блока 13 синхронизации вьфабатывается импульс, который проходит на выход второго разряда распределителя 42 импульсов и на первые входы вторых элементов И 34 и 35. С выхода регистра 1 сдвига через элемент 15 задержки, формирователь 11 дополнительного кода и второй элемент И 34 на вторую выходную гаину 47 частного преобразования интегро-дифференциаль- ного вычислителя сдвигается двоичный код абсолютного значения fYj|} выходной величины интегро-дифференциального преобразования второго порядка. Одновременно с второго выхода блока 12 формирования знака через второй элемент И 35 на вторую выходную шину 48 знака частного преобразования поступает знак выходной велины интегро-дифференциального преобразования второго порядка. Вычисления для всех последующих звеньев интегро-дифференциального преобразования до h -го звена включи- тельно выполняются аналогичным образом. Вычисления на ( i + 1)-м шаге вычислений и всех последующих для всех h звеньев интегро-дифференциального преобразования осуществляются анало гично. Одновременно с интегро-дифференциальными преобразованиями от первого до . порядка интегро-дифференциальный вычислитель формирует согла но выражению (5) величину сложного интегро-дифференциального преобразования. С помощью группы элементов И 41 задают переключательные функции 6«, которые определяют функцию и вид сложного интегро-дифференциального преобразования. Группа элементов И 4 подключает выход первого разряда рас пределителя 42 импульсов к первому входу элемента ИЛИ 40, если выходная величина интегро-диФФеренциапьного преобразования первого порядка входит в состав сложного интегро-дифференциального преобразования, т.е. 6| 1. Аналогично, выход f-ro разря да распределителя импульсов подключается элементом И группы 41 к соответствующему f-му входу элемента ИЛИ 40, если выходная величина интег ро-дифференциального преобразования -го порядка входит в состав сложного интегро-дифференциального преобразования, т.е. 6g 1. На выходе элемента ИЛИ 40 формируется управляю щий сигнал, который открывает элемен И 36 во время сдвига с выхода регист ра 1 сдвига выходных величин Y g , звеньев интегро-дифференциального преобразования, соответствующих заданным переключательным переменным (ag 1, 1, 2, ...,п . Двоичный код выходной величины Ye: заданного /J t-ro звена интегро-дифференциального преобразования под действием импульсов десятого выхода блока 13 синхронизации сдвигается с выхода регистра 1 сдвига через элемент 15 задержки, элемент И 36 и сумматор 31 на информационный вход Г1-разрядного регистр 30 сдвига и записывается в него, начиная с младшего разряда. Двоичный код выходной величины р4-1 следующего заданного, например Ct + )-то интегро-дифференциального преобразования, поступая аналогичным образом на вход сумматора 31, суммируется с двоичным кодом величины Yf v который сдвигается с выхода регистра 30 сдвига, и записывается под действием импульсов десятого выхода блока 13 синхронизации вновь в регистр 30 сдвига, где формируется двоичный код выходной величины 2- сложного интег ро-дифференциального преобразования на i-м шаге вычисления. ( После каждого 1 -го шага вычислений в течение h тактов следующего (i 1)-го шага вычислений интегродифференциальный вычислитель выдает на выходах 45 и 46 соответственно двоичный код абсолютной величины и сигнал знака сложного интегро-дифференциального преобразования (5). Если величина Z,- отрицательна, то в регистре 30 сдвига записан дополниjтельный двоичный код, единичный сигнал знака которого в п -м такте i-го шага вычислений с выхода сумматора 31 поступает через элемент И 37 на вход триггера 33, устанавливая его в единичное состояние. Единичный сигнал триггера 33 открывает элемент И 38, через который на выход 45 с девятого выхода блока 13 синхронизации поступает единичный сигнал отрицательного знака величины Zj сложного интегро-дифференциального преобразования. Дополнительный двоичный код величины Z , сдвигаемый с выхода регистра 30 сдвига, преобразуется формирователем 32 дополнительного кода в прямой код абсолютной величины |Z) сложного интегро-дифференциального преобразования (5) и вьщается через элемент И 39 на выход 46 в виде последовательного двоичного кода. Если величина 2- положительна, то триггер 33 сохраняет нулевое состояние, а формирователь 32 дополнительного кода пропускает без изменения прямой двоичный код регистра 30 сдвига на выход 46 интегро-дифферен циального вычислителя. В этом случае элемент И 38 закрыт нулевым сигналом прямого выхода триггера 33 и на выходе 45 действует нулевой сигнал положительного знака величины Z,- . Блок 12 формирования знака и блок 13 синхронизации работают в процессе вычислений следующим образом. Знак входной величины Xj.-i -содержится в первом разряде двухразрядногс регистра 49 сдвига блока 12 формирования знака. Знак выходных величин звеньев интегро-дифференциального преобразования с первого по п й содержится в регистре 50 сдвига на п 1 разряд блока 12 формирования . Знаки коэффициентов XJ € Г, , ..., и , содержится в регистре 1 сдвига блока 12 формирования знака Знаки коэффициентов Bj и Се, 2- 1, 2, ..., п , всегда положительны и не требуют предварительной, установки. Генератор 60 тактовых сигналов блока 13 синхронизации вьфабатывает последовательность импульсов частоты f, которая делится распределителем 61 импульсов на п раз и затем задерживается элементом 62 задержки на длительность тактового импульса. Пос ледовательность импульсов частоты /п на вьсходе п -го разряда распределителя 61 импульсов (шина 70 треть го выхода блока 13 синхронизации) определяет ti -е такты работы интегро дифференциального вычислителя, а последовательность импульсов частоты f/n на выходе первого разряда распределителя 61 импульсов (шина 69 второго выхода блока 13 синхронизации) задает первые такты работы. Счетчик 63 выполняет деление на 3ti частоты выходной последовательно ти импульсов элемента 62 задержки. Выходная последовательность импульсов счетчика 63 частоты f /3fi дели ся на п раз делителем 64 частоты, на выходе которого Лормируется после довательность импульсов частоты /3 h, период следования которых определяет один шаг вычислений. С помощью дешифратора 66, входы которого подключены к выходам триггеров счетчика 63, формируются пять последовательностей импульсов заданной длительности и периода следования, которые необходимы для управления работой интегро-дифференциального вычислителя (шины 71-75 четвертого - восьмого выходов блока 13 синхронизации соответственно). Каждый шаг вычислений в интегродифференциальном вычислителе начинае ся в момент генерации импульсов на выходе делителя 64 частоты блока 13 синхронизации, который устанавливает триггер 65 в единичное состояние и сдвигает на один разряд информацию о знаке входной величины в регистре 49 сдвига блока 12 формирования знака. В результате сдвига в , первый разряд регистра 49 записывается знак входной величины на текущем Ч-м шаге, сигнал которого действует на шине входа 43 знака входной информацрш вычислителя, а знак входной величины на предьщущем ( i - 1)-м шаге сдвигается из первого разряда во второй разряд регистра 49 сдвига. На прямом выходе триггера 65 (шина 76 девятого выхода блока 13 синхро низации) формируется сигнал, который 11 с помощью коммутаторов 52 и 53 подключает выходы регистра 49 или 50 сдвига к входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 56 и коммутатора 54 соответственно. Коммутатор 54 по сигналам трехканального распределителя 55 импульсов опрашивает последовательно через каждые ,М тактов выходы элемента ИСКЛЮЧАЮР1ЕЕ ИЛИ 56, регистра 50 сдвига и коммутатора 53. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 56, входы которого подключены к выходу рёгист- ра 51 сдвига и через коммутатор 52 к выходам регистров 49 и 50 сдвига, формируется сигнал знака произведения или AgXg, e(1,i-i f 2, 3, ...,п , На выходе п -го разряда регистра 50 сдвига формируется сигнал знака произведения BpYg., 1 1,2, п, а на выходе коммутатора 53 - сиг- нал знака произведения С Xj itti.1 ii(i4L iij-v ri ji t.-i -jiri/i -4 -4 mi И Се e,i cg Yg. , e 2, 3, . . . , П . Таким образом, на выходе коммута- тора 54 (шина 58 первого выхода блока 12 формирования знака) каждые п тактов последовательно во временидействуют на сигналы знаков произведений Af Xg,., и CjXf , , - 1, 2, ...,ht На выходной шине 59 второго выхода блока 12 формирования знака действует сигнал выхода первого разряда регистра 50 сдвига, в который с выхода сумматора 9 по шине 57 записывается п -и знаковый разряд выходных величин V( , где € 1, 2, ...,П всех звеньев интегро-дифференциаль ного преобразования. Выходная последовательность импульсов генератора 60 тактовых сигналов, действующая на шине 77 десятого выхода блока 13 синхронизации, осуществляет синхронизацию сдвига информации в регистрах 1-8 и 30 сдвига, Одиночньш импульс на шине 78 одиннадцатого выхода блока 13 синхронизации формируется генератором 67 одиночных импульсов, запуск которого осуществляется коммутатором 68, вьтол- ненным, например, в виде кнопочного переключателя. Последовательность импульсов, действующая на шине 79 двенадцатого выхода блока 13 синхронизации через каждые п тактов, поступает на входы сброса сумматоров 9 и 31, а также |юрмирователей 10, 11 и 32 дополни25

тельного кода, выполняя сброс триггеров, которые могут быть использованы при реализации этих блоков.

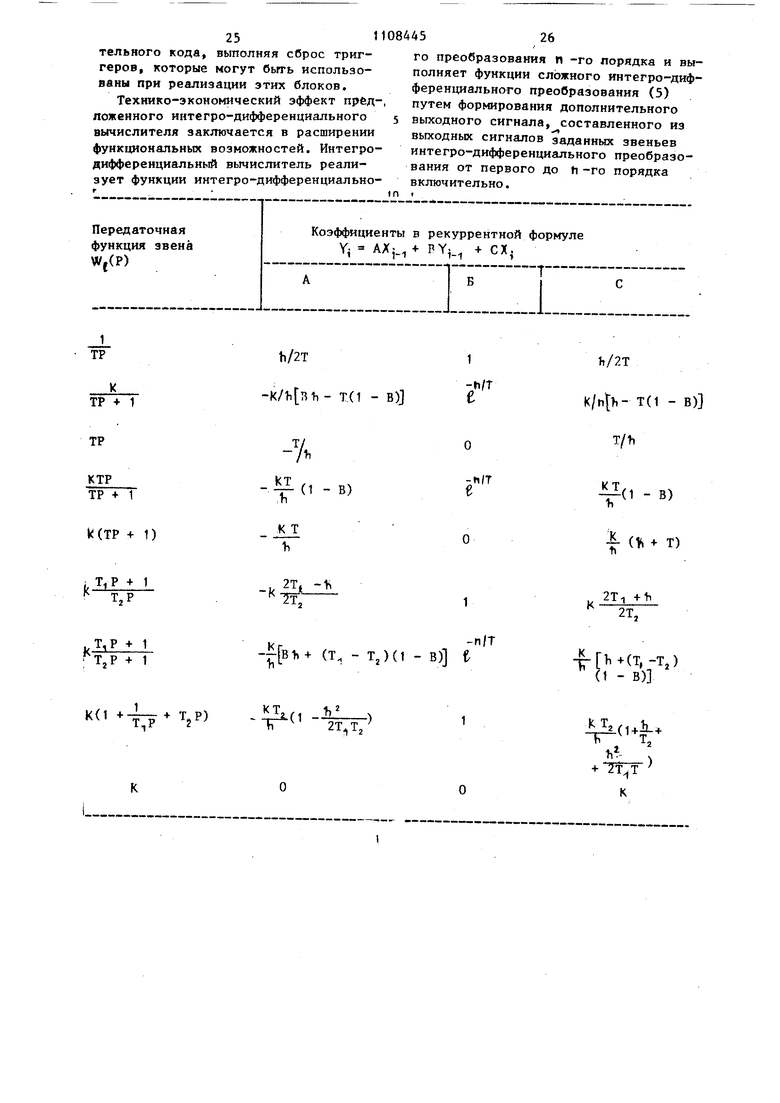

Технико-экономический эффект предложенного интегро-дифференциального вычислителя заключается в расширении функциональных возможностей. Интегродифференциальный вычислитель реализует функции интегро-дифференциальноh/2T Т.(1 - B)J ТР + 1 КТР (1 - В) ТР + 1 k(TP -4- 1)

. 2Т, --Ь

1

1/ ,

ж Т,Р + 1 (т, - Tj){i + 1

КТ

-т;р Vi

108445

26

го преобразования п -го порядка и выполняет функции сложного интегро-дифференциального преобразования (5) путем формирования дополнительного 5 выходного сигнала, составленного из выходных сигналов Заданных звеньев интегро-дифференциального преобразования от первого до ti -го порядка

включительно.

n I

2Ti + 2Т,

(иЬ-+

hf ;

+ 1 -h/T К/ф- т(1 - в) 6 (1 - в) I- (У, + Т) , В) е

Фиг.О. 5S

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU955051A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1983-03-25—Подача