:.- ,,. . ,. , 1

изобретение относится к автоматике и вычислительной технике и предназначено для возведения в квадрат двоичных чисел или последовательности импульсов.

Известен квадратор , содержащий счетчик-регистр, счетный вход которого через элемент задержки подключен к входной шине, а его выходы поразрядно через ключи подключены ко входам накапливающего сумматора, вход ключей соединен с входной шиной, а вход накапливакщего сумматора соединен со счетным входом счетчикагрегистра р/|,

Недостаток такого квадратора заключается в росте аппаратурных затрат пропорционально разрядности счетчикарегистра и накапливающего сумматора, что усложняет его устройство при значительном количестве разрядов.

Наиболее близким техническим решением к предлагаемому является квадратор, содержащий сумматор, первый

вход которого соединен и ш ходом первого элемента ИЛИ, а второй вход и выход соответственно - с выходом н входом первого регистра сдвига, первый и второй входы первого элемента ИЛИ соединены соответственно с прямЕЛМ выходом второго регистра сдвига и со входом первого элемента задержки.

Кроме того, устройство содержит два счетчика и блок умножения 2 .

Недостатком этого устройства является его относительная сложность.

Цель изобретения - упрощение устройства.

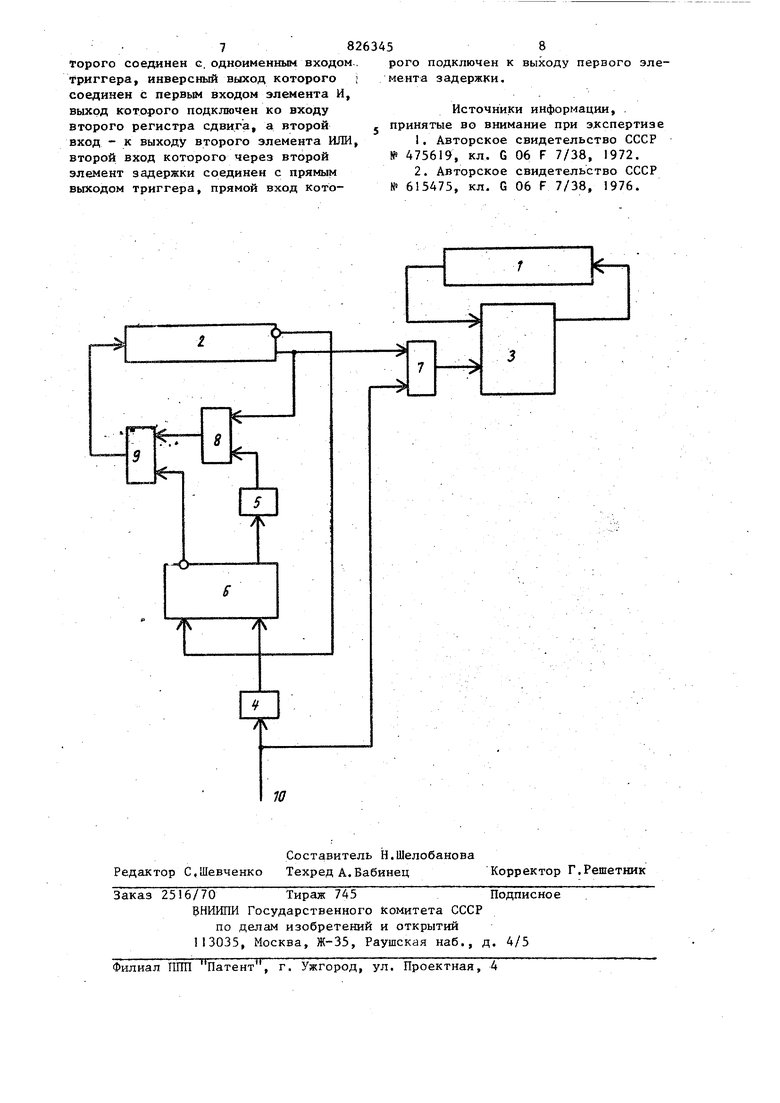

Поставленная цель достигается тем, что в квадратор, содержащий сумматор, первый вход которого соединен с выxoдo первого элемента ИЛИ, а второй вход и.выход соответственно с выходом и входом первого регистра сдвига, первый и второй входы первого элемента ИЛИ соединены соответственно с прямым выходом второго ре гистра сдвига и со входом первого элемента задержки, вход которого является входом квадратора, второй эле мент задержки, введены триггер, элемент И и второй элемент ИЛИ, первый вход которого подключен к прямому выходу второго регистра сдвига, инверсный выход которого соединен с одноименньи входом триггера, инверсный выход которого соединен с первым входом элемента И, выход которого подключен ко входу второго регист ра сдвига, а второй вход - к выходу второго элемента ИЛИ, второй вход которого через второй элемент задерж ки соединен с прямым выходом триггера,прямой вход которого подключен к выходу первого элемента задержки. На чертеже изображена структурна схема квадратора. Квадратор содержит два регистра 1 и 2 сдвига, сумматора 3, два элемента 4 и5 задержки,триггер 6,два эле мента ИЛИ 7 и 8, элемент И 9 и вход 10 устройства. Квадратор реализует соотношение xt-- 1,(I) + 2х4, 1 - J$1H 1, 2, 3,... - Si ЛХ: - входные приращения на i-oM шаге вычисления; - значенияаргумента на i-о и (i - l)-oM шагах вы числений соответственно; х- - значения квадратичной функции на i-оми -i - )шагах вычислений соотв ственно. В исходном состоянии регистры 1 и 2 сдвига очищены, так как х. 1 XQ О, а триггер 6 находится в нуле вом состоянии, так как на его инверс ном входе действует единичный сигнал инверсного выхода регистра 2 сдвига. На вход 10 квадратора подается по следовательность импульсовлх , которая представляет собой например, поток выходных приращений цифрового дифференциального анализатора, Йервый входной импульсдх поступает через элемент ИЛИ 7 на второй вход последовательно однорядного сум матора 3, на первый вход которого по следовательно, начиная с младших рязрядов, считывается двоичный код начального значения квадратичной фун кции XJ О, В результате суммирования сумматором 3 образуется значение квадратичной функции на первом шаге S 1, которое с выхода вычислений сумматора 3 .записывается в нпадший разряд регистра 1 сдвига. Спустя время задержки элементом 4, равное длительности действия входного импульса, первый входной импульс поступает на прямой вход триггера 6 и устанавливает его в единичное состояние, при котором на его инверсном выходе устанавливается нулевой сигнал, закрывающий по первому входу элемент И 9, а на прямом выходе - едидиничный сигнал. Единичный сигнал с прямого выхода триггера 6, спустя время задержки элементом 5, равное длительности входного импульса, начи- . нает действовать по второму входу элемента ИЛИ 8 и поддерживает на выходе элемента ИЛИ 8 и втором входе элемента И 9 единичный сигнал, Таким образом, к моменту считывания с выходов регистров I и 2 сдвига вторых разрядов начальных двоичных кодов О и Хо О соответственно триггер 6 находится в единичном состоянии, на первом входе элемента И 9 действует нулевой сигнал, а на его втором входе - единичный сигнал. Поскольку во втором разряде начального двоичного кода Хо О с выхода регистра сдвига 2 считывается нулевой код, то на его инверсном выходе появляется импульсный сигнал, который поступает на инверсный вход триггера 6 и возвращает его в нулевое состояние, открывая по первому входу элемент И 9. Из-за задержки на длительность импульса элементом 5 единичного сигнала прямого выхода триггера 6 его предыдущего состояния, на вторых входах элементов ИЛИ 8 и И 9 действует также единичный сигнал на время длительности импульса, В результате на выходе элемента И 9 сформировывается импульсный сигнал, который записывается во второй разряд регистра 2 сдвига. Следующие разряды с выхода регистра 2 сдвига на его вход переписываются без изменения, так как на втором входе элемента ИЛИ 8 устанавливается нулевой сигнал прямого выхода триггера 6, а элемент И 9 открыт по первому входу единичным сигналом инверсного выхода триггера 6, В это время содержимое разрядов регистра I сдвига, начиная со второго, не изменяется, так как с прямого выхода регистра 2 сдвига считываются нулевые Сигналы на второй вход элемента ИЛИ 7, на первом входе которого также отсутствуют сигналы ввиду окончания действия входиого импульса АХ на вход 10.

Таким образом, после первого шага вычислений в регистре 1 сдвига сформировывается последовательный двоичный код результата х 1, а в регистре 2 сдвига - двоичный код удвоенного значения аргумента 2х; 2.

Второй входной импульс приращения Ах2 поступает с входа 10 на первый вход элемента ИЖ 7, на второй вход которого поступает двоичный код удво-енного значения аргумента на предыдущем шаге вычислений 2х 2. Навыходе элемента ИЛИ 7 сформируется двоичный код 011 (три), который поступает на второй вход сумматора J.

Учитывая, что в первом разряде ДВОИЧНОГО кода удвоенного значения аргумента 2 . всегда содержится нулевой код, поступаюдий на второй вход элемента ИЛИ 7 а на его первом вхо- де в первом разряде в каждом шаге вычислений действует входной импyльc то элемент ИЛИ 7 выполняет функции формирования двоичного кода 2 х.- 1

Двоичный код 2 х. I с выхода элемента ИЛИ 7 суммируется сумматором 3 с последовательным двоичным кодом , считываемым с выхода регистра I сдвига и результат х записывается с выхода сумматора 3 в регистр 1 сдвига.

На втором шаге на выходе элемента ИЛИ 7 действует двоичный код 011 (три который суммируется с двоичным кодом предыдущего значения квадратичной функции 001 (один), считываемого с выхода регистра 1 сдвига. В результате суммирования сумматором 3 на втором шаге вычислений сформируется двоичный код 100 (четыре), который записывается в регистр сдвига 1.

Одновременно с процессом вычислекия квадратичной функции сумматором 3 в регистре 2 сдвига формируется удвоенное значение аргумента 2 х .

На втором шаге вычислений второй входной импульс, действующий по входу 10 спустя время задержки элементом 4, установит 1риггер 6 в единичное состояние, при котором на первом

входе элемента И 9 действует нулевой сигнал инверсного выхода триггера 6. Элемент И 9 закрывается и в младшие разряды регистра 2 сдвига записываются нулевые коды до тех пор, пока триггер 6 не вернется в нулевое состояние, в которое его возвращает первый, начиная со второго разряда, нулевой код регистра 2 сдвига.

На втором шаге вычислений с выхода регистра 2 сдвига считывается двоичный код 010 (два). Перв, начиная со второго разряда, нулевой код содержится в третьем разряде регистра 2 сдвига, который привода1т к формированию на его инверсном выходе единичного сигнала, возвращающего триггер 6 в нулевое состояние.

Возврат триггера 6 в нулевое состояние приводит к формированию импульса на выходе элемента И 9, благодаря задержке элементом 5 еди 01чного сигнала прямого выхода триггера 6 его предьщущего состояния. В результате иа втором шаге вычислений в первые два разряда регистра 2 сдвига записывается нулевой код, а в третий разряд --единичный код, что дает двоичный код 100 (четыре).

Вычисления на последующих шагах выполняются согласно алгоритму (1) аналогичным образом.

Технико-экономические преимущества предлагаемого квадратора по сравнению с известным заключаююя в упрощении устройства при сохранении высокой точности вычислеш1Й.

Формула изобретения

Квадратор, содержащий сумматор, первый вход которого соединен с выходом первого элемента ИЛИ, & второй вход и выход соответственно - с выходом и входом первого регистра сдви га, первый и второй входы первого элемента ИЛИ соединены соответственно с прямым выходом второго регистра сдвига и со входом первого элемента задержки, вход которого является входом квадратора-, второй элемент задержки, отличающийся тем, что, с целью упрощения, он содержит триггер, элемент И и злемент ИЛИ, первый вход которого подключен к прямому выходу второго регистра сдвига, инверсный выход ко

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1987 |

|

SU1501049A1 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

| Устройство для возведения в куб | 1979 |

|

SU868755A1 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

| Вычислительное устройство | 1983 |

|

SU1144105A2 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

Авторы

Даты

1981-04-30—Публикация

1979-04-27—Подача