Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано при разработке микросхем памяти с резервированием.

Цель изобретения - расширение функциональных возможностей запоминающего устройства с резервированием путем увеличения его разрядности

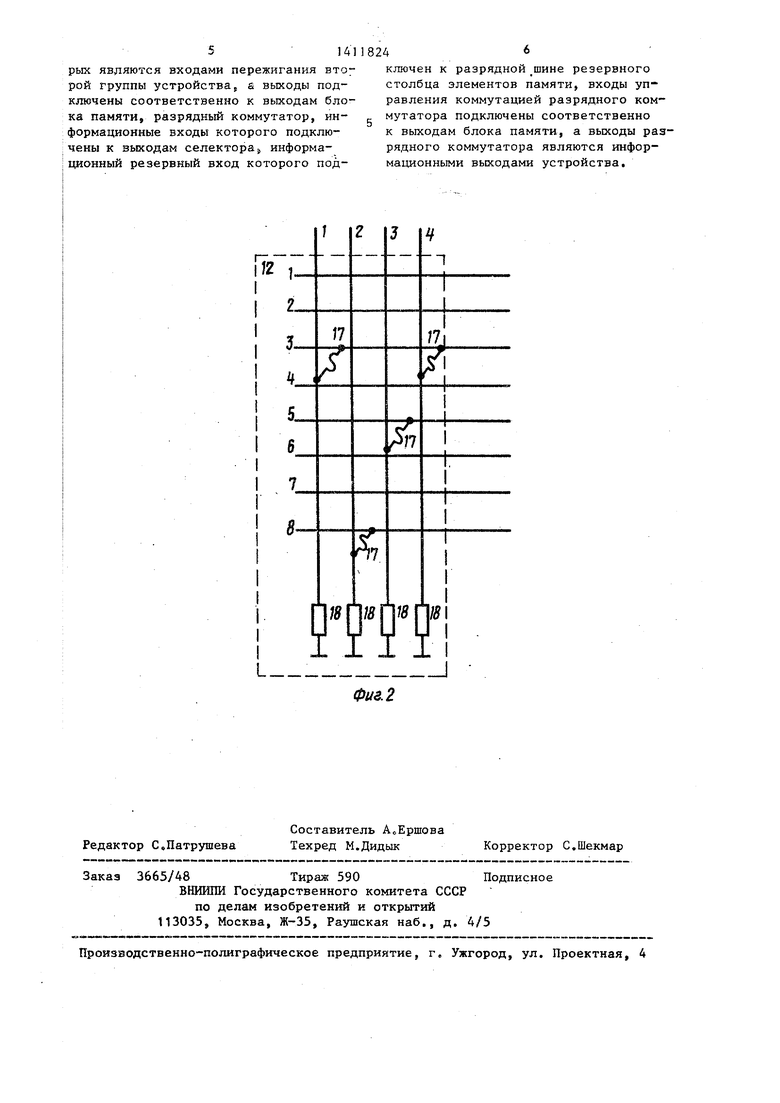

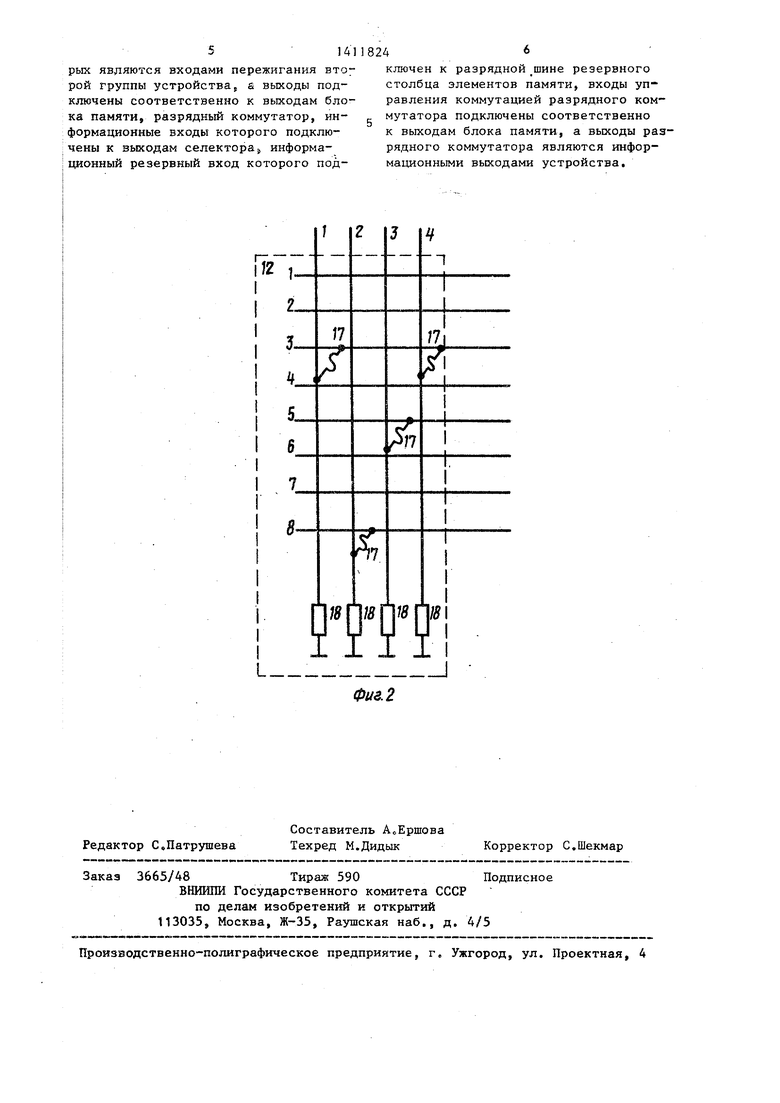

На фиг.) представлена блок-схема ° запоминающего устройства с резервированием; на фиг о 2 - блок памяти.

Устройство содержит накопитель 1, разбитый на секции 2, число которых равно разрядности устройства, резервный столбец 3 элементов памяти, разбитый на несколько частей 4, дешифратор 5 слов, дешифратор 6 разрядов, три преобразователя адресных сигна- лов 7о1-7.3, селектор 8, дешифратор 9 резервных разрядов, первая, вторая группы формирователей 10 и 11 напряжения пережигания, блок 12 памяти, третья группа формирователей 13 нап ряжения пережигания, разрядный коммутатор 14 из ключевых элементов 15 и 16 на транзисторах, блок 12 памяти представляет программируемзпо логическую матрицу (ПЛМ) на плавких встав- ках 17 с элементами 18 смещения на резисторах,

Функционирование устройства может быть рассмотрено;, например, при его восьмиразрядной организации и разбиении резервного столбца 3 на четыре части 4, Каждая часть 4 столбца 3 может заменить соответствующую часть столбца любой из секций 2 накопителя 1. Количество формирователей 10 и П равно числу частей 4, на которые разбит столбец 3, а количество формирователей 13 равно разрядности устрой- ства. Количество преобразователей ад pecHbtx сигналов адреса первой группы равно количеству разрядов адреса, необходимых для выбора одной из частей 4 столбца 3, т,е. в данном случае преобразователей 7 адресных сигналов первой группы,

Дефектные элементы памяти располагаются в первой и четвертой частях третьей секции 2 накопителя 1, в третьей части пятой секции 2 и во второй части восьмой секции 2, Запис адресов неисправных элементов памяти в дешифратор 9 и блок 2 производится следующим образом. На микросхему подается повьш1енное напряжение пита

5 0 5 О

Q Q

5

5

ния. На адресные входы преобразователей 7.,3 первой и третьей групп подается код адреса той части столбца, в которой находится первый неисправный элемент памяти. Разряды адресов, поступающие на входы преобразо- вателей второй группы в данном режиме работы могут быть произвольными, так как они определяют расположение неисправного элемента памяти в части столбца, поэтому они могут быть объединены с входами формирователей 10. С выходов преобразователей 7 адрес поступает на входы дешифратора 9, При появлении на первом входе формирователей 10 разрешающего сигнала на его первом выходе формируется высокое напряжение пережигающее плавкие перемычки в первом разряде дешифратора 9 в соответствии с поступившим на него адресом. Таким образом, происходит запись адреса части столбца, в которой находится первый неисправный элемент памяти. Аналогично проводитт ся запись адресов и всех остальных частей в соответствии с информацией, поступающей на адресные входы преобразователей 7 первой и третьей групп и формирователей 10,

Устройство многоразрядно, поэтому каждая часть столбца, адрес которой хранится в дешифраторе 9, может находиться по данному адресу в любой из секций 2 накопителя I„ Для установления соответствия между храни- адресами и секциями служит блок 12-, Запись информации в него производится после того, как произведена запись в дешифратор 9 и формирователи 10 отключены. Формирователи 11 необходимы для обеспечения- тока,пережигающего перемычки 17, Для определения секции, в которой находится первый неисправный элемент памяти, на адресные входы подается код его адресов, а на входы формирователей 13, кроме соответствующего данной секции, подается низкое напряжение, разрешающее пережигание. Дешифратор 9 в соответствии с адресом выбирает первый из формирователей 11, который подает на первую строку матрицы 12 высокое напряжение, В результате в первой строке сгорают все перемычки 11, кроме третьей. Аналогичным образом пережигаются перемычки 15 в остальных строках матрицы 12

этого устройство готово к раПослеботе.

В рабочем режиме на устройство подается номинальное напряжение питания. При таком напряжении питания формирователи 10 и 13 отключаются, и на работу устройства влияния не оказывают.

В режиме выборки на адресные входы поступает код адреса выбираемого слова, в соответствии с которым дешифратор 5 выбирает адресную шину Информация из выбранных элементов памяти поступает в разрядные шины всех столбцов, в том числе и резервного Селектор 8 пропускает на свои выходы информацию только с тех разрядных шин накопителя 1, код адреса которых поступил на входы дешифратора б. Одновременно часть разрядов поступает на дешифратор 9,, При совпадении поступившего адреса с одним из адресов, хранящемся в. нем, он дает сигнал на соответствующий формирователь 11. Формирователь -ITчерез плавкую перемычку 17 повышает напряжение на соответствующем входе коммутатора 14. В данном разряде коммутатора закрывается транзистор 15, коллектор которого подключен к одному из выходов селектора 8, и открывается транзистор 16,подключенный к разрядной шине резервного столбца 3 На входах всех остальных разрядов коммутатора 14 остается низкое напряжение, устанавливаемое элементами 18. Таким образом, при поступлении на адресные входы адреса неисправного элемента памяти произойдет его замена на элемент памяти из резервного столбца 3 в том разряде, в котором неисправный элемент расположен. Коммутатор 14 передает информацию на выход устройства.

Если на адресные входы поступает адрес элемента памяти, не находящийся ни в одной из частей столбцов накопителя 1 совместно с неисправным элементом, то этот адрес не совпада- зт ни с одним из адресов, записанных в дешифраторе 9. В этом случае все выходы дешифратора 9 вьщают напряжение невыборки о В коммутаторе 14 открыты все транзисторы 15 и закрыты все транзисторы 16 На выход проходит информадая только из селектора 8 В предложенной схеме запоминающего

0

5

0

5

0

5

0

5

0

5

устройства с резервированием используется только один резервный столбец для замены одиночных неисправностей, расположенных в разных секциях многоразрядного накопителя, Это позволяет избежать больших затрат площади, занимаемой резервными элементами на кристалле, и повысить выход годных при наличии одиночных неисправностей, возникающих в накопителе о

Формула изобретения

Запоминающее устройство с резервированием, содержащее накопитель, резервный столбец элементов памяти, дешифратор слов, дешифратор разрядов, три преобразователя адресных сигна- лов, информационные входы которых

являются адресными входами устройства, селектор,информационные входы которого подключены к соответствующим разрядным шинам накопителя, адресные шины которого подключены к соответствующим адресным входам резервного столбца элементов памяти и выходам дешифратора слов, входы которого подключены соответственно к выходам первого и второго преобразователей адресных сигналов, выходы третьего преобразователя адресных сигналов подключены соответственно к входам дешифратора разрядов, выходы которого подключены соответственно к входам управления коммутацией селектора, дешифратор резервных разрядов, входы которого подключены соответственно к выходам первого и третьего преобра зователей адресных сигналов, первую группу формирователей напряжения пережигания, выходы которых подключены соответственно к выходам дешифратора резервных разрядов, а входы являются входами пережигания первой группы устройства, отличакзщее- с я тем, что, с целью расширения функциональных возможностей устройства путем увеличения его разрядности, в него введены вторая группа формирователей напряжения пережигания, входы которых соединены с выходами дешифратора резервных разрядов, блок памяти, входы которого подключены соответственно к выходам второй группы формирователей напряжения пережигания, третья группа формирователей напряжения пережигания, входы кото514

рых являются входами пережигания второй группы устройства 5 s выходы подключены соответственно к выходам блока памяти, разрядный коммутатор, информационные входы которого подключены к выходам селектораJ информационный резервный вход которого под18246

ключей к разрядной шине резервного столбца элементов памяти, входы управления коммутацией разрядного коммутатора подключены соответственно к выходам блока памяти, а выходы разрядного коммутатора являются информационными выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1988 |

|

SU1596393A1 |

| Программируемый дешифратор | 1986 |

|

SU1399816A1 |

| Дешифратор | 1988 |

|

SU1594605A1 |

| Дешифратор | 1986 |

|

SU1399817A1 |

| Адресный формирователь | 1988 |

|

SU1596389A1 |

| Адресный формирователь | 1988 |

|

SU1596388A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1439684A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Оперативное запоминающее устройство с резервированием строк | 1986 |

|

SU1462426A1 |

| Программируемое постоянное запоминающее устройство | 1988 |

|

SU1635218A1 |

Изобретение относится к вычисли- /-тельной технике, а именно к запоминающим устройствам и может быть использовано при разработке микросхем памяти с резервированием. Цель изобретения - расширение функциональных возможностей запоминающего устройства путем увеличения его разрядности. Это достигается тем, что устройство дополнительно содержит второй и третий формирователи 11,13 напряжения пережигания, программируемую матрицу 12, коммутатор 14 с соответствующими связями. Программирование матрицы 12 устанавливает соответствие между адресом неисправного элемента памяти и разрядом устройства, В соответствии с этой информацией коммутатор 14 осуществляет замену информации, поступающей из неисправного элемента, на информацию из реверв- ног о элемента памяти. 2 ил. о 9 (Л

L.I

Фиг. 2

| Зарубежная электронная техника, 1985, № 10, 0.22, рис.П | |||

| Патент США № 4047163, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1988-07-23—Публикация

1987-01-04—Подача